Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as uneven distribution of impurities in the P-well region, different turn-on voltage, and affecting the electrical characteristics of the device, so as to achieve optimal electrical properties. Characteristics and reliability, optimized uniformity, effects of reducing adverse defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0032] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

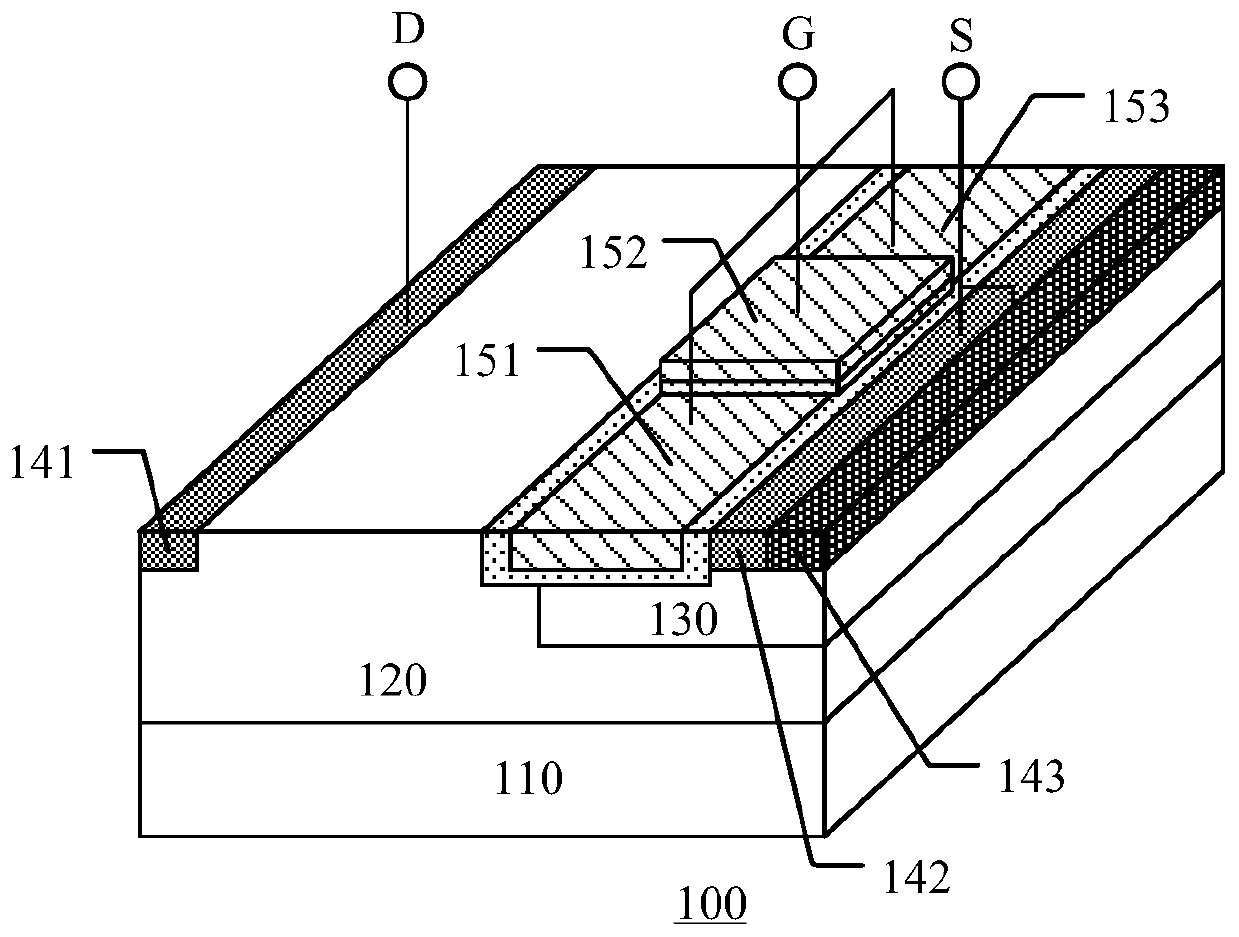

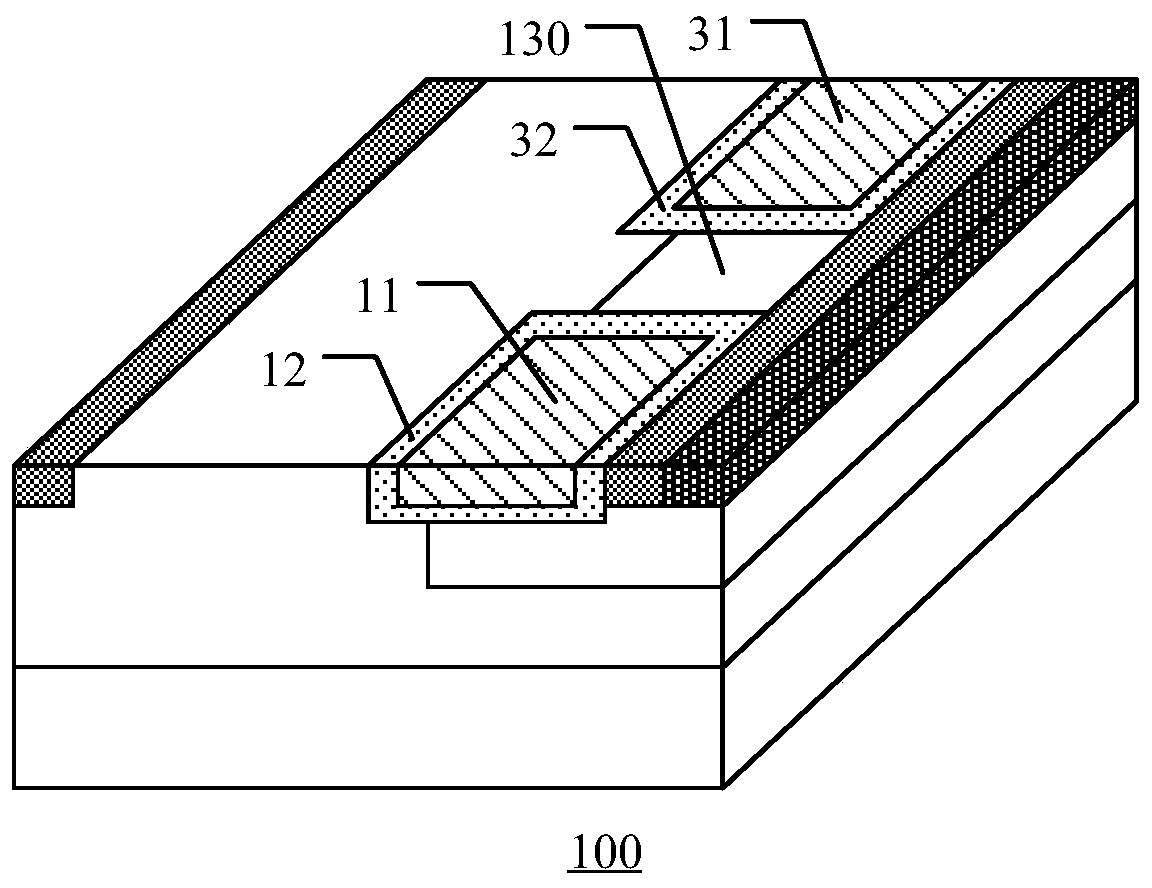

[0033] figure 1 shows a schematic structural diagram of a tri-gate LDMOS device according to the prior art, figure 2 shows the basis figure 1 A partial structural schematic diagram of the tri-gate LDMOS device. combine figure 1 and figure 2 , a triple-gate LDMOS device 100 in the prior art includes a P substrate 110, an N drift region 120, a P well region 130, an N+ doped region 141, an N+ doped region 142, a P+ doped region 143, a first gate region 151 , the second gate region 152 and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More