Masking template, static random access storage unit and storage

A technology of static random access and storage unit, which is applied in the direction of electrical components, electric solid-state devices, semiconductor devices, etc. It can solve problems such as chamfering and affecting device performance, and achieve the effect of simple production and avoiding mismatching problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

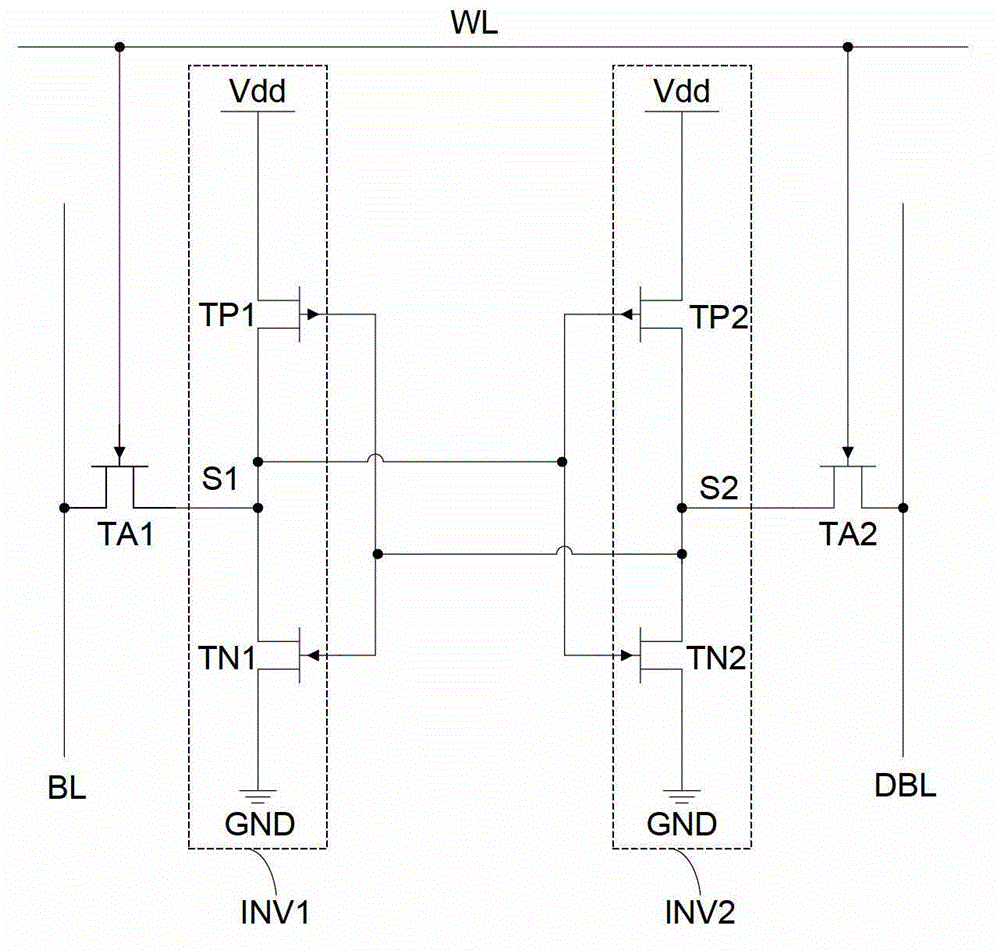

[0036] In order to ensure the normal operation of the storage unit of the SRAM in the existing technology, the size of the access NMOS transistor in the storage unit must be larger than that of the driving NMOS transistor to obtain a β value (beta ratio).

[0037]The larger the size difference between the two, the larger the beta ratio; and the larger the beta ratio value, the higher the stability of the storage unit.

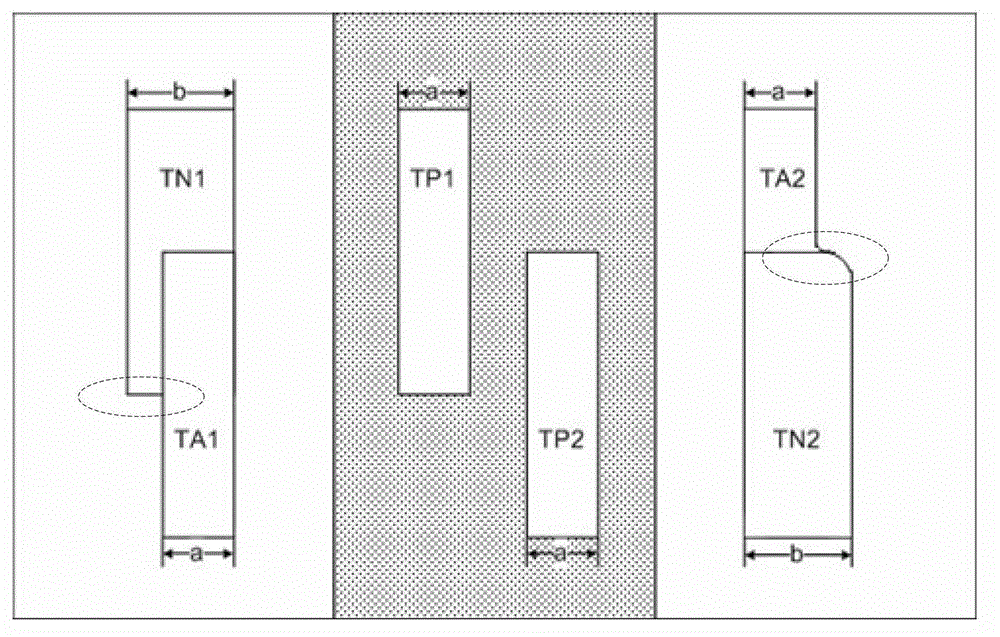

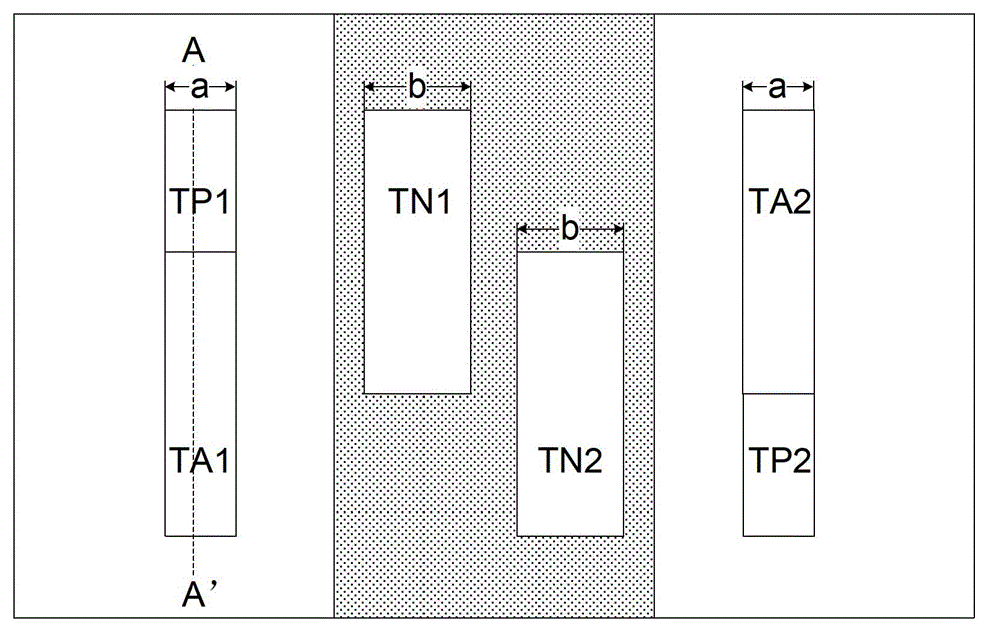

[0038] figure 2 is a schematic top view of a conventional reticle with static random access memory cell patterns. Such as figure 2 As shown, the first load PMOS transistor TP1 pattern, the first access NMOS transistor TA1 pattern, the second load PMOS transistor TP2 pattern, and the second access NMOS transistor TA2 pattern have the same first critical dimension a. The pattern of the first driving NMOS transistor TN1 and the pattern of the second driving NMOS transistor TN2 have the same second critical dimension b. In order to obtain the above betaratio, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More