BE-SONOS (bandgap engineered-SONOS) structural device with low compile voltage and trapping charge and forming method of BE-SONOS structural device

A BE-SONOS and voltage technology, applied in the field of microelectronics, can solve problems affecting device performance, erasure cannot be performed, etc., and achieve the effect of reducing capture and suppressing unstable factors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

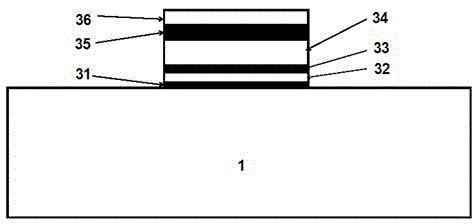

[0023] The process of forming a BE-SONOS structure device with low compilation voltage trapping charges is as follows:

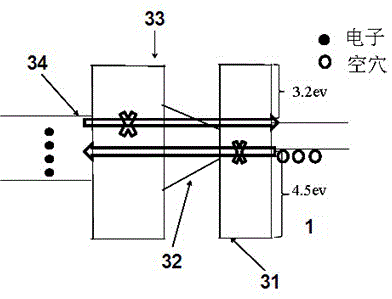

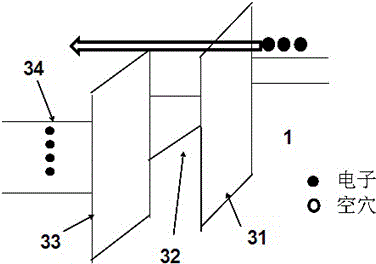

[0024] First prepare a thin silicon oxide layer 31 (referred to as O1) with a thickness of 1.5 nm on the P-type silicon substrate 1, and then prepare a layer of nitrogen-rich nitrogen with a thickness of 2.0 nm on the silicon oxide layer 31. Silicon nitride layer 32 (denoted as rich-N1), the Si / N concentration in the formed silicon nitride layer is 0.1. Then another silicon oxynitride layer 33 (referred to as SiON) with a thickness of 2.5 nm is prepared on the nitrogen-rich silicon nitride layer 32 (rich-N1). Then prepare a layer of 7nm thick silicon nitride layer 34 (denoted as N2) with charge storage capability on the silicon oxynitride layer 33, and thermally oxidize a layer of 9nm thick blocking oxide layer 35 on the layer of charge storage nitride layer (denoted as O3), and finally a polysilicon control gate 36 is prepared on the blocking oxide layer (...

Embodiment 2

[0029] This example is slightly different from Example 1. By adjusting the thickness ratio of nitrogen-rich silicon nitride and N1, the N1 layer with a thickness of 2-t nm in the original BE-SONOS is replaced with a layer of t nm-rich silicon nitride with a thickness of t nm. Nitrogenated silicon nitride layer 32 .

[0030] The obvious erasing speed is due to the fact that the hole barrier (<1.9eV) at the interface between silicon and silicon nitride is smaller than that at the interface between silicon and silicon oxide (4.6eV). At high field, this large barrier difference for holes can produce a large energy band shift under electric field, so that holes only tunnel quickly through the O1 layer.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More