Semiconductor device structure and fabrication method of semiconductor device structure

A technology of device structure and manufacturing method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of large reverse breakdown voltage, affecting device characteristics, and insufficient current handling capacity of devices, so as to improve the endurance Effect of current surge capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

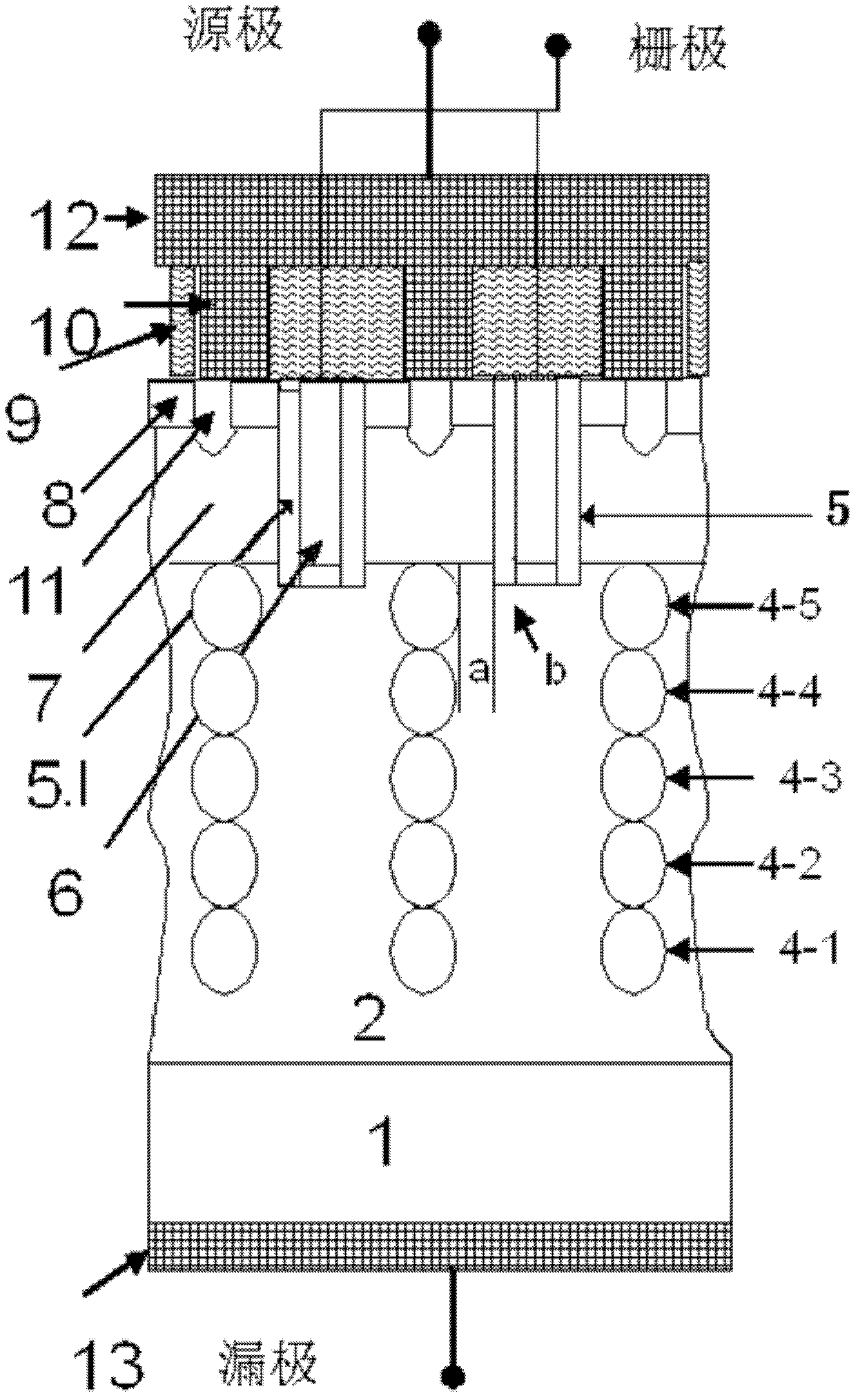

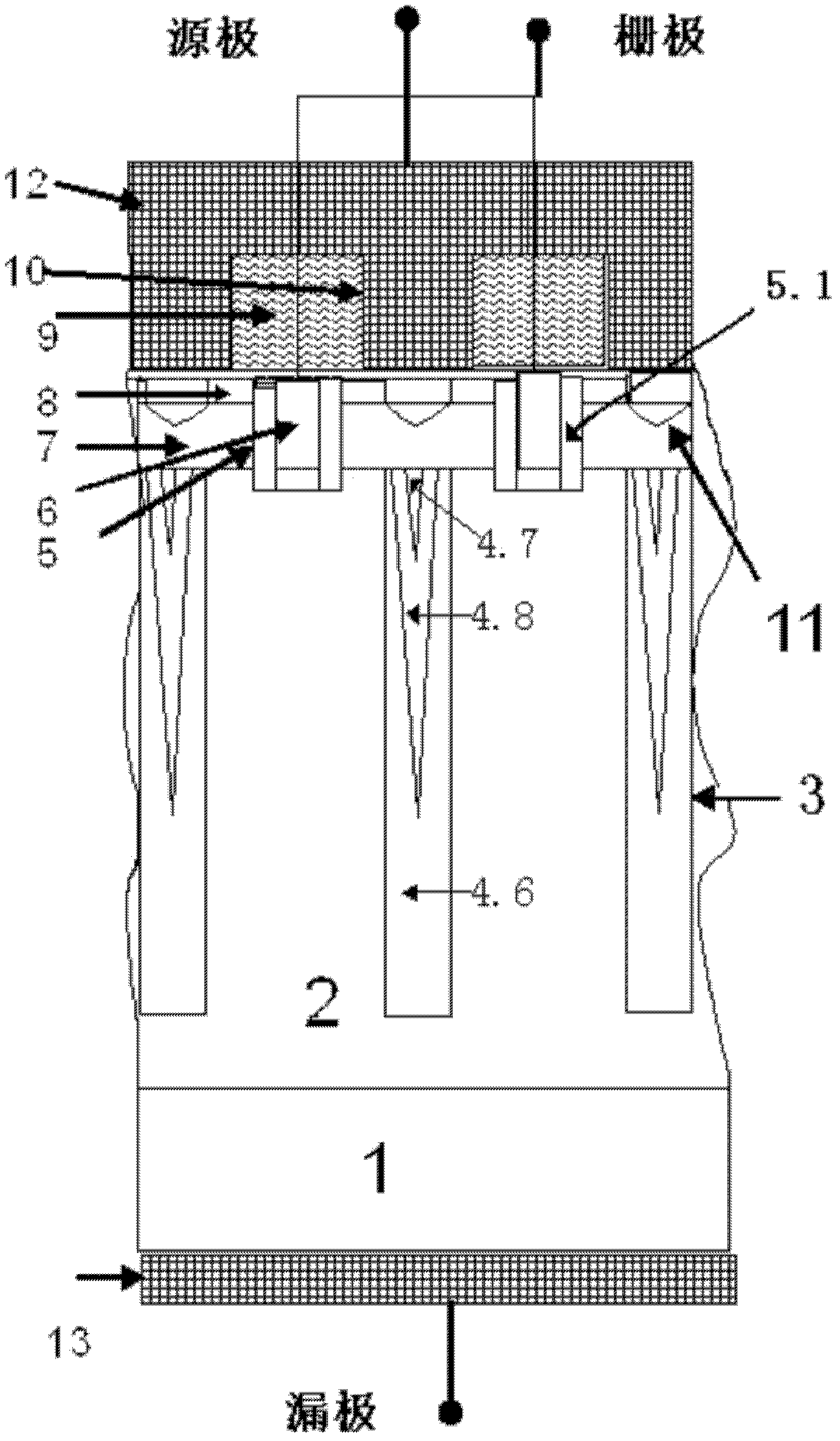

[0058] Such as figure 2 As shown, the device with a reverse breakdown voltage of 600V is an embodiment of the present invention, and the resistivity of the N+ substrate used is 0.001 ohm to 0.003 ohm. The widths of the P film and the N film are 4 microns and 8 microns in turn. N-type silicon is uniformly doped, and its doping concentration is 3E15 / CM3. In order to achieve the best charge matching, the corresponding uniform doping concentration of P-type silicon is P0 = 6E15 / CM3,

[0059] The super junction semiconductor device structure of the present invention includes:

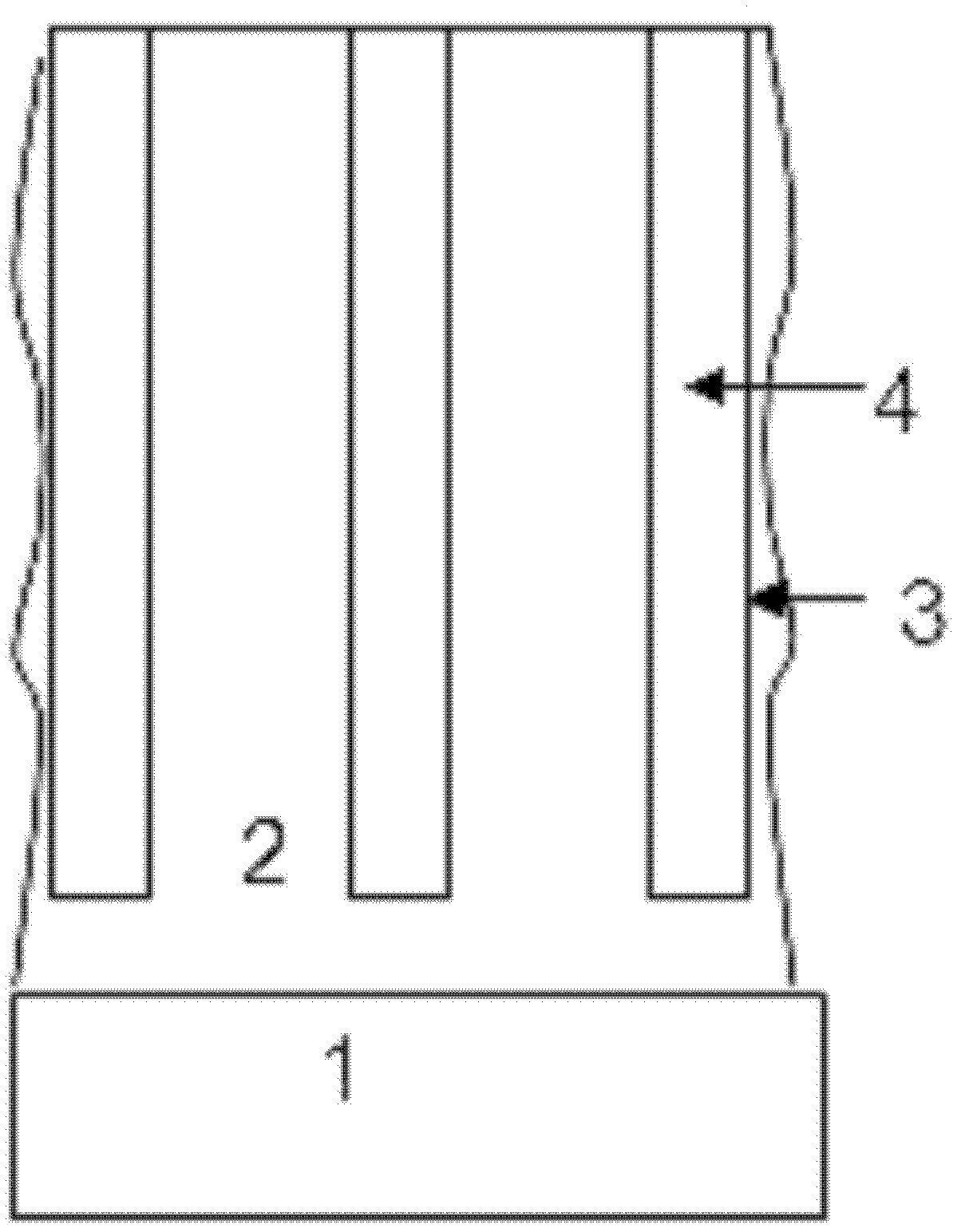

[0060] An N+ substrate (1), on which an N-type epitaxy (2) is grown, and the N-type epitaxy (2) has a plurality of P trenches (3), and the P trenches are filled with P-type silicon (4), forming a P-type film;

[0061] The top of the N-type epitaxy (2) has multiple N trenches (5), the N trenches (5) have an oxide film (5.1), and the oxide film (5.1) is filled with N-type silicon (6), forming an N-type thi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com