Chip package structure and manufacturing method thereof

A technology of chip packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc. Solve problems such as solid connection, to avoid cantilever deviation, avoid pin deformation, and avoid poor bonding of welding wires

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

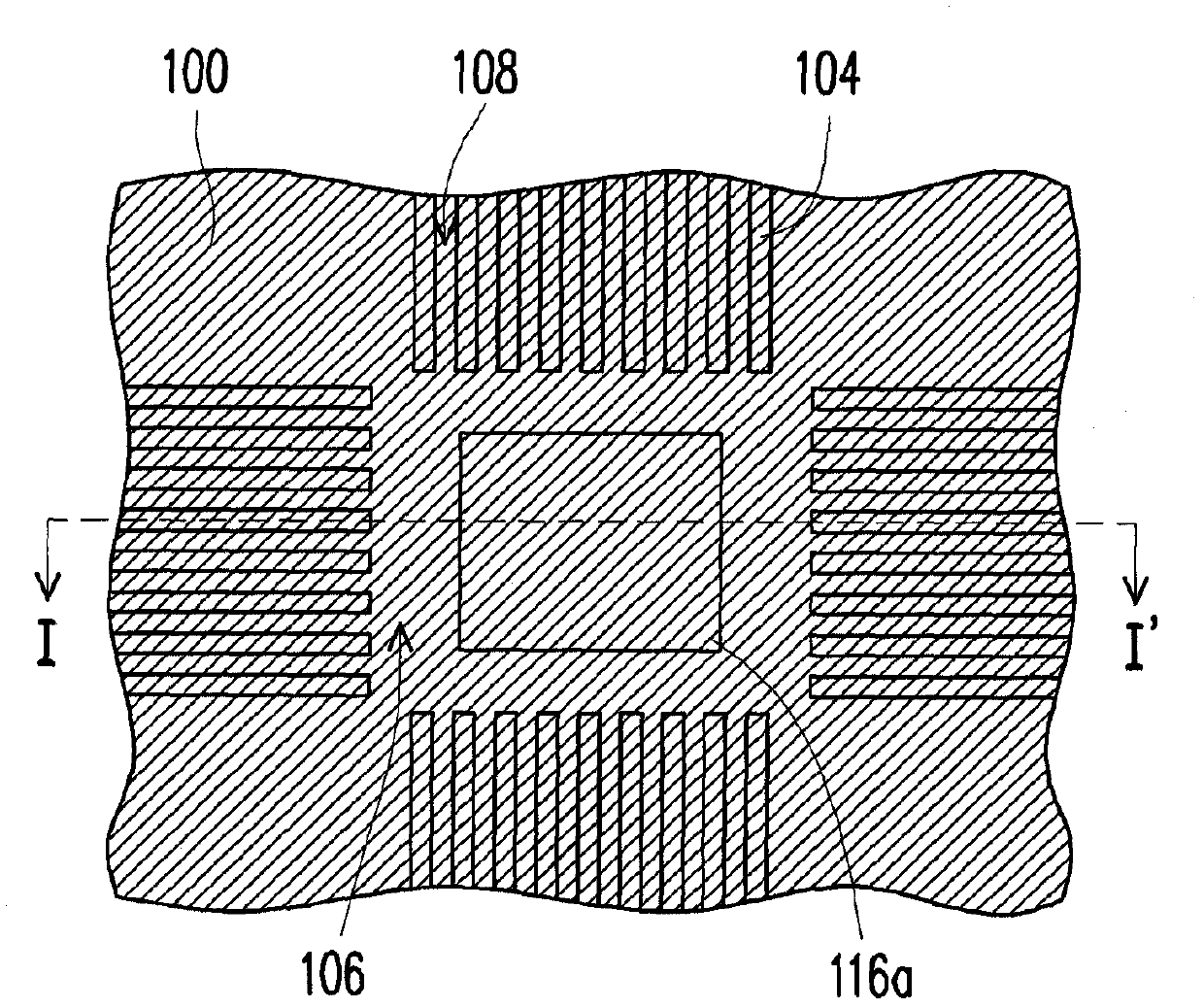

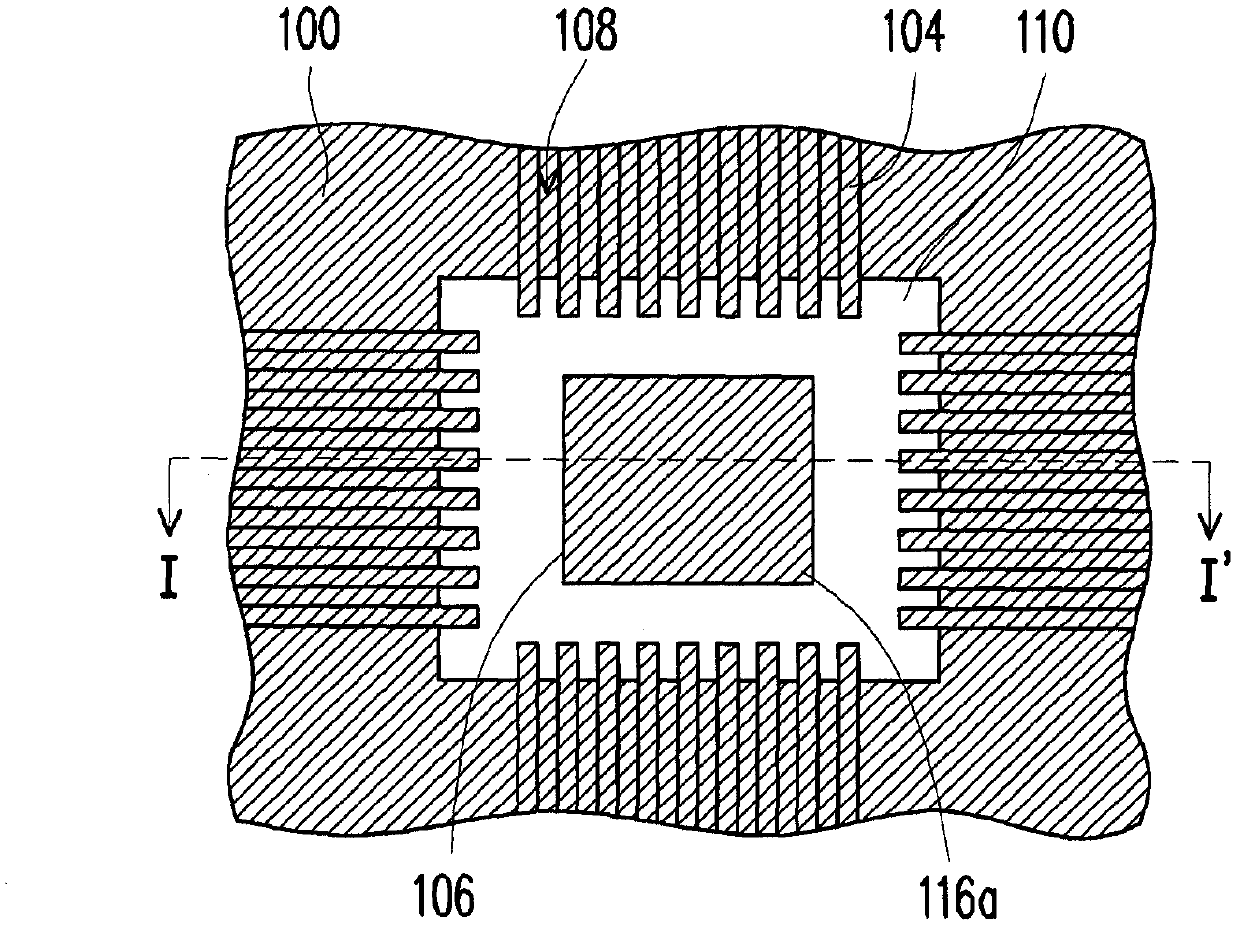

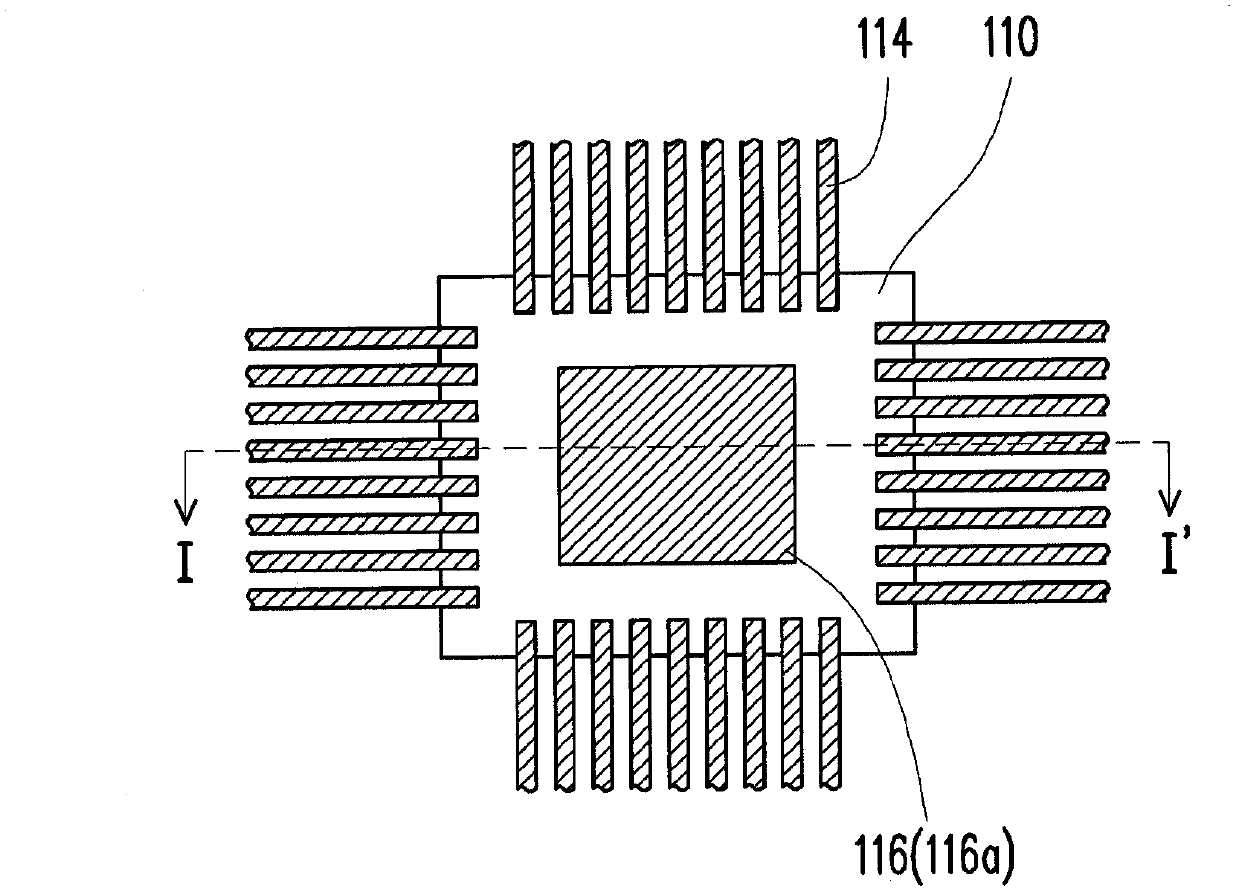

[0022] Figure 1A to Figure 1D It is a schematic top view of a method for manufacturing a chip package structure according to an embodiment of the present invention. Figure 2A to Figure 2D in accordance with Figure 1A to Figure 1D The cross-sectional schematic diagram shown by the section line I-I' in . First, please also refer to Figure 1A and Figure 2A , providing a metal layer 100 . The metal layer 100 has a first upper surface 100a and a first lower surface 100b opposite to the first upper surface 100a. The metal layer 100 is, for example, a copper foil substrate, which can be used to manufacture multiple lead frames. In this embodiment, only one lead frame is shown. Then, the first upper surface 100a of the metal layer 100 is patterned to define a chip bonding portion 116a and a plurality of lead portions 104, wherein there is a gap 106 between the lead portion 104 and the chip bonding portion 116a, and adjacent There are gaps 108 between the pin portions 104 . ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More