Etching method for improving bottom of silicon carbide table board

A silicon carbide, mesa technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of easy operation, improved etching method, and smooth surface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

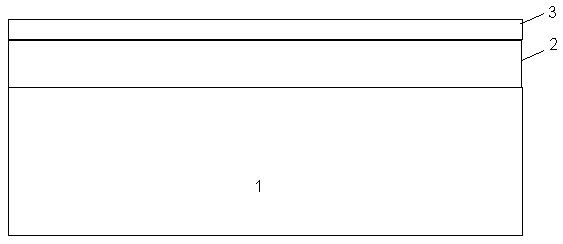

[0022] Process step 1, a layer of dielectric film 3 is formed on the silicon carbide epitaxial layer 2 by chemical vapor deposition, such as figure 1 As shown; the silicon carbide epitaxial layer 2 is a silicon carbide wafer, or an epitaxial layer in which one or more layers of silicon carbide films are grown on the silicon carbide substrate 1 . The chemical vapor deposition method used is inductively coupled plasma enhanced chemical vapor deposition (ICP-PECVD) or plasma enhanced chemical vapor deposition (PECVD).

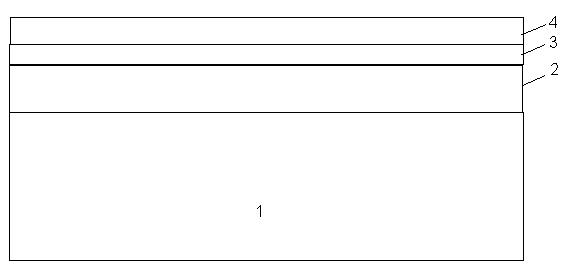

[0023] Process step 2, coating photoresist 4 on dielectric film 3, such as figure 2 shown.

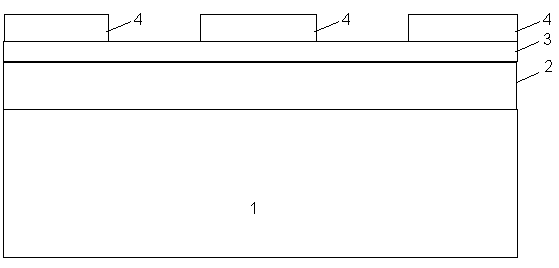

[0024] The third process step is to form the pattern transfer of the mesa through the photolithography process, such as image 3 shown.

[0025] Process step 4, the photoresist 4 is used as a barrier layer, and the dielectric film 3 is dry-etched using the first condition, such as Figure 4 shown.

[0026] The first conditional dry etching dielectric film 3 process i...

Embodiment 2

[0047] Process step 1, a layer of dielectric film 3 is formed on the silicon carbide epitaxial layer 2 by chemical vapor deposition, such as figure 1 As shown; the silicon carbide epitaxial layer 2 is a silicon carbide wafer, or an epitaxial layer in which one or more layers of silicon carbide films are grown on the silicon carbide substrate 1 . The chemical vapor deposition method used is inductively coupled plasma enhanced chemical vapor deposition (ICP-PECVD) or plasma enhanced chemical vapor deposition (PECVD).

[0048] Process step 2, coating photoresist 4 on dielectric film 3, such as figure 2 shown.

[0049] The third process step is to form the pattern transfer of the mesa through the photolithography process, such as image 3 shown.

[0050] Process step 4, the photoresist 4 is used as a barrier layer, and the dielectric film 3 is dry-etched using the first condition, such as Figure 4 shown.

[0051] The first conditional dry etching dielectric film 3 process i...

Embodiment 3

[0072] Process step 1, a layer of dielectric film 3 is formed on the silicon carbide epitaxial layer 2 by chemical vapor deposition, such as figure 1 As shown; the silicon carbide epitaxial layer 2 is a silicon carbide wafer, or an epitaxial layer in which one or more layers of silicon carbide films are grown on the silicon carbide substrate 1 . The chemical vapor deposition method used is inductively coupled plasma enhanced chemical vapor deposition (ICP-PECVD) or plasma enhanced chemical vapor deposition (PECVD).

[0073] Process step 2, coating photoresist 4 on dielectric film 3, such as figure 2 shown.

[0074] The third process step is to form the pattern transfer of the mesa through the photolithography process, such as image 3 shown.

[0075] Process step 4, the photoresist 4 is used as a barrier layer, and the dielectric film 3 is dry-etched using the first condition, such as Figure 4 shown.

[0076] The first conditional dry etching dielectric film 3 process i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More