Manufacturing method for semiconductor device with field barrier layer

A field blocking layer and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of low ion efficiency, high cost, and not higher than 500 degrees Celsius in the blocking layer, and achieve flexible amplification Sex and adjustability, good cost performance, cost-saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

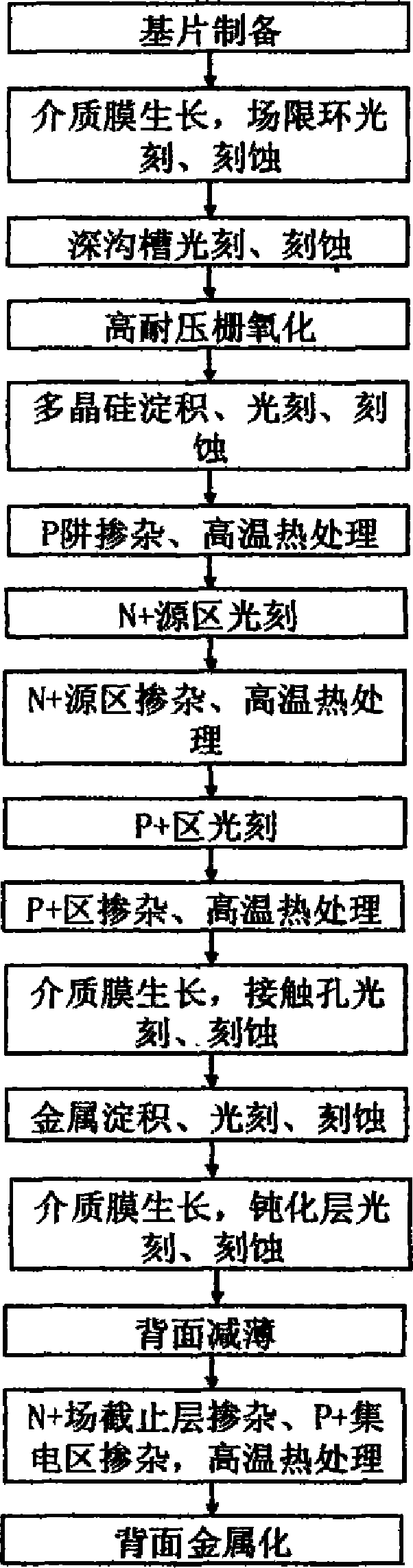

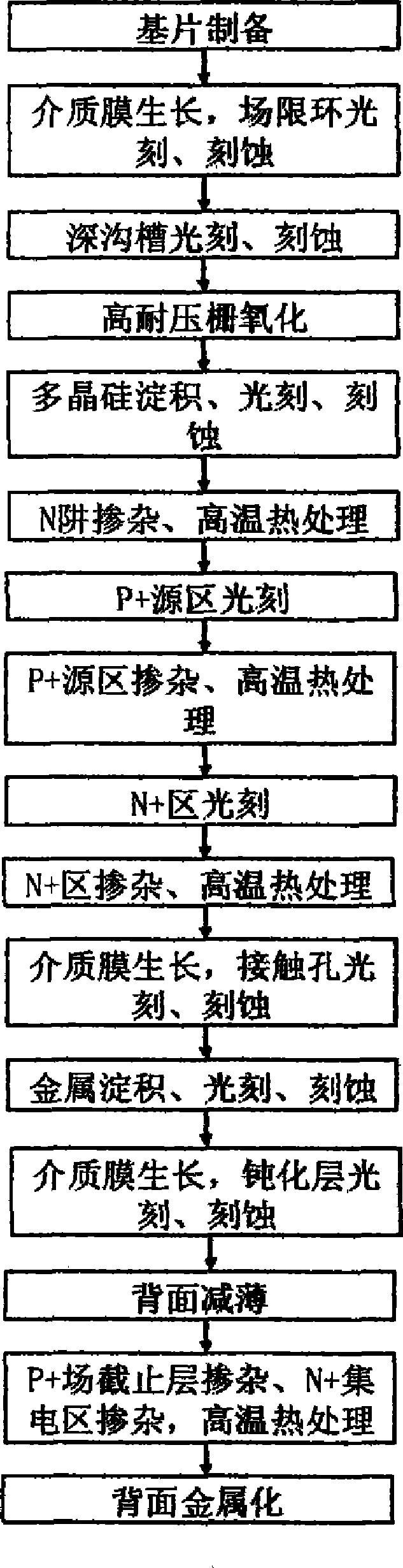

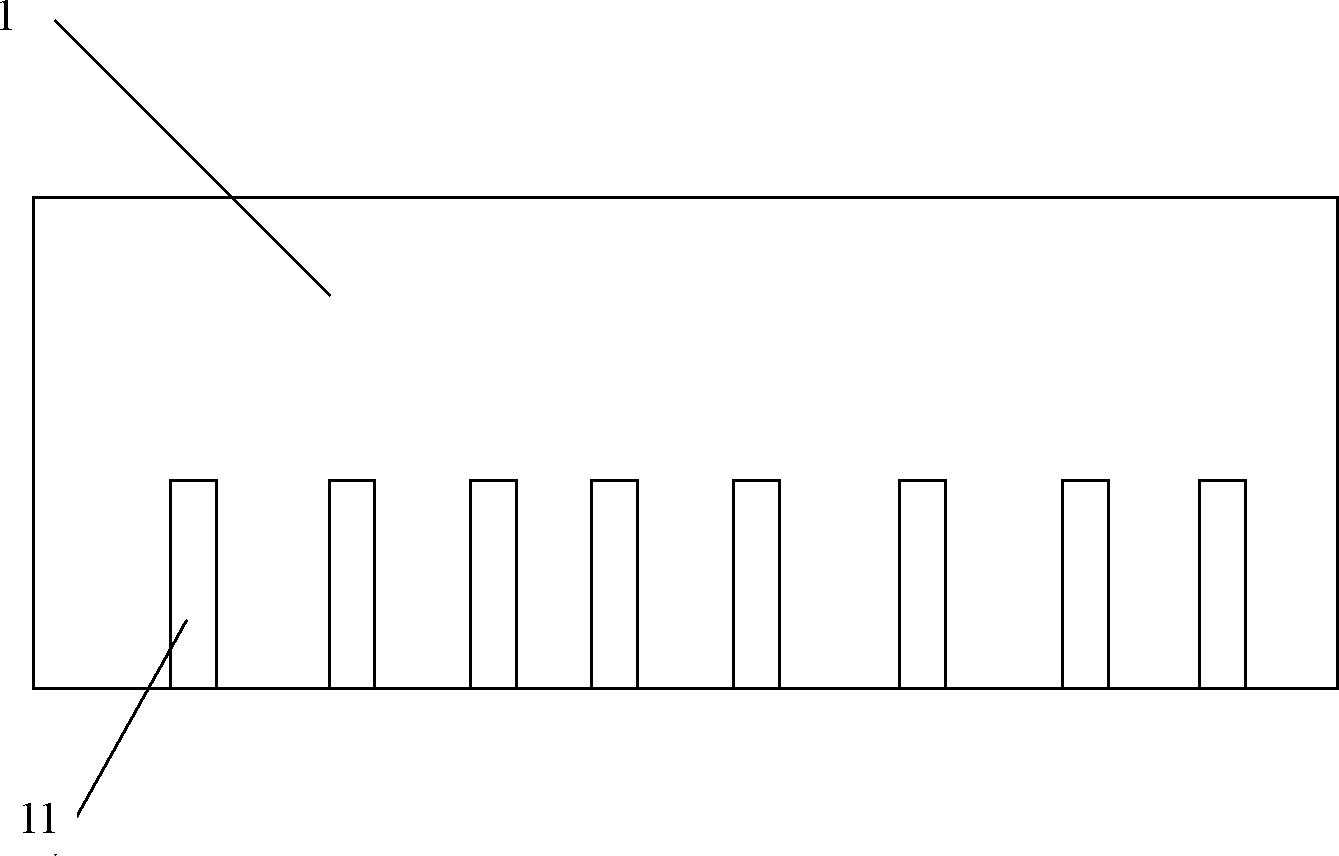

[0036] One embodiment of the method for manufacturing a semiconductor device with a field barrier layer of the present invention includes the following steps:

[0037] 1. Growing a silicon oxide film on the back of the silicon wafer, preferably, the thickness of the silicon wafer is greater than or equal to 500 microns, and the thickness of the silicon oxide film is 5000-20000 angstroms. exposure;

[0038] 2. Etching the silicon oxide film on the back of the silicon wafer to the silicon surface;

[0039] 3. Remove the photoresist, use the silicon oxide film as a barrier layer, etch silicon, etch grooves or holes of required depth on the back of the silicon wafer, and remove the silicon oxide film, preferably, the The depth of the groove or hole is greater than or equal to 20 microns;

[0040] 4. Growing highly doped polycrystalline silicon (N-type or P-type) from the groove or hole on the back of the silicon wafer, preferably, the polycrystalline concentration is greater tha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More