Method for designing high reliability and embedded type minimum central processing unit (CPU) core applicable to aerospace field and based on field programmable gate array (FPGA)

A CPU core and reliability technology, applied in the direction of machine execution devices, etc., can solve problems such as limited resources, achieve cost savings, high program reliability, and reduce component costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

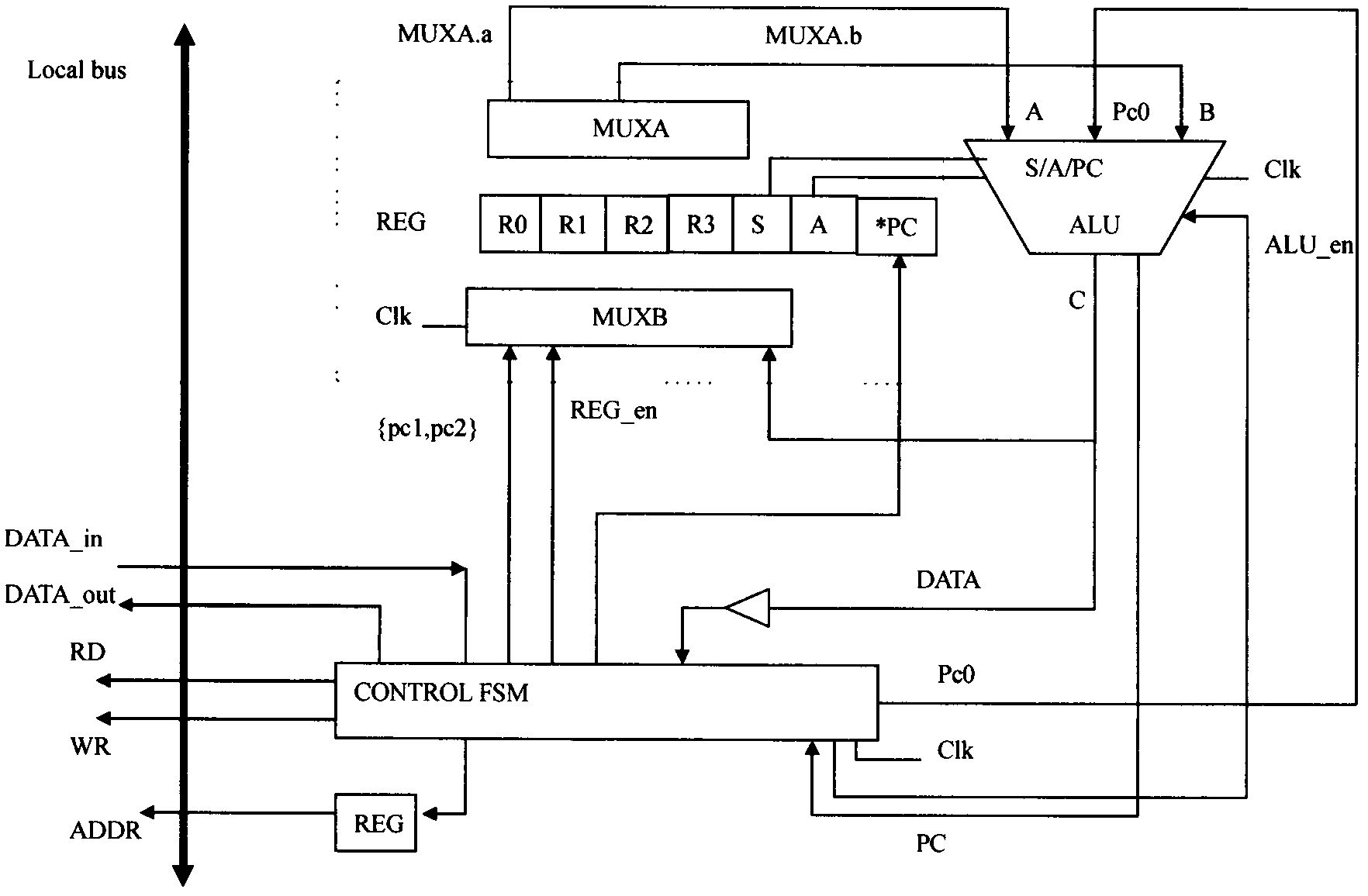

Method used

Image

Examples

specific Embodiment

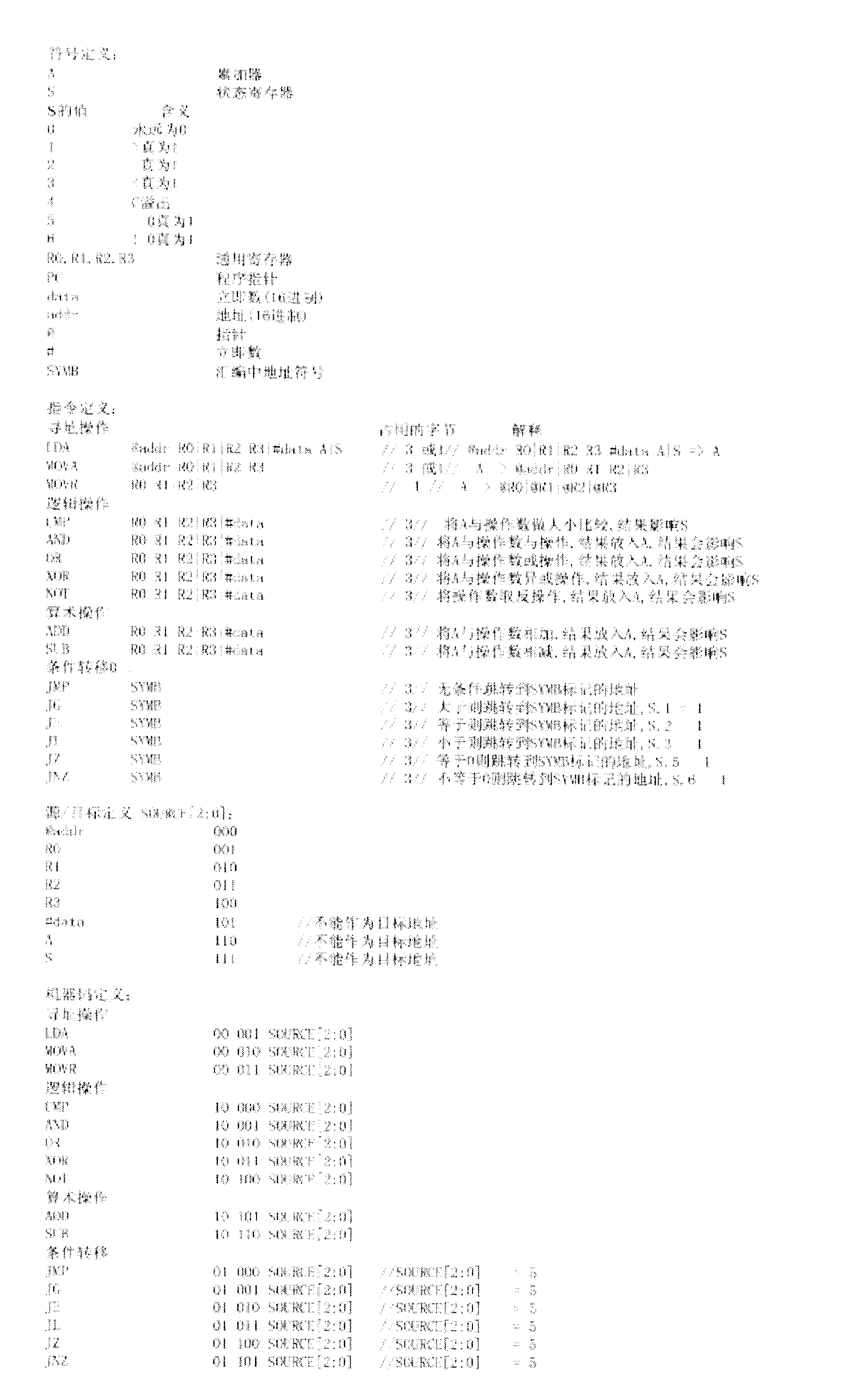

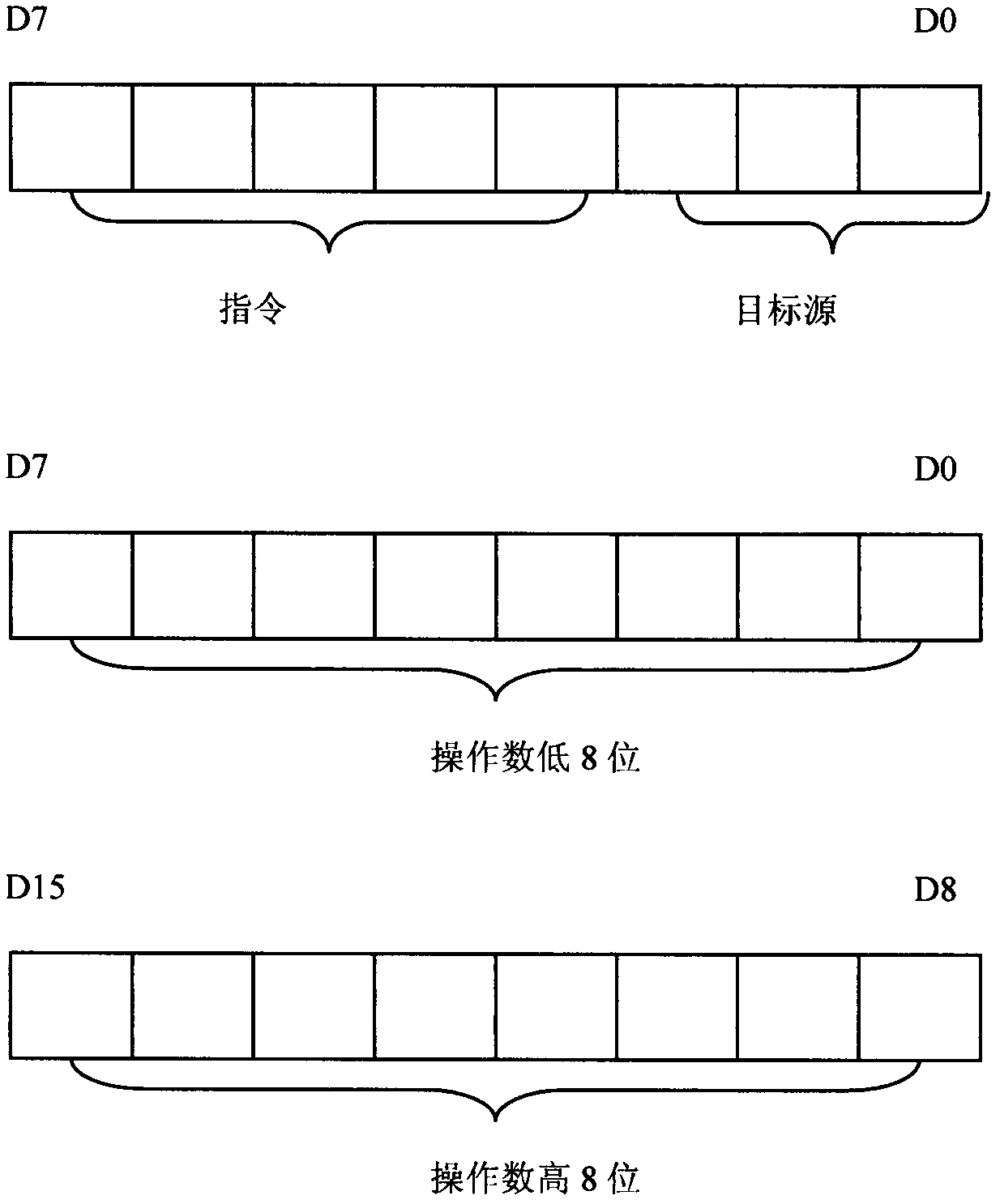

[0033] This embodiment adopts C language to write a section program (a simple 1553B communication program), according to figure 2 The analysis of the instructions and target source uses the imitation assembly language to convert the C language program into Binary format machine code, and writes it into the PROM, and according to the CPU core designed in the FPGA software, disassemble the instruction and target source of the injected code points, identify the instruction type and target source, and then perform data read and write operations. The concrete steps of its method are as follows:

[0034] The C language program is as follows:

[0035]

[0036]

[0037] Step a1: According to figure 2 According to the analysis of the instructions and the target source, the program is written in imitation assembly language according to the C language program. This step is an important step in the entire design. This step is the source of the entire data. The code after writin...

Embodiment

[0053] Taking a certain model as an example, the architecture of FPGA+SCM+off-chip RAM+off-chip PROM was originally adopted, and the code was written in C language program. Now use the same program, write new code with imitation assembly language, compile and link, generate Binary format code, and write it into off-chip PROM, the original program function works well.

[0054] As can be seen from the above, adopting the method of the present invention to design the FPGA embedded CPU core in the aerospace field is a low price, increases the reliability of aerospace components, and can save a lot of financial and material resources.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More