Split gate type flash memory and forming method thereof

A split-gate flash memory and floating gate technology, which is applied in the direction of electrical components, electric solid-state devices, circuits, etc., can solve the problems of poor working efficiency of split-gate flash memory, reduce coupling capacitance, improve coupling coefficient, and capacitive coupling capability change effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

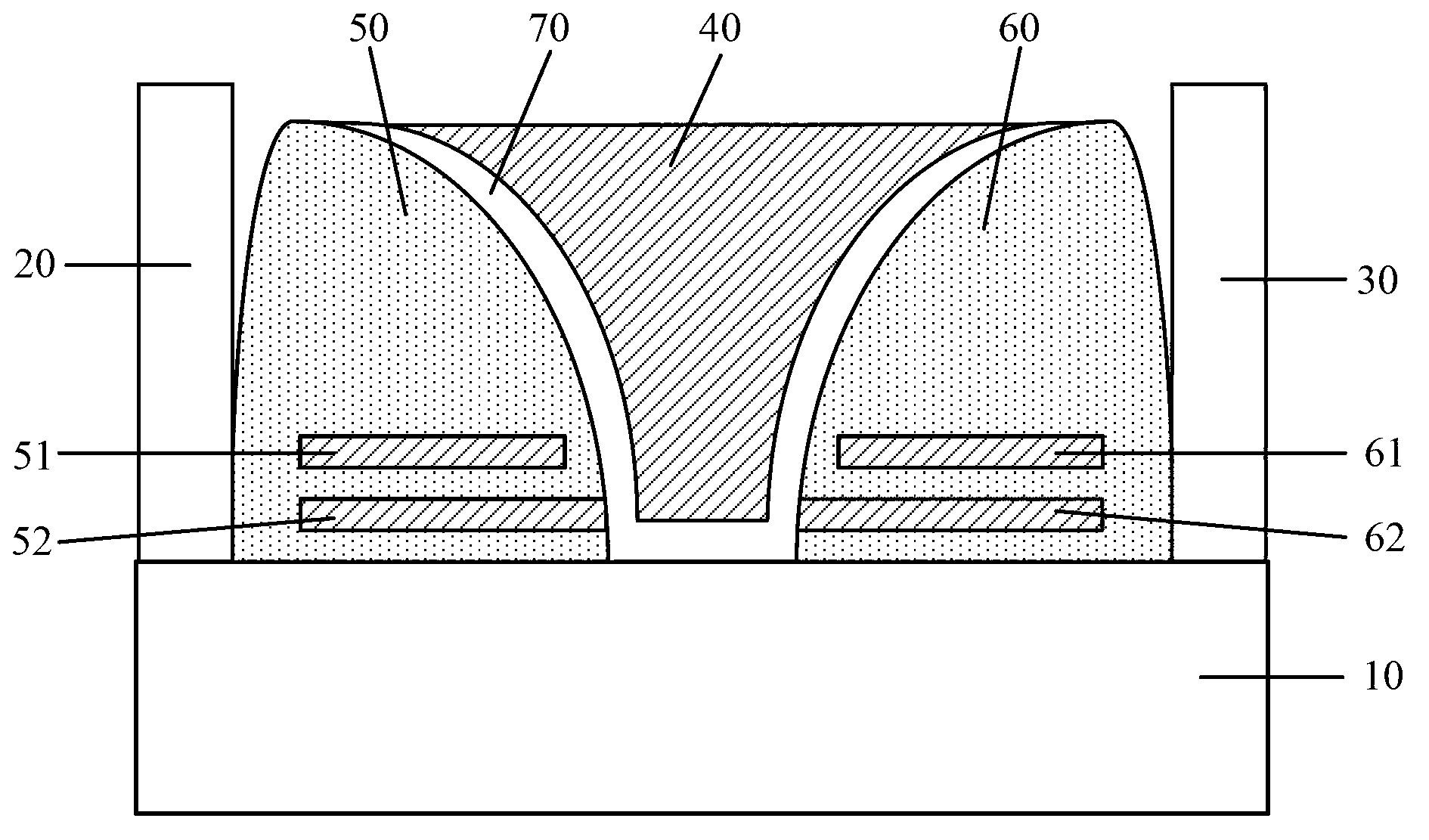

[0025] The first embodiment of the present invention firstly provides a method for forming a split-gate flash memory, please refer to Figure 2 to Figure 11 , is a schematic structural diagram of the formation process of the split-gate flash memory according to the first embodiment of the present invention.

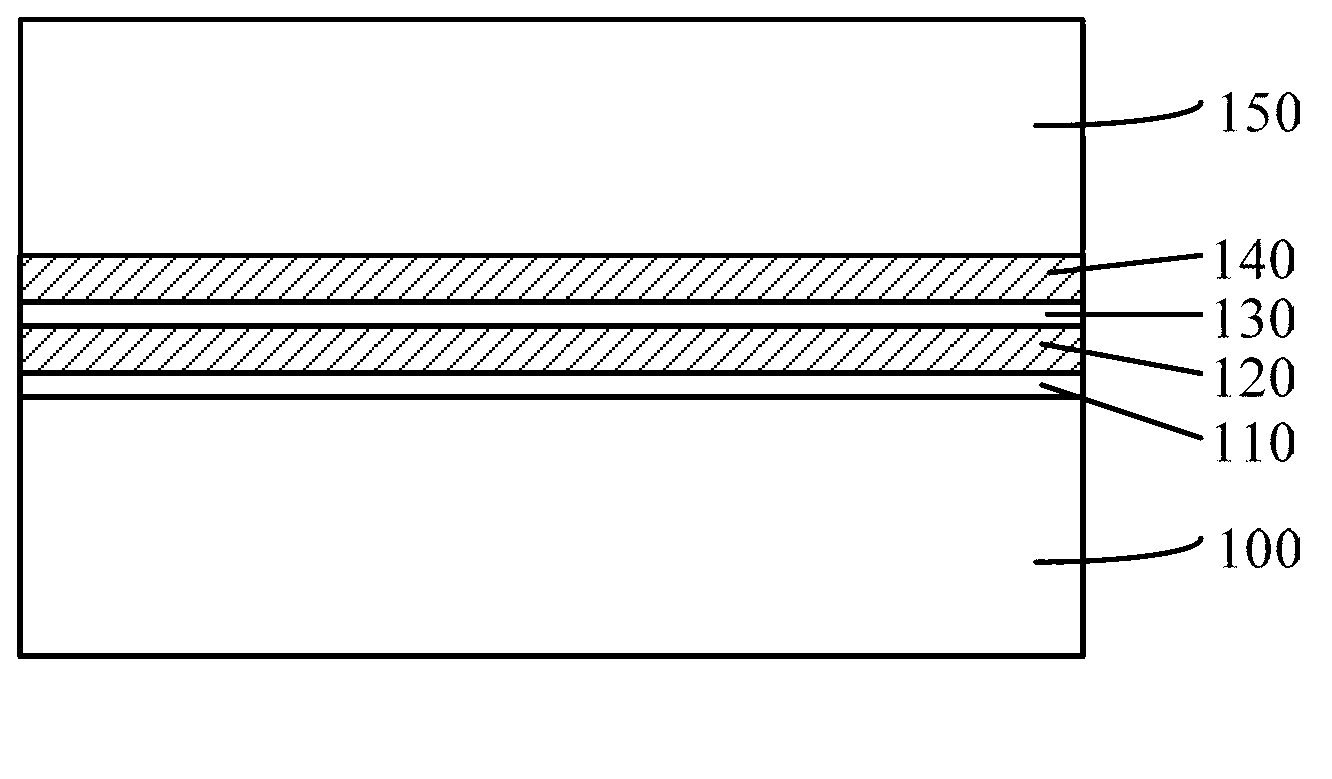

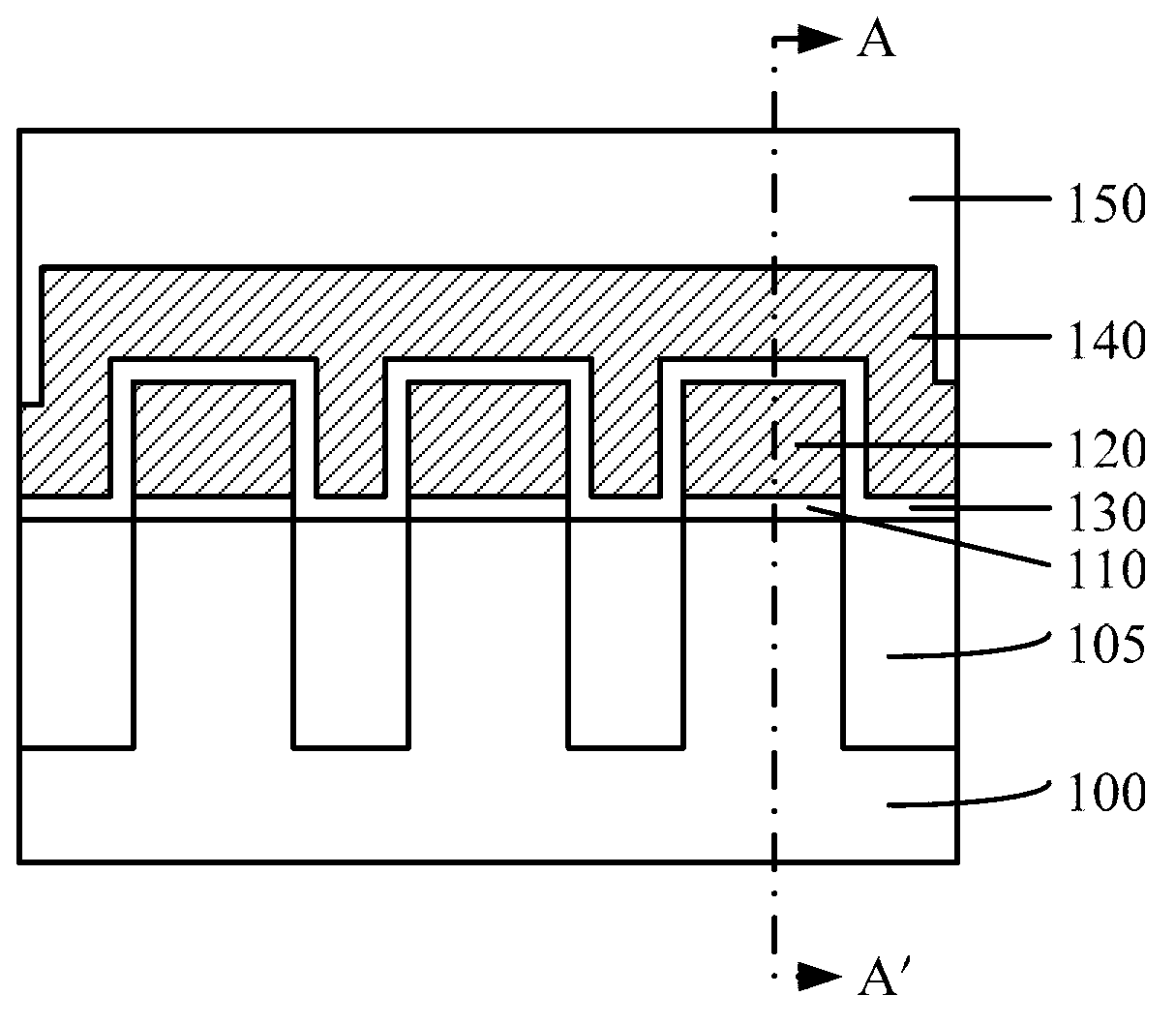

[0026] Please refer to figure 2 , a semiconductor substrate 100 is provided, a first insulating material layer 110 is formed on the surface of the semiconductor substrate 100, a floating gate material layer 120 is formed on the surface of the first insulating material layer 110, and a floating gate material layer 120 is formed on the surface of the floating gate material layer 120. The second insulating material layer 130 , a control gate material layer 140 is formed on the surface of the second insulating material layer 130 , and a mask layer 150 is formed on the surface of the control gate material layer 140 .

[0027]The semiconductor substrate 100 is selected from o...

no. 2 example

[0055] The second embodiment of the present invention also provides a method for forming a split-gate flash memory, please refer to Figure 12 to Figure 18 , is a schematic structural diagram of the formation process of the split-gate flash memory according to the second embodiment of the present invention.

[0056] In the formation process of the split-gate flash memory in the second embodiment of the present invention, the formation of the first spacer and the previous process are the same as those in the first embodiment of the present invention, please refer to Figure 2 to Figure 4 , which will not be described here.

[0057] Please refer to Figure 12 , using the first sidewall 161 as a mask, firstly etch the control gate material layer 140 and the second insulating material layer 130 to form a third opening 173 .

[0058] Please refer to Figure 13 , forming a fourth sidewall 164 on the sidewall of the third opening, using the fourth sidewall 164 as a mask to etch a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More