Image transmission and processing system based on FPGA (Field Programmable Gate Array) and multi-core DSP (Digital Signal Processor)

A technology of processing system and data transmission system, applied in the field of image transmission and processing system based on FPGA and multi-core DSP, can solve the problem of no application, etc., and achieve the effect of improving computing speed and processing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific example

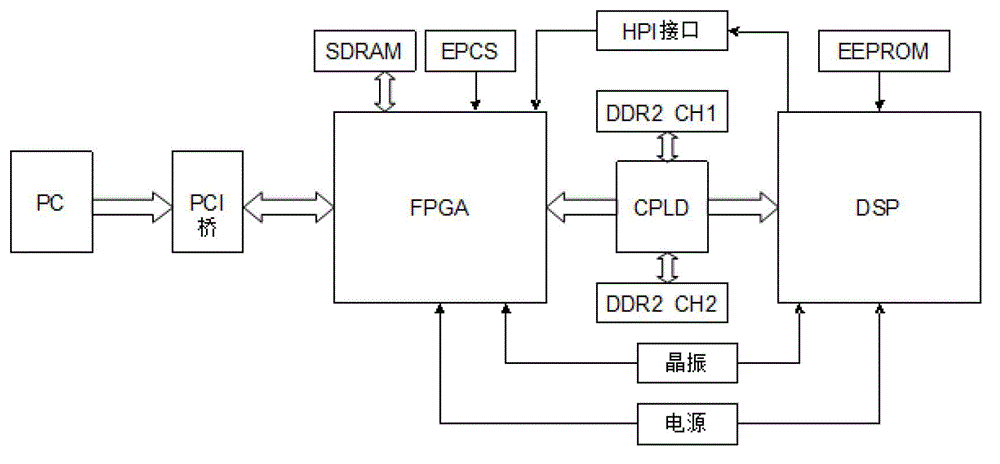

[0026] 1. After the system is powered on, the FPGA (model EP2C35F672C6N) partly initializes and then starts to read the image data buffered into the internal FIFO through the PCI bridge. Here, choose PCI9056 as the PCI bridge to connect PC and FPGA. The interface between PCI9056 and FPGA can be realized by connecting the signals (data, address, control, etc.) of the local end of PCI9056 with the pins of FPGA.

[0027] 2. The FPGA writes the data in the FIFO to the DDR2 SDRAM (model MT47H16M16) connected to it. FPGA's DDR2SDRAM interface such as figure 2 shown.

[0028] 3. After the data in DDR2SDRAM reaches a certain amount, FPGA notifies CPLD to exchange the bus control right of dual-channel DDR2SDRAM between FPGA and DSP (model TMS320C6472), and sends an interrupt signal to DSP. Here, what needs to be explained is: TMS320C6472 itself is not directly connected with DDR2SDRAM, but needs to be connected with one of the DDR2SDRAMs through switching of CPLD. When the DDR2SDR...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More