Semiconductor packaging structure and method of fabricating same

A packaging structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as excessive thickness and poor reliability, and achieve improved reliability and good electrical performance Transmission efficiency, the effect of saving high material costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

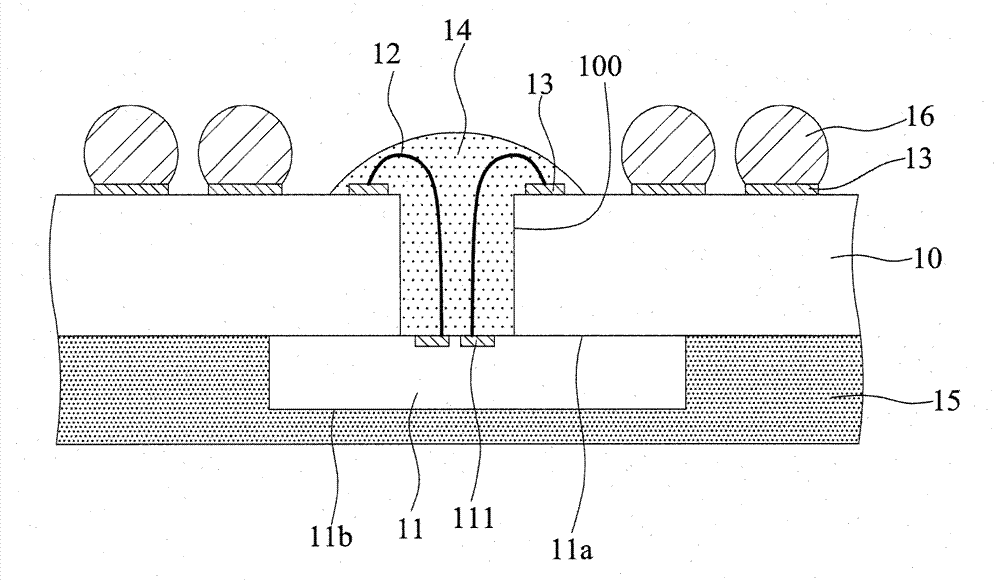

[0063] Generally speaking, the implementation of the present invention can be divided into three stages, at first, prepare a plurality of semiconductor chips such as dynamic random access memory (DRAM), please refer to Figure 2A to Figure 2C , is a cross-sectional view of the semiconductor chip of the semiconductor package structure of the present invention and its manufacturing method.

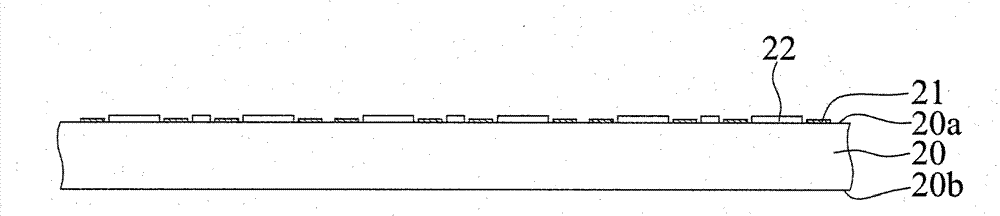

[0064] Such as Figure 2A As shown, a semiconductor wafer 20 having an opposite active surface 20 a and a non-active surface 20 b, and a plurality of electrode pads 21 and buffer layers 22 formed on the active surface 20 a are provided.

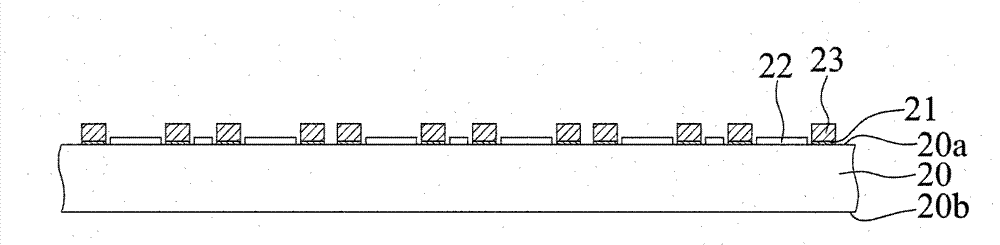

[0065] Such as Figure 2B As shown, a metal bump 23 is formed on each of the electrode pads 21 .

[0066] Such as Figure 2C As shown, the semiconductor wafer 20 is thinned from the non-active surface 20b, and the semiconductor wafer 20 is cut to obtain a plurality of semiconductor chips 20', each of which has an opposite active surface 20a' and a non-ac...

no. 2 example

[0085] Generally speaking, the main difference between this embodiment and the first embodiment is only the implementation of the metal foil, please refer to Figure 5A to Figure 5C , which is a cross-sectional view of the second embodiment of the metal foil 50' of the semiconductor package structure of the present invention and its manufacturing method.

[0086] Such as Figure 5A As shown, a metal plate 50 is provided, and the material of the metal plate 50 can be copper or other metals.

[0087] Such as Figure 5B As shown, a plurality of punched bumps 51 are formed on the metal plate 50 by punching.

[0088] Such as Figure 5C As shown, the third adhesive layer 32 covering each of the stamped bumps 51 is formed on the metal plate 50 , and then, the third adhesive layer 32 can be solidified in a B-stage according to circumstances.

[0089] Next, carry out assembly and packaging operations, please refer to Figure 6A to Figure 6I , which is a cross-sectional view of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com