High-temperature wafer level burn-in test scheduling method for SoC (system on a chip) chip

A test scheduling and aging test technology, applied in the field of integrated circuits, can solve problems such as insufficient reliability tests, save test costs, improve accuracy, and reduce the requirements of test equipment.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

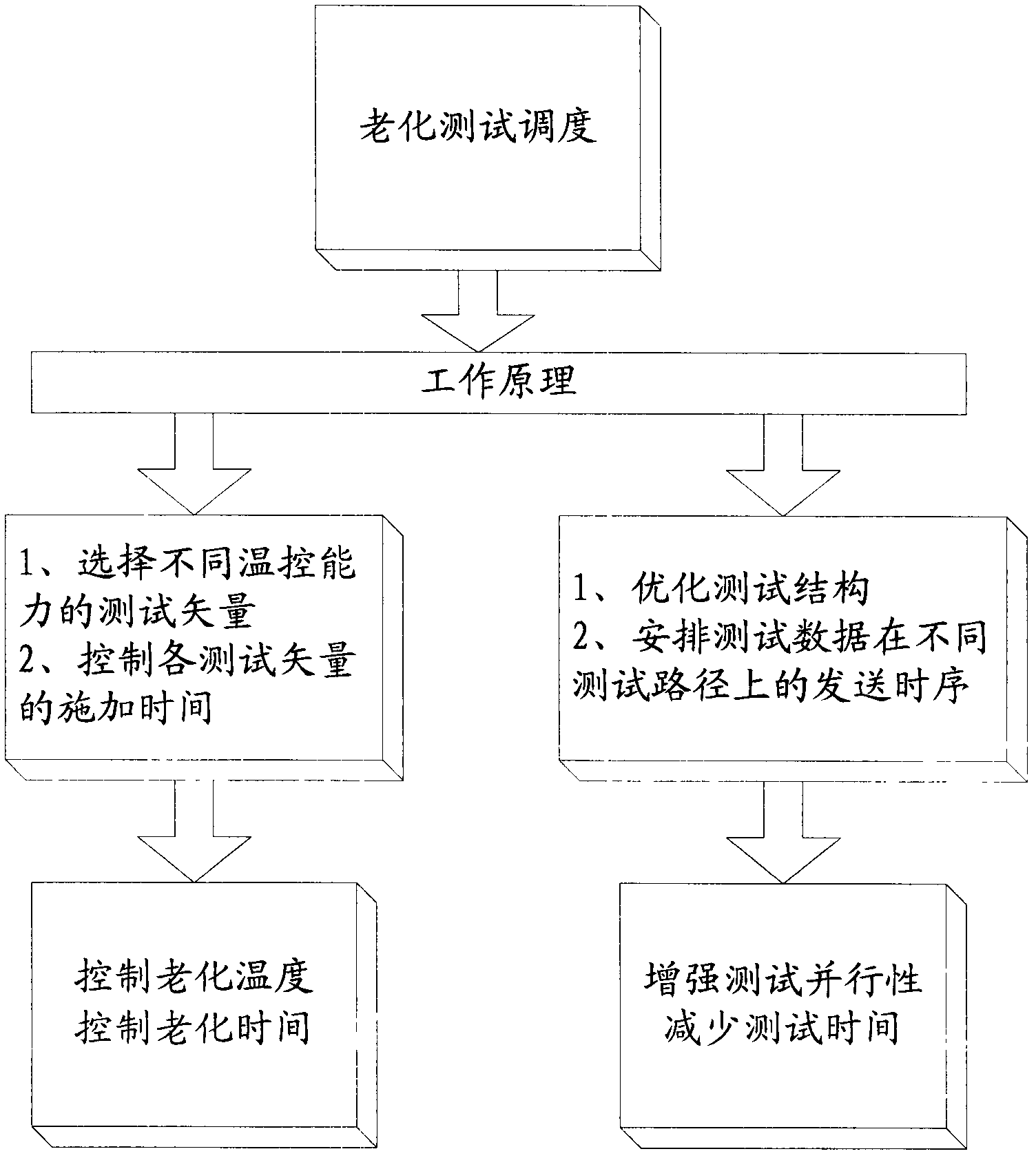

[0017] The needs of the present invention are implemented according to the following 4 steps:

[0018] first step:

[0019] Obtain information such as process documents, wafer material parameters, wafer layout and dimensions, burn-in test requirements, etc.

[0020] Step two:

[0021] Calculate the effect of different test input vectors on the power consumption and temperature control of the chip, and obtain the test vector sets corresponding to different temperature rise conditions.

[0022] Circuit power consumption P is mainly composed of dynamic power consumption and static power consumption.

[0023] The dynamic power consumption of the circuit is determined by formula (1):

[0024] P dyn =1 / 2·C·V 2 · N · f(1)

[0025] Among them, V is the operating voltage of the circuit, C is the load capacitance of the circuit, f is the operating frequency, and N is the number of circuit level jumps. After the circuit is made, the circuit load capacitance C is basically unchange...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More