Split gate flash memory and forming method thereof

A memory and flash technology, applied in the field of split gate flash memory and its formation, can solve the problems of high power consumption and poor erasing performance, and achieve the effects of increasing voltage difference, reducing power consumption and reducing voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

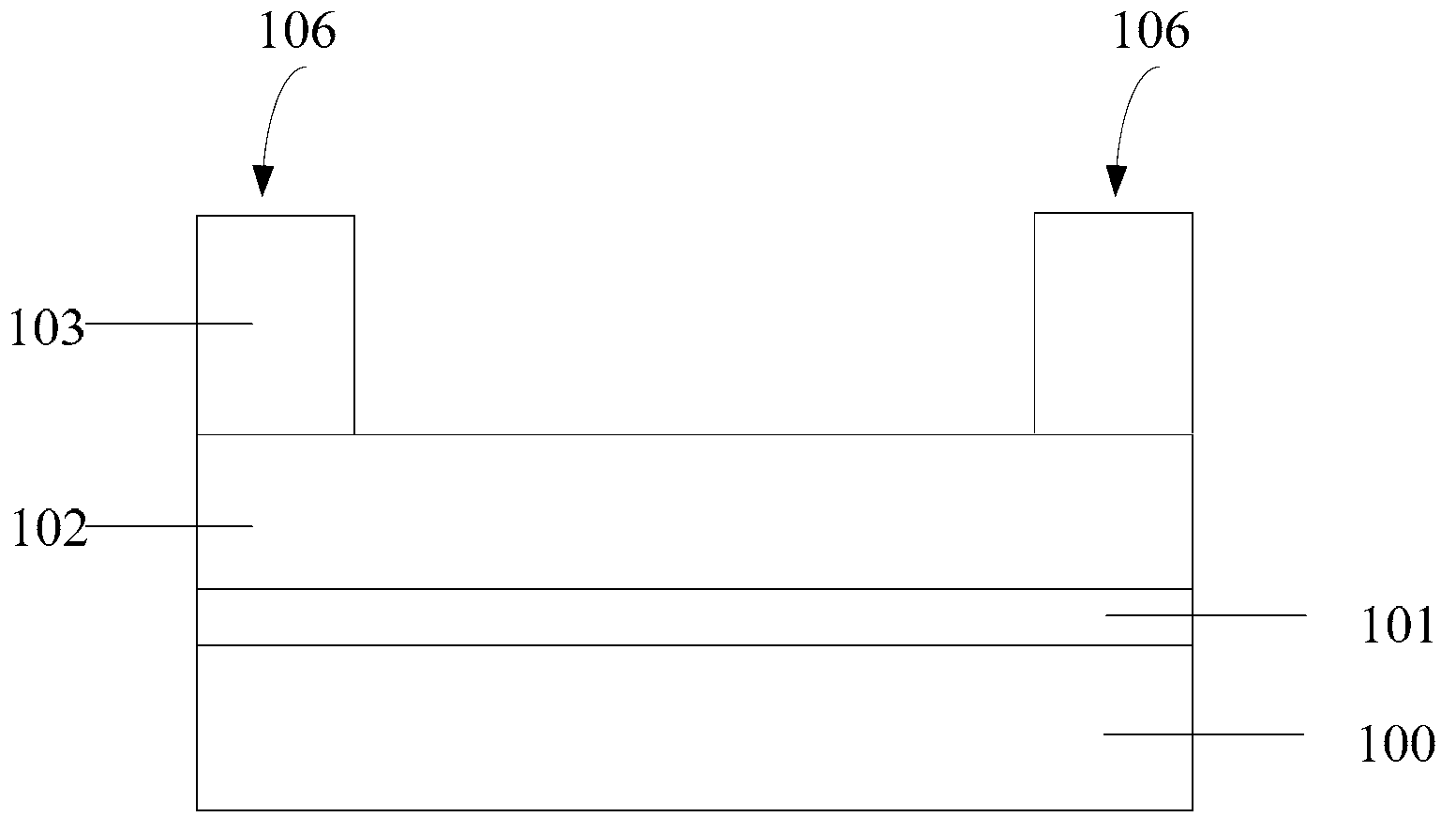

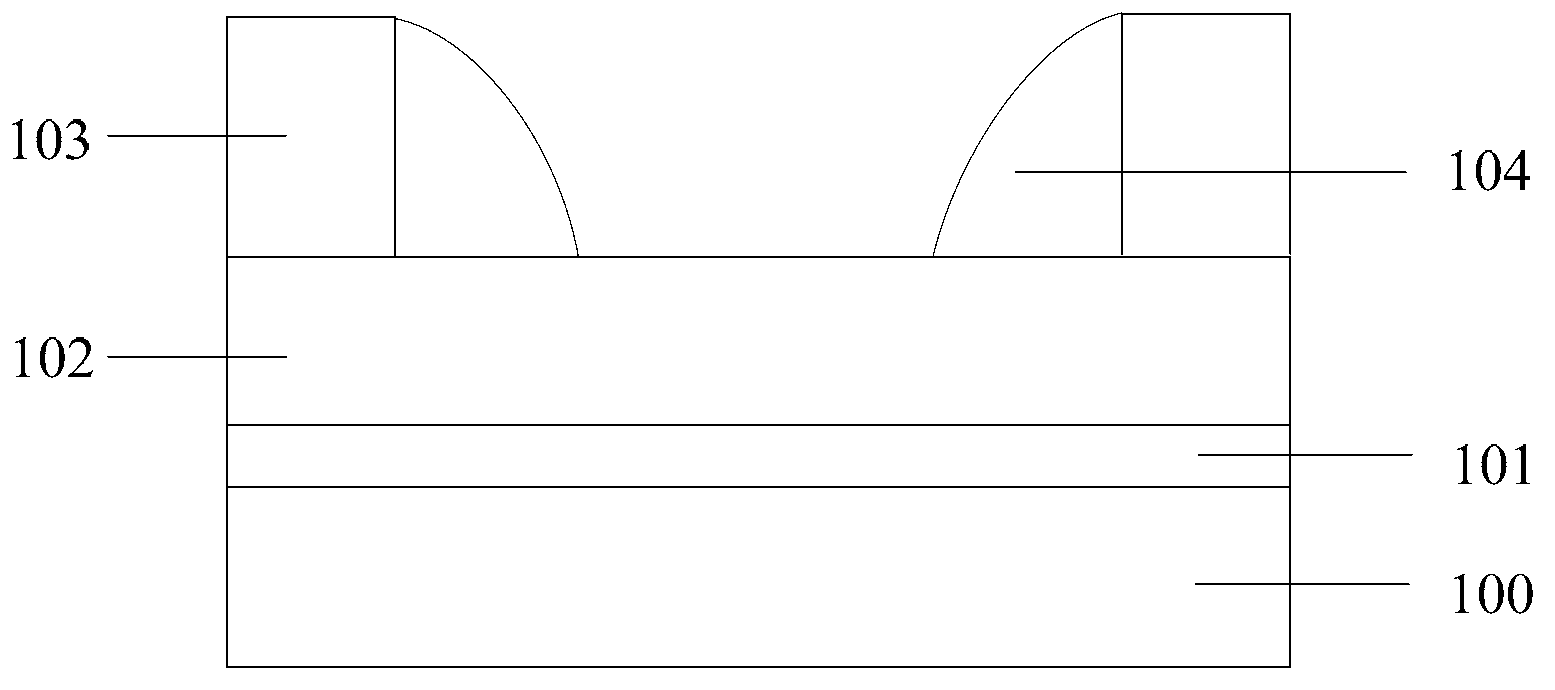

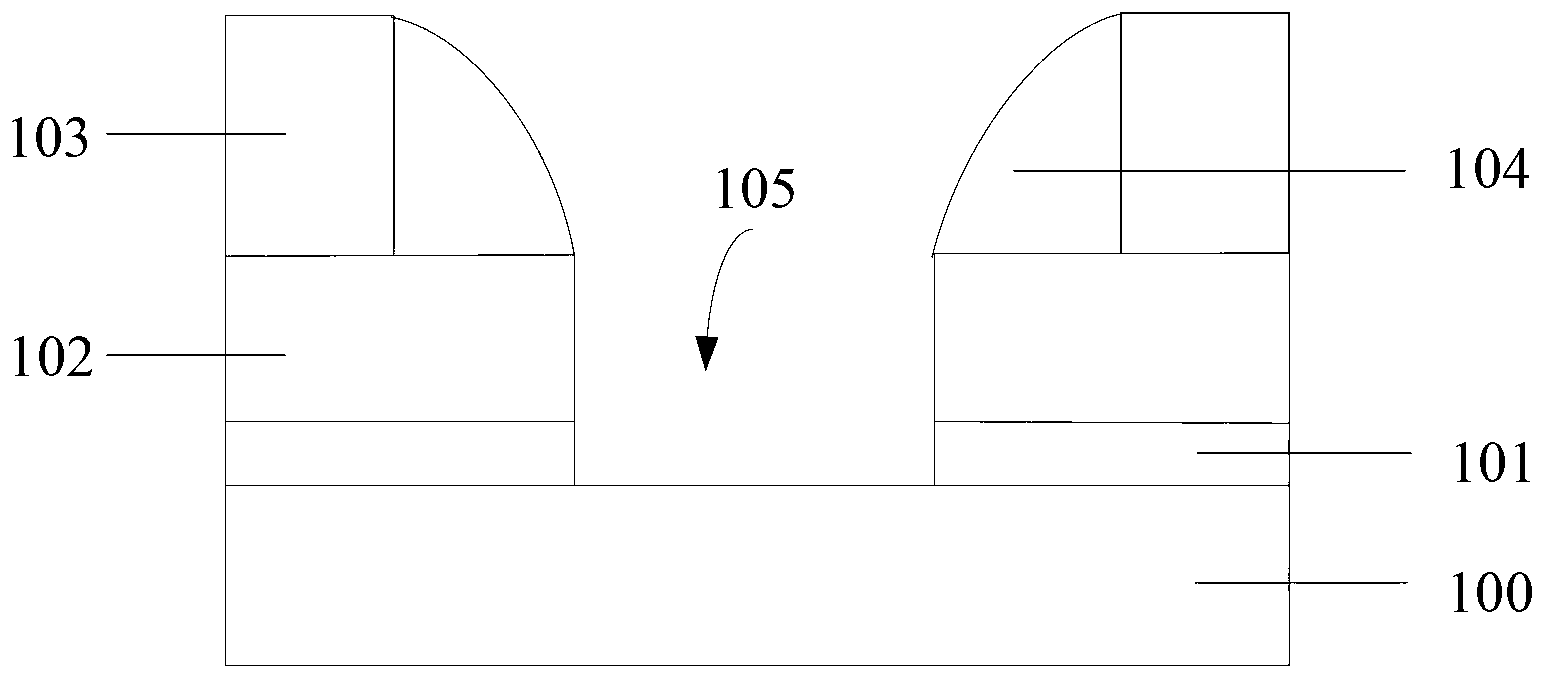

[0058] refer to Figure 7 with Figure 8 , when performing data erasing on the existing self-aligned split-gate flash memory, apply a high negative bias voltage to the word line 111, while maintaining the source line 107, the corresponding drain (not shown) and the substrate When the voltage is grounded or close to 0V, electrons can be pulled out from the floating gate 108 . Therefore, the floating gate releases its accumulated electrons to the word line 111 through the Fowler-Nordheim (abbreviated as F-N) tunneling mechanism.

[0059] The inventors have found through research that the erasing performance of the self-aligned split-gate flash memory is related to the voltage difference V between the word line and the floating gate during erasing. 12 Related, V 12 Higher means that the electric field between the word line and the floating gate is stronger, and F-N tunneling is more likely to occur, so V 12 The higher the value, the higher the erase performance of the device. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More