Multi--core processor oriented on-chip lock variable global addressing storage method and device

A technology of many-core processors and global addressing, which is applied in the field of architecture design of shared-storage many-core processors, can solve problems such as performance degradation, inapplicability, and lock variable memory mapping, so as to improve parallel performance, improve utilization rate, The effect of simplifying operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

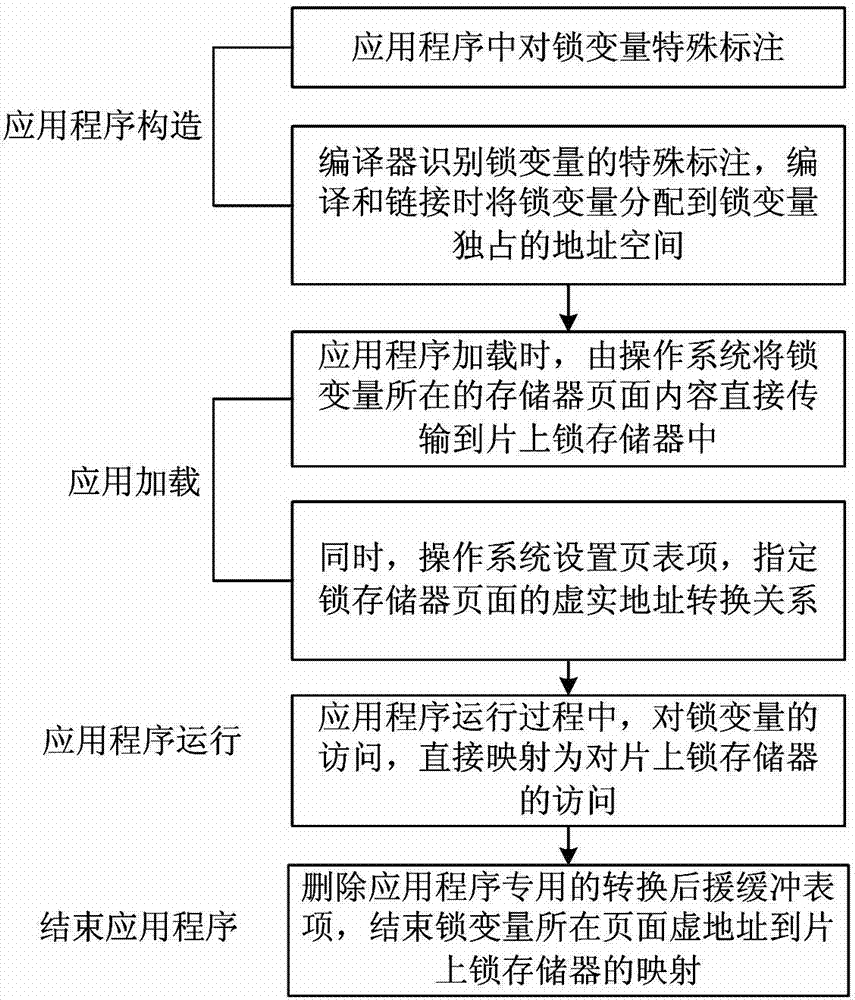

[0039] Such as figure 2 As shown, the implementation steps of the on-chip lock variable global address storage method for many-core processors in this embodiment are as follows:

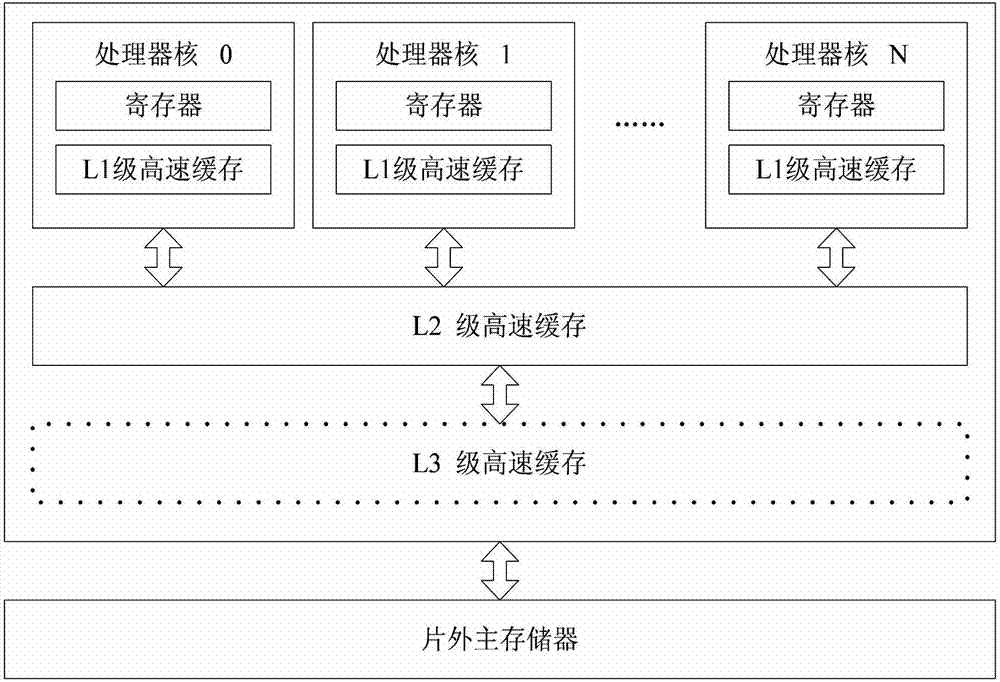

[0040] 1) Establish a global addressable on-chip lock memory for storing lock variables on the many-core processor chip in advance, and directly connect the global addressable on-chip lock memory to the access unit of each processor core on the many-core processor; Mark the lock variable in the application program, and allocate the lock variable to the exclusive address space of the lock variable when compiling and linking the application program;

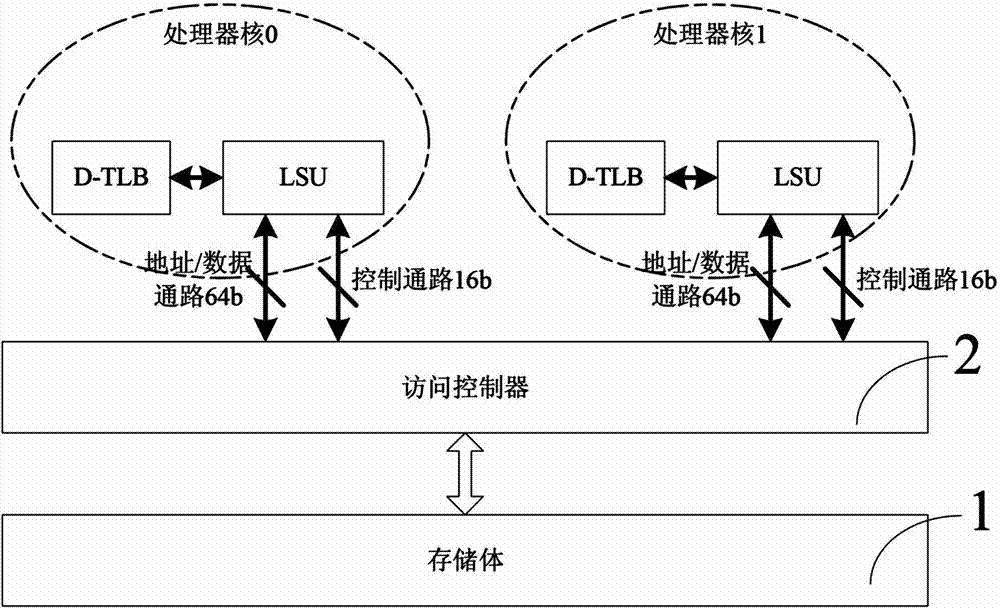

[0041] 2) When the application program is loaded, the operating system transfers the virtual memory page where the lock variable of the application program is located from the off-chip main memory to the global addressing on-chip lock memory, and specifies by constructing an application-specific translation lookaside buffer (TLB) entry The virtual addre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More