Programmable precise clock circuit based on field programmable gate array (FPGA)

A precise clock and circuit technology, applied in the direction of logic circuits using specific components, logic circuits using basic logic circuit components, etc., can solve problems such as increasing device costs, hindering high chip integration, and difficulty in integrating chips, so as to improve integration Degree, cost reduction, and the effect of saving FPGA resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

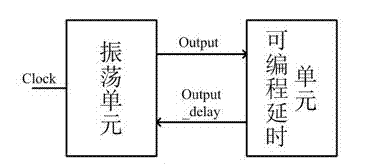

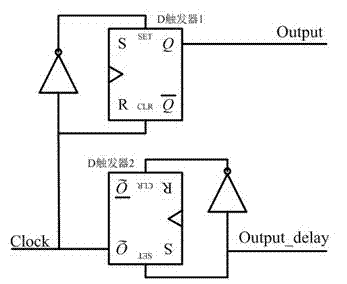

[0016] An FPGA-based programmable precise clock circuit of the present invention includes an oscillating unit and a programmable delay unit. The described oscillating unit is composed of 2 D flip-flops and 2 NOT gates to realize the inversion of the output clock signal; the described The programmable delay unit is composed of several selectors and basic delay units, and uses layout and wiring constraint technology to make the clock cycle precise and controllable.

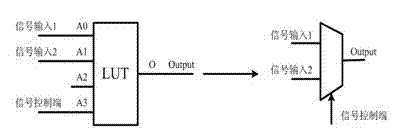

[0017] The described basic delay unit is realized by the look-up table of FPGA, which can delay a fixed time. Nanosecond-level precise delay can be realized.

[0018] The described two-choice selector NAND gate is realized by the look-up table of FPGA, so as to realize the minimum delay time of the system.

[0019] The described programmable delay unit is composed of a number of selectors and a basic delay unit. The selector selects whether to pass through the basic delay unit, and can output clock signals of diffe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com