Wafer structure for reducing damage of wafer cutting stress and layout design method

A wafer and graphics technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as chip access and chip failure, and achieve the effect of preventing stress cracking and shortening the damage distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The specific embodiments described here are only used to explain the present invention, but not to limit the present invention.

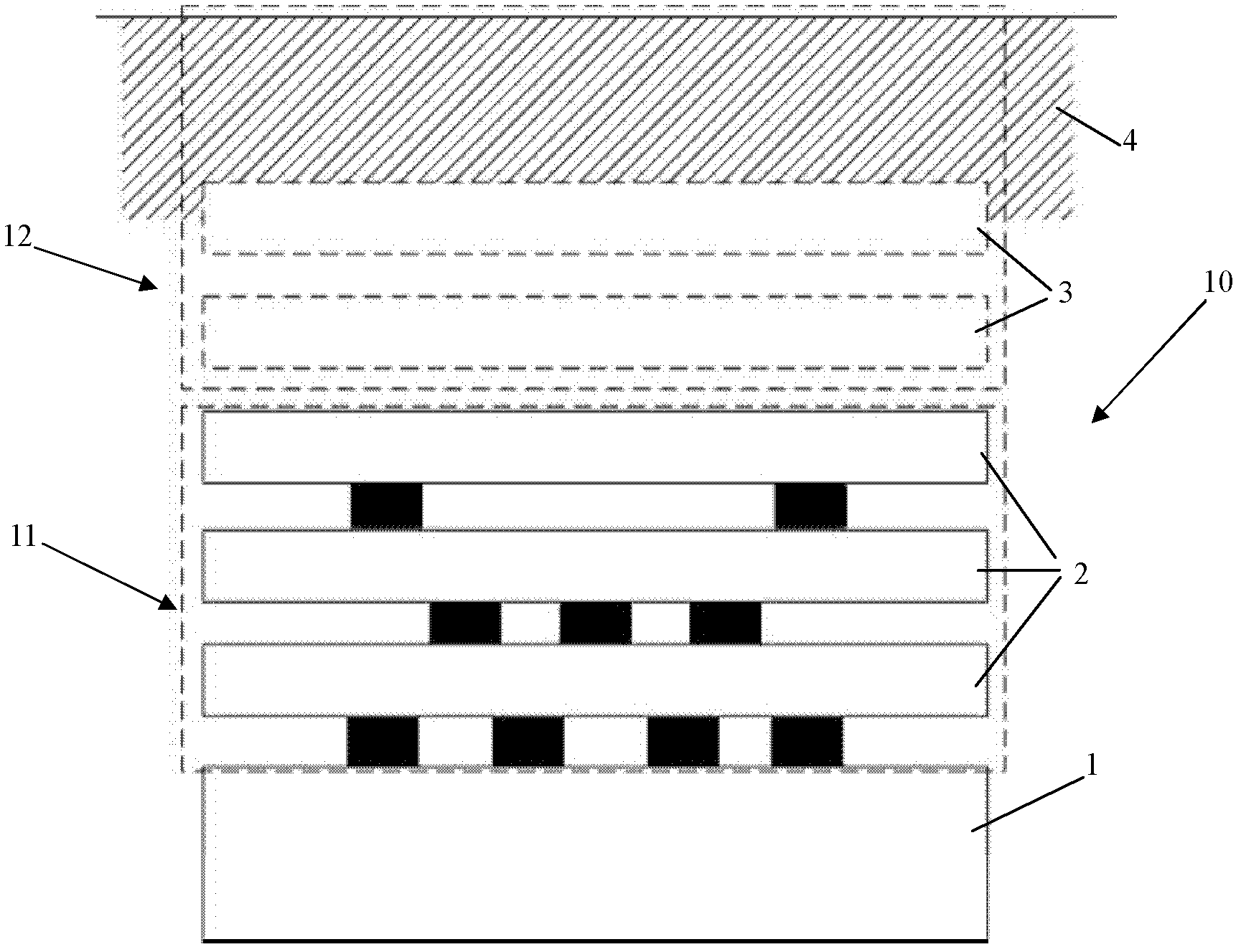

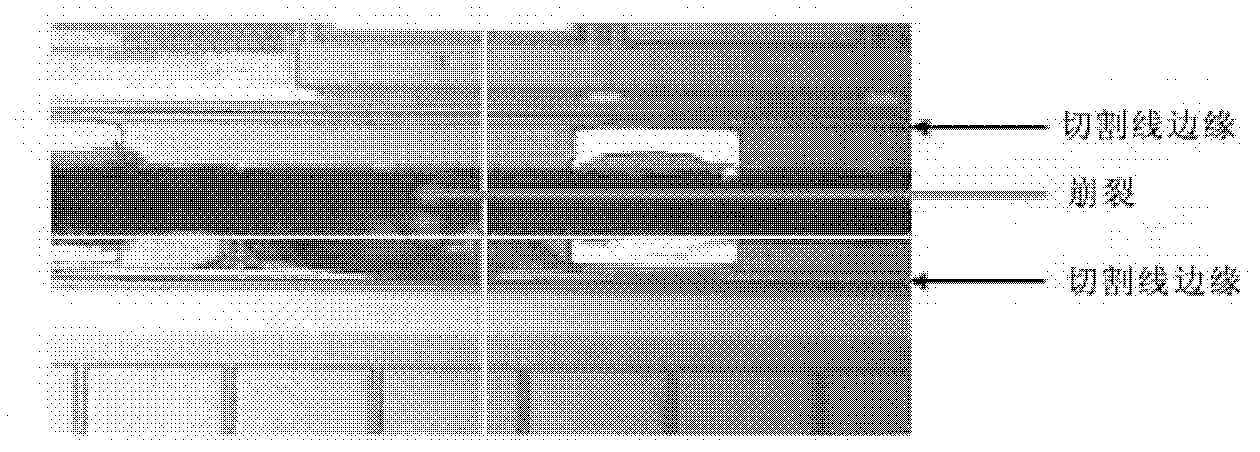

[0040] The present invention provides a wafer structure that alleviates wafer cutting stress damage, such as image 3 As shown, the wafer structure 10 includes a high-density metal layer and an oxide passivation protection layer thereon. The oxide passivation protection layer includes a metal layer 3 without pattern connection and a metal layer 3 without pattern connection The upper polishing pad layer 4; the wafer structure also includes a window 5 and a metal dummy device 6, the window 5 is arranged on the oxide passivation protection layer above the feature pattern of the wafer structure 10, and the metal dummy device ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More