Semiconductor structure and forming method thereof

A semiconductor and interconnection structure technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of low dielectric constant, affecting the electrical performance of interconnection structures, and ultra-low K dielectric layer damage And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

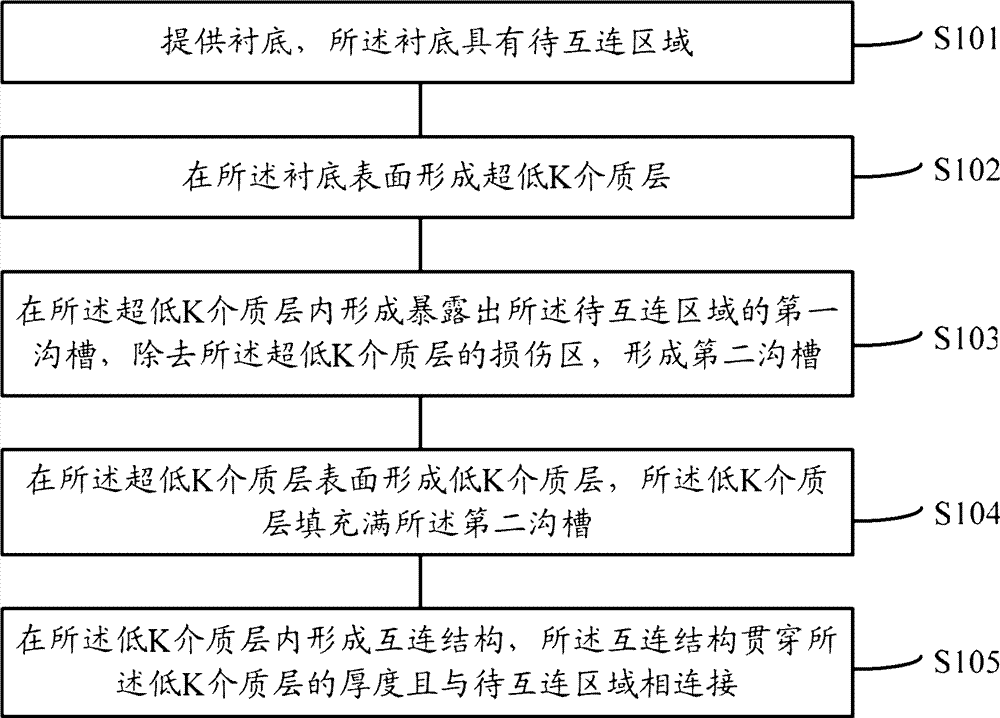

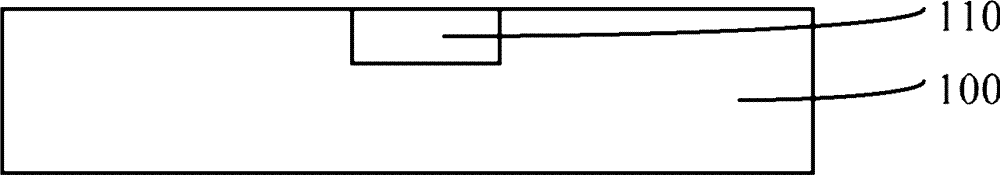

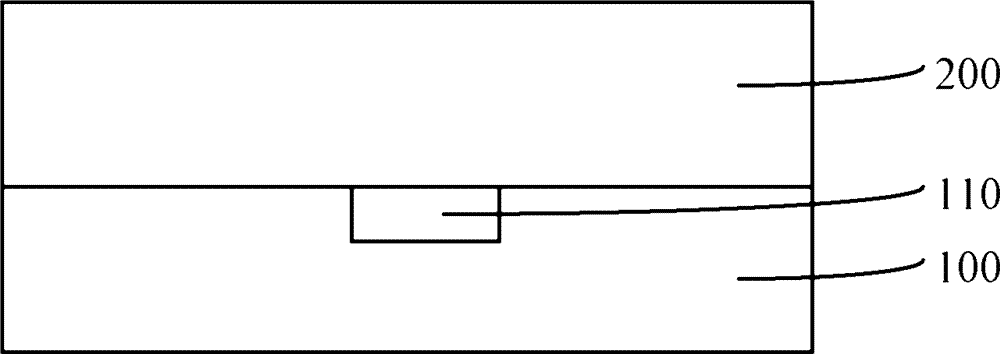

[0035] In the prior art, the ultra-low K dielectric layer is directly subjected to dry etching, chemical mechanical polishing, ashing and other processes, which can easily cause damage to the ultra-low K dielectric layer, making the dielectric constant of the ultra-low K dielectric layer If it becomes larger, the advantages of reducing the crosstalk between metal wirings and reducing the RC delay between metal wiring layers brought by the ultra-low K dielectric layer cannot be utilized. Therefore, the inventor has proposed a semiconductor structure and its formation method after research, and the formation method includes: providing a substrate, the substrate has a region to be interconnected; forming an ultra-low K dielectric layer on the surface of the substrate ; forming a first trench exposing the region to be interconnected in the ultra-low K dielectric layer, removing the damaged region of the ultra-low K dielectric layer to form a second trench; in the ultra-low K dielec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More