Field programmable gate array device dead-weight configuration device and method

A technology for configuring devices and gate arrays, which is applied to general-purpose stored program computers and architectures with a single central processing unit, etc., can solve problems such as increased weight and power consumption, reduced reliability of hardware design, and increased design complexity, etc. The effect of simple wiring and structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Embodiments of the present invention will be described below with reference to the drawings. Elements and features described in one drawing or one embodiment of the present invention may be combined with elements and features shown in one or more other drawings or embodiments. It should be noted that representation and description of components and processes that are not related to the present invention and known to those of ordinary skill in the art are omitted from the drawings and descriptions for the purpose of clarity.

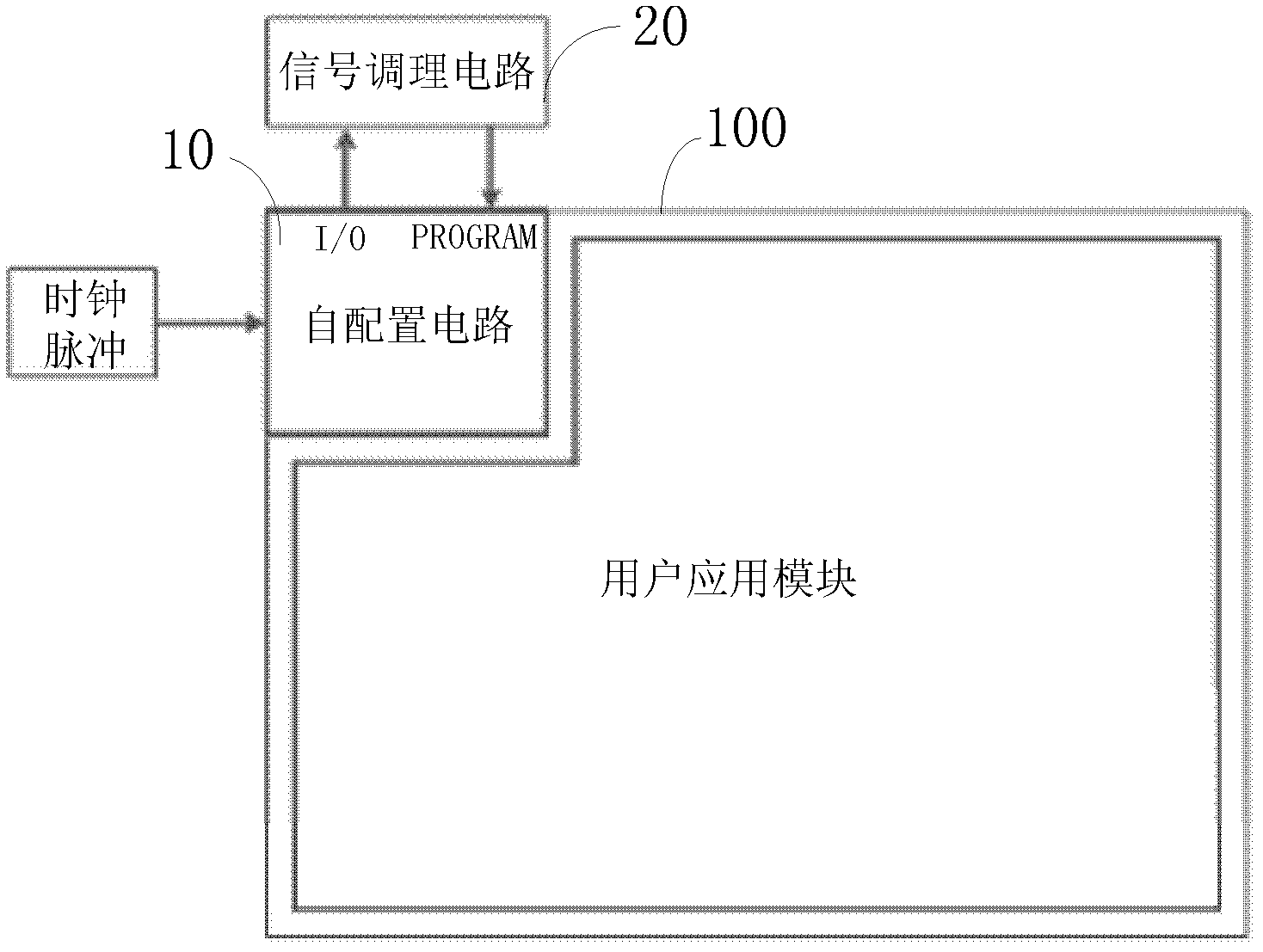

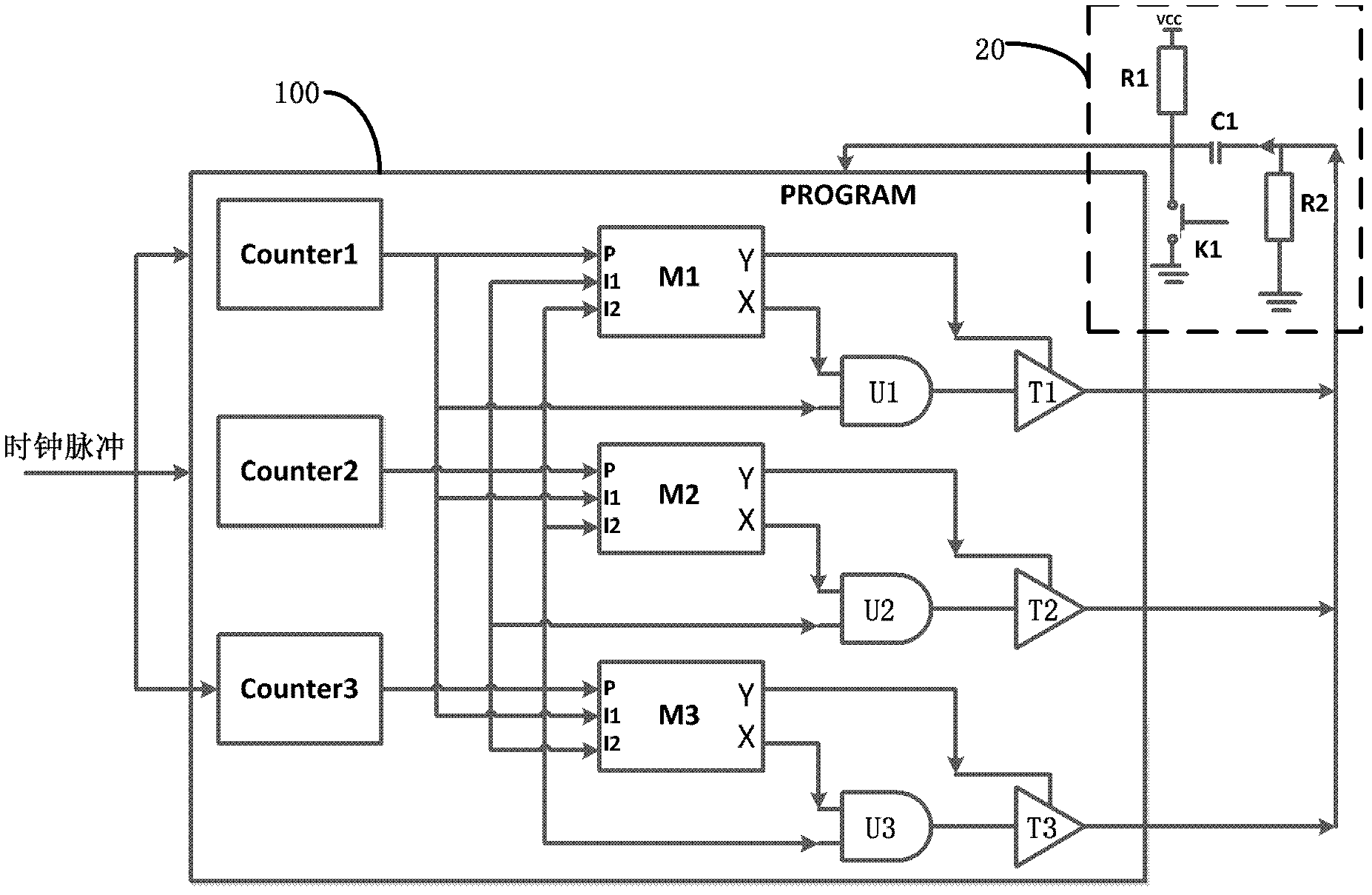

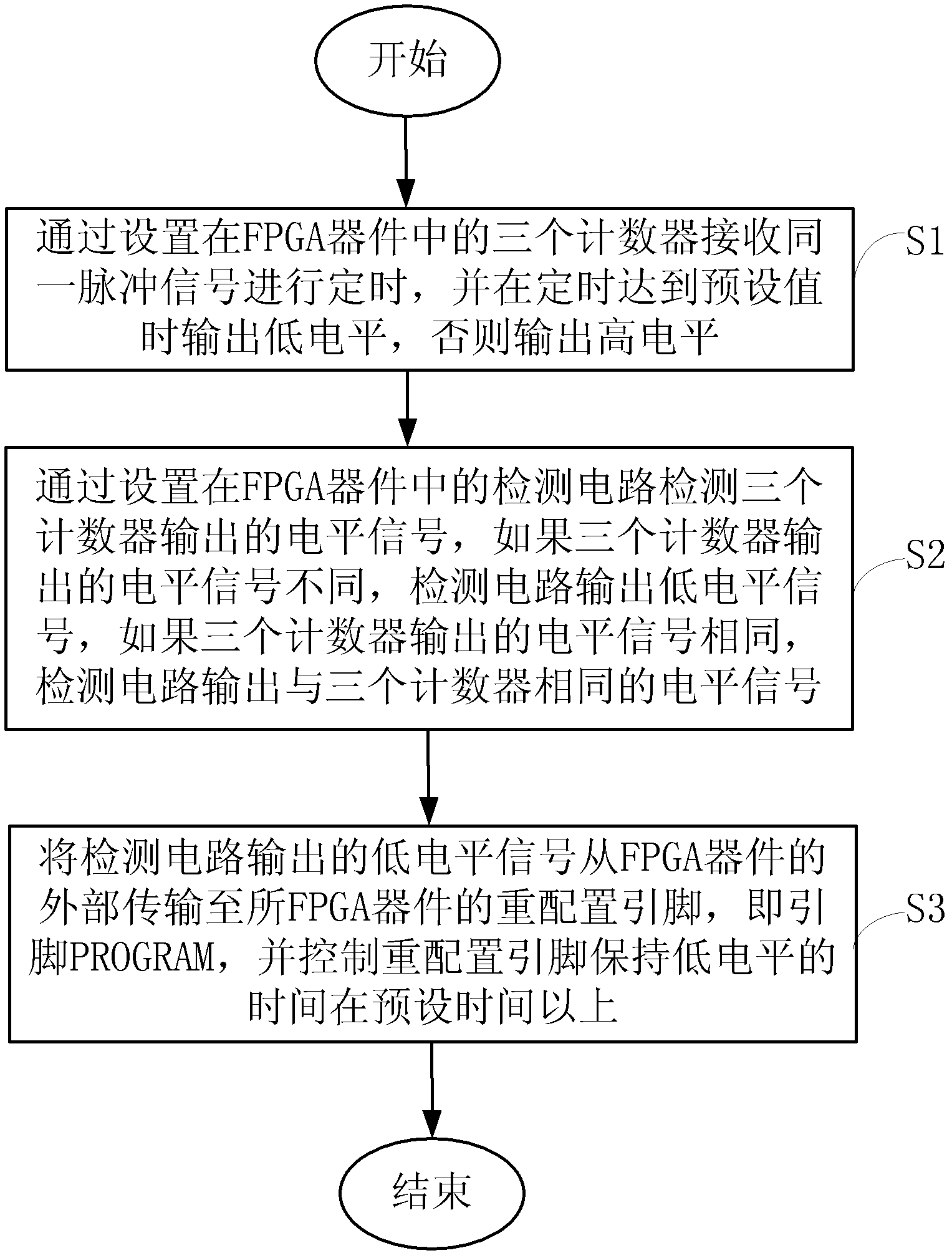

[0022] For SRAM-type FPGA devices, a reconfiguration pin is generally provided, and the FPGA device can enter the reconfiguration stage by applying a low-level pulse with a preset width to the pin. The invention provides an FPGA device self-weight configuration device. In the device of the present invention, the low-level pulse of the preset width is provided by the FPGA device to be configured, specifically, a self-configuration circuit is set in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More