Transistor and method of making the same

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of left and right damage, leakage, and affecting the electrical performance of transistors, and achieve the effect of less current leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The technical solution of the present invention will be described clearly and completely through specific embodiments below in conjunction with the accompanying drawings. Apparently, the described embodiments are only a part of the possible implementation modes of the present invention, not all of them. According to these embodiments, all other implementation manners that can be obtained by those skilled in the art without creative efforts belong to the protection scope of the present invention.

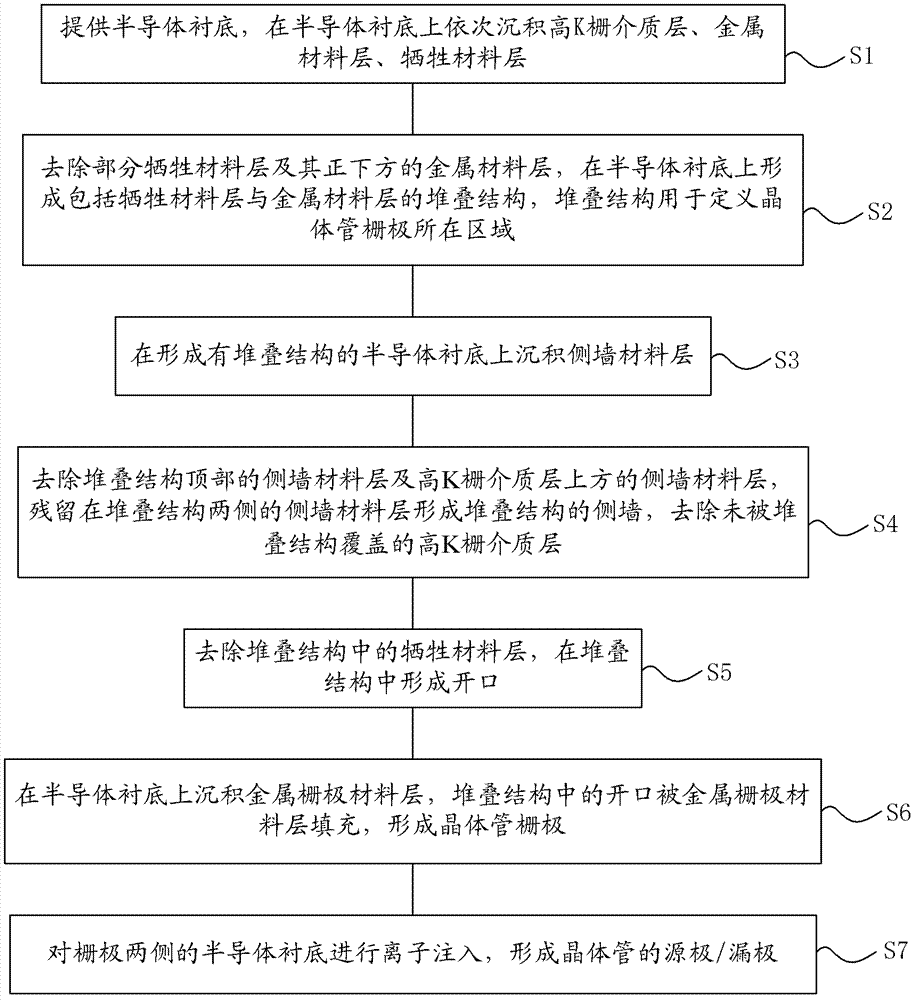

[0031] figure 2 It is a fabrication flowchart of the transistor in the embodiment of the fabrication method of the transistor of the present invention. Such as figure 2 As shown, the method includes the following steps:

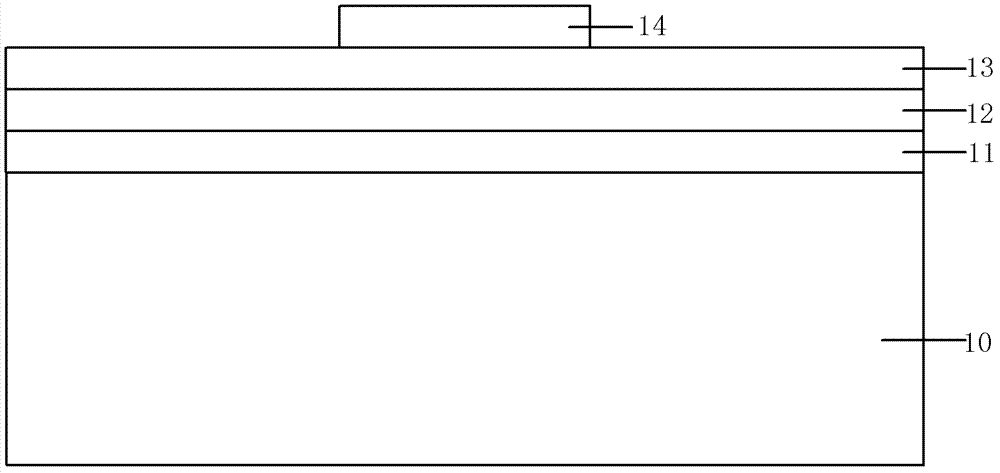

[0032] S1: Provide a semiconductor substrate, and sequentially deposit a high-K gate dielectric layer, a metal material layer, and a sacrificial material layer on the semiconductor substrate.

[0033] S2: removing part of the sacrificial material layer a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More