Creating Anisotropic Diffused Junctions in Field Effect Transistor Devices

A field-effect transistor, transistor technology, applied in semiconductor devices, electrical solid-state devices, semiconductor/solid-state device manufacturing, etc., can solve problems such as degradation of scaling device performance, device performance degradation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

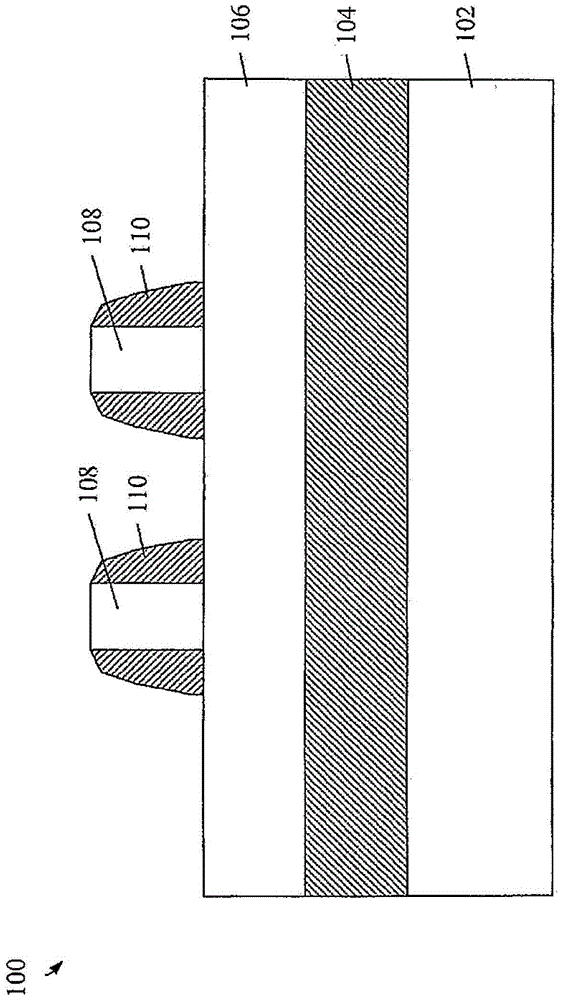

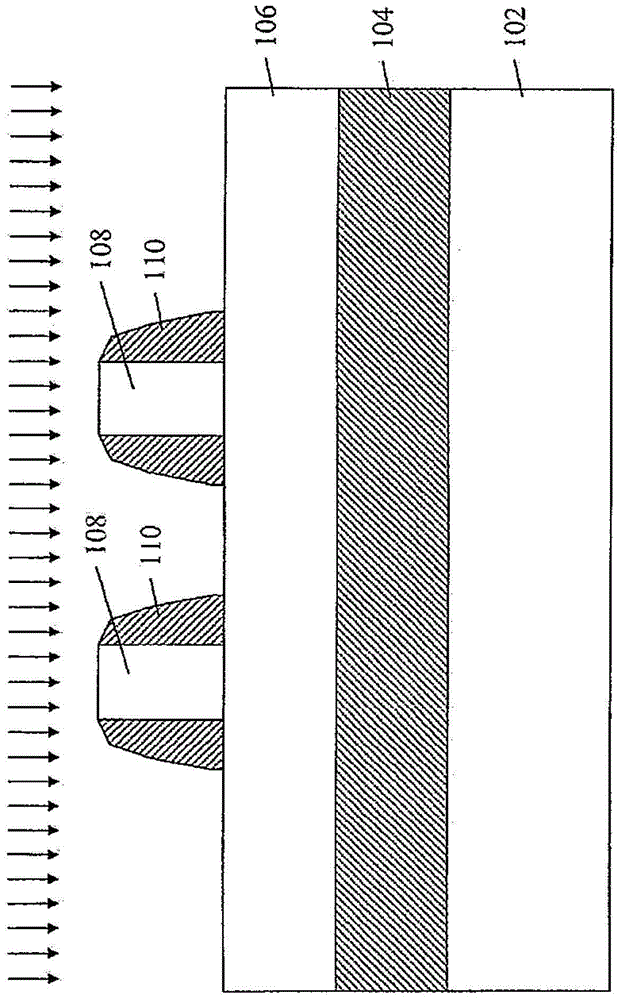

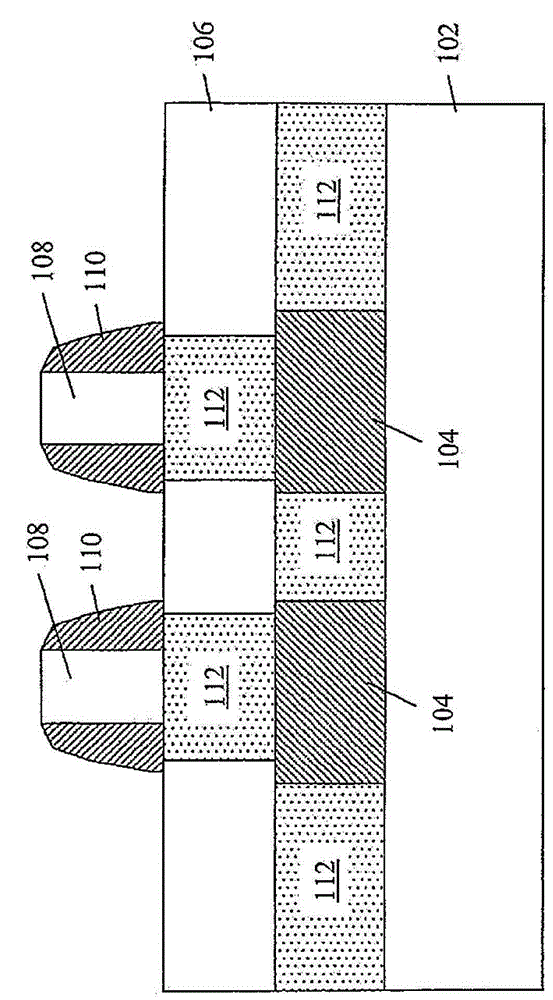

[0023] Disclosed herein are methods and structures for creating anisotropically diffused junctions in field effect transistor (FET) devices. In particular, embodiments of methods for promoting vertical diffusion of NFET and / or PFETS / D junctions while suppressing lateral diffusion are disclosed, which embodiments enable the realization of deep source / drain. Thus, such a process reduces the S / D series resistance of NFETs and / or PFETs and enables the use of thicker silicon-on-insulator (SOI) substrates, which is useful for eSiGep-type FETs (PFETs) and eSiCn-type FETs (NFETs) The stress optimization of is advantageous. In the following description, the boron difluoride (BF2) dopant in the PFET device is equivalent to the arsenic (As) dopant in the NFET device, while the boron (B) dopant in the PFET device is equivalent to the NFET device Phosphorus (P) dopant in .

[0024] In the embodiments shown below, exemplary NFET devices are shown. However, it should be understood that t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More