Dual-port peripheral configuration interface circuit

A configuration interface, dual-port technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of resource waste, cumbersome, hardware resource waste, etc., and achieve the effect of convenient rate adjustment, simple communication protocol, and simple circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

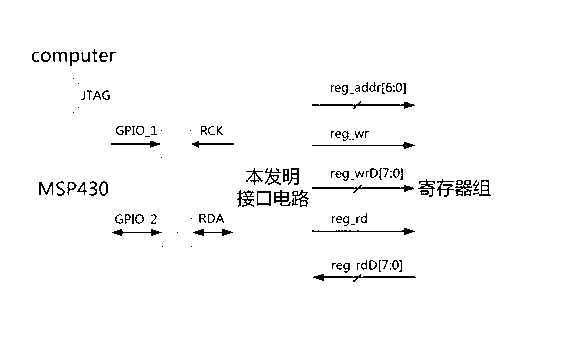

[0019] The dual-port peripheral configuration interface circuit described in the present invention can use a unified dual-port to communicate with the outside when connecting different peripherals, and the communication rate is completely determined by the external clock.

[0020] Specific embodiments of the present invention are given below in conjunction with the accompanying drawings.

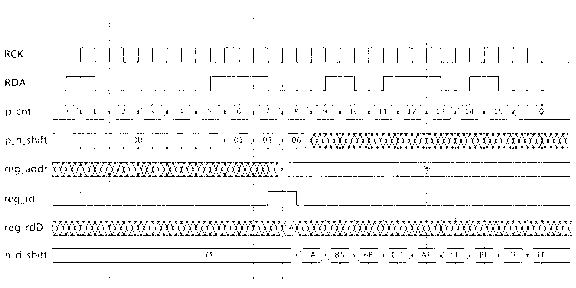

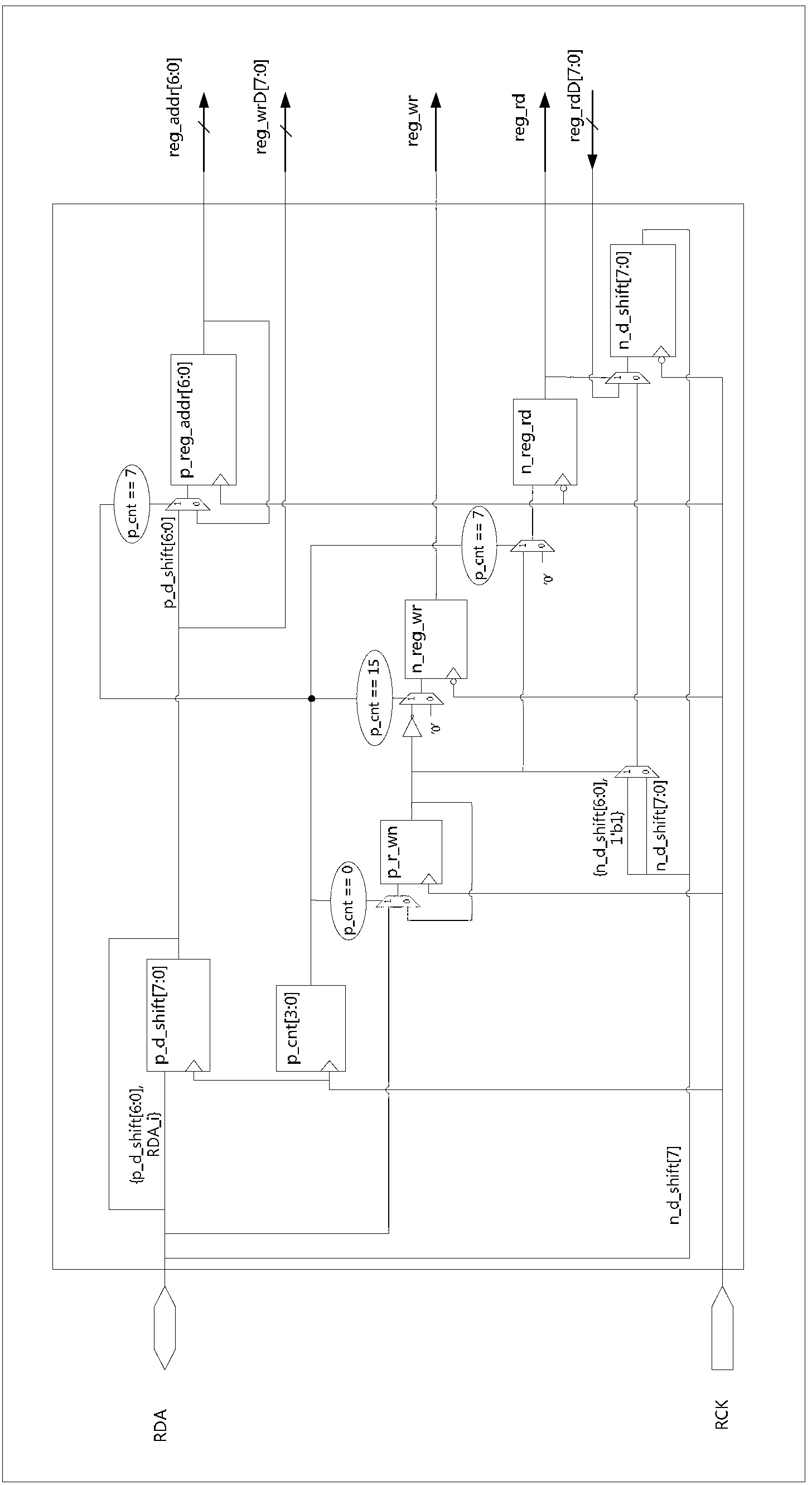

[0021] figure 1 It is the electrical schematic diagram of the interface circuit of the present invention, mainly by clock counter p_cnt[3:0], read and write judge register p_r_wn, address / data shift register p_d_shift[7:0], read data shift register n_d_shift[7:0] ], address register p_reg_addr[6:0], write enable signal generating register n_reg_wr, and read enable signal generating register n_reg_rd.

[0022] After the interface circuit design verification of this embodiment is completed, the RTL (Register Transfer Level) code is synthesized to form a netlist, and the layout is drawn corr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More