Reversible-logic-based 16-bit carry look-ahead adder

A technology of advanced carry and adder, which is applied in the field of microelectronics, can solve the problem of high power consumption of devices and achieve the effect of reducing energy loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

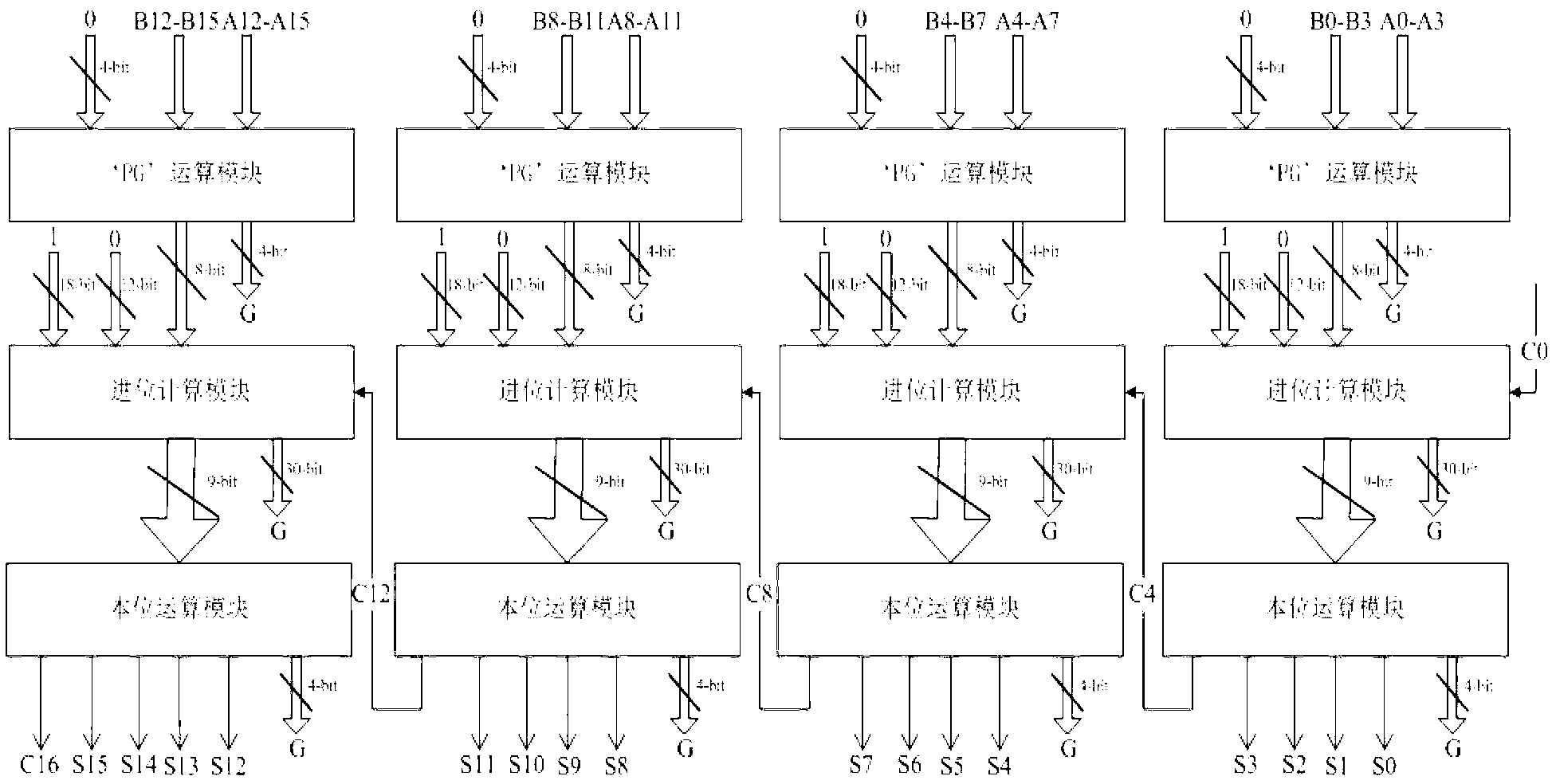

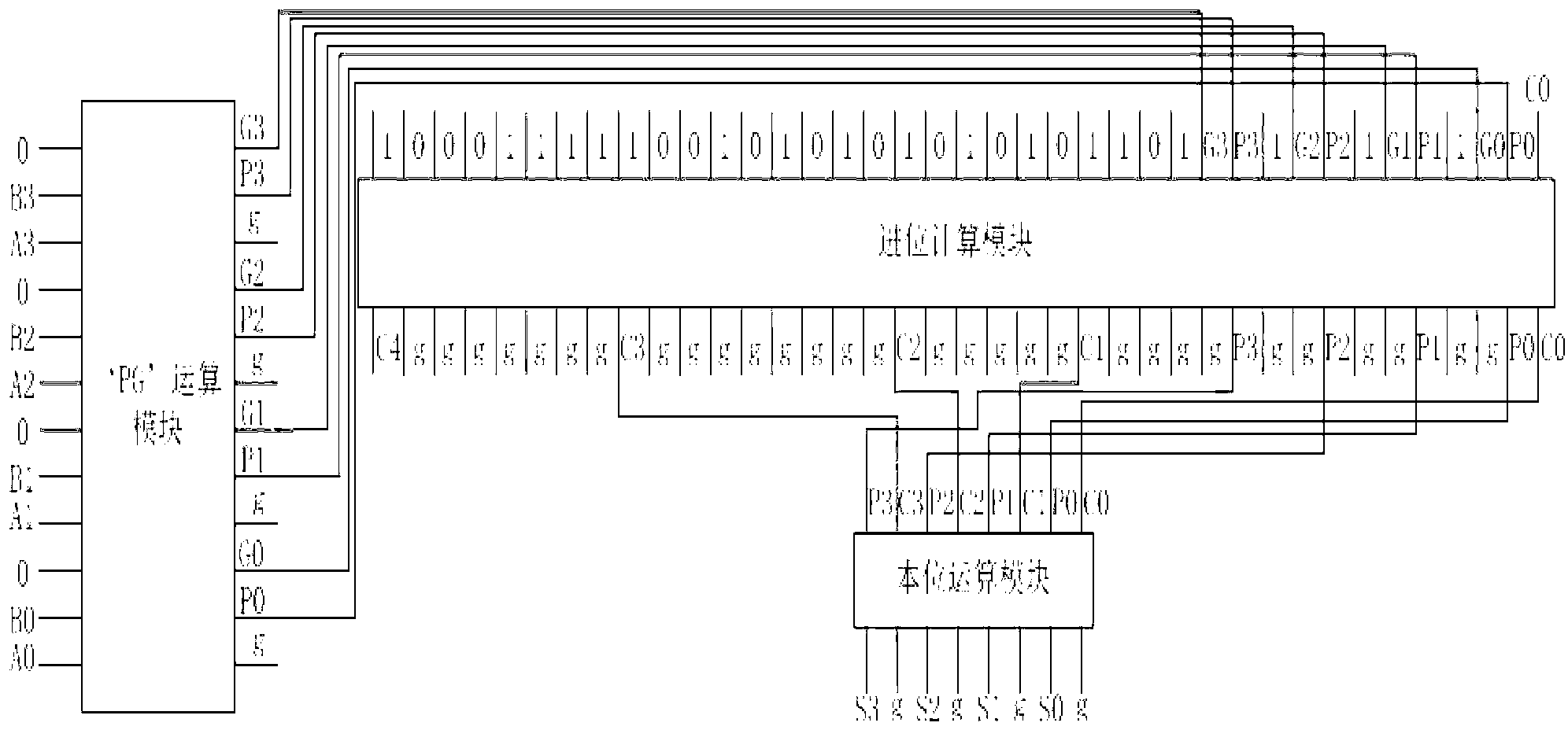

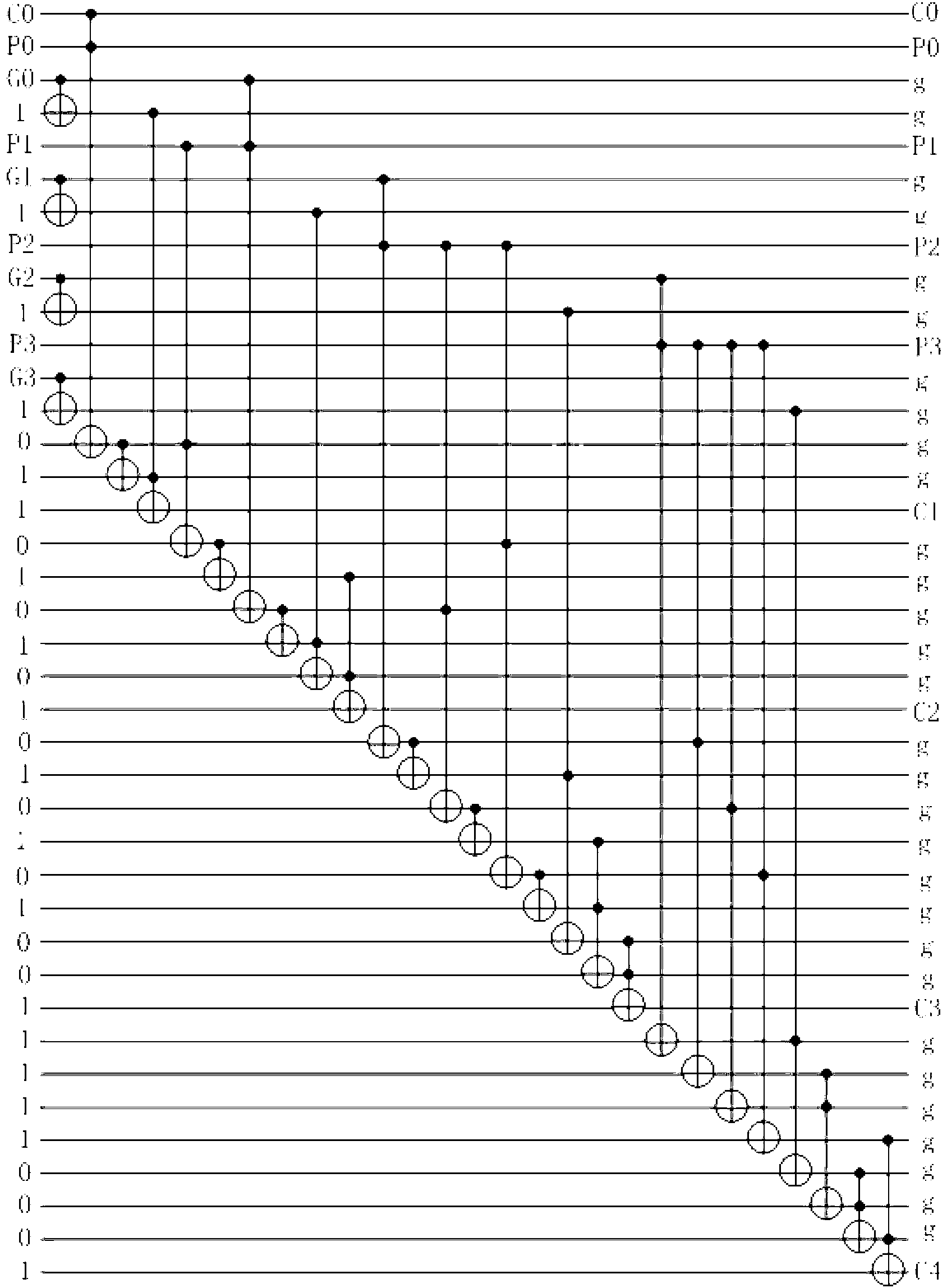

[0013] Such as figure 1 Shown is a 16-bit reversible carry-look-ahead adder. It consists of four 4-bit reversible carry-look-ahead adders cascaded, and its quantum cost is 552. The adder has 169 input terminals, of which A0-A15, B0-B15, and C0 are effective input terminals, and the remaining 136 input terminals are redundant inputs, namely the '1' input port and the '0' input port in the figure. The adder also has 169 output terminals, among which S0-S15 and C16 are effective output terminals, and the remaining 152 output terminals are garbage outputs, that is, the 'g' output ports in the figure. Such as figure 1 As shown, the 4-bit results S0-S3, S4-S7, S8-S11 and S12-S15 of the adder are calculated by the 4-bit reversible carry-look-ahead adder of each stage, and the corresponding carry output C4 of the stage , C8, C12 and C16, input three of C4, C8 and C12 (the first, second and third carry outputs) in the carry output of the current stage to the corresponding carry inpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More