Chip bonding structure and bonding method

A chip bonding and chip technology, which is used in semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., and can solve problems such as reducing the reliability of die bonding, overflowing eutectic materials, and poor electrical connection between the chip and the heat dissipation substrate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

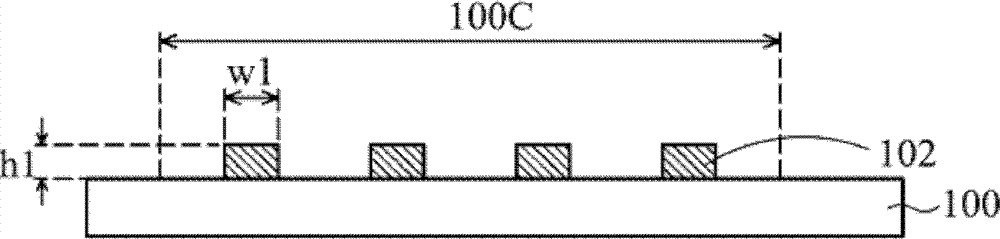

[0023] refer to Figure 1A to Figure 1C , which shows a schematic cross-sectional view of each stage of a bonding method of a chip bonding structure according to an embodiment of the present invention. Figure 1A Firstly, a substrate 100 for fixing the chip is provided, such as a printed circuit board, a ceramic substrate, a metal substrate such as copper or aluminum, the substrate 100 has a chip predetermined area 100C, and a plurality of bumps (bump) 102 are arranged on the chip predetermined area 100C. on the surface of the substrate 100. The material of the bump 102 can be gold, silver, copper, the aforementioned alloys or other metal materials. In one embodiment, a wire bonder can be used to form a plurality of metal balls in the chip predetermined area 100C of the substrate 100. Then carry out the leveling step to flatten the surface of the metal ball to form a Figure 1A A plurality of bumps 102 that are flush with the surface are shown.

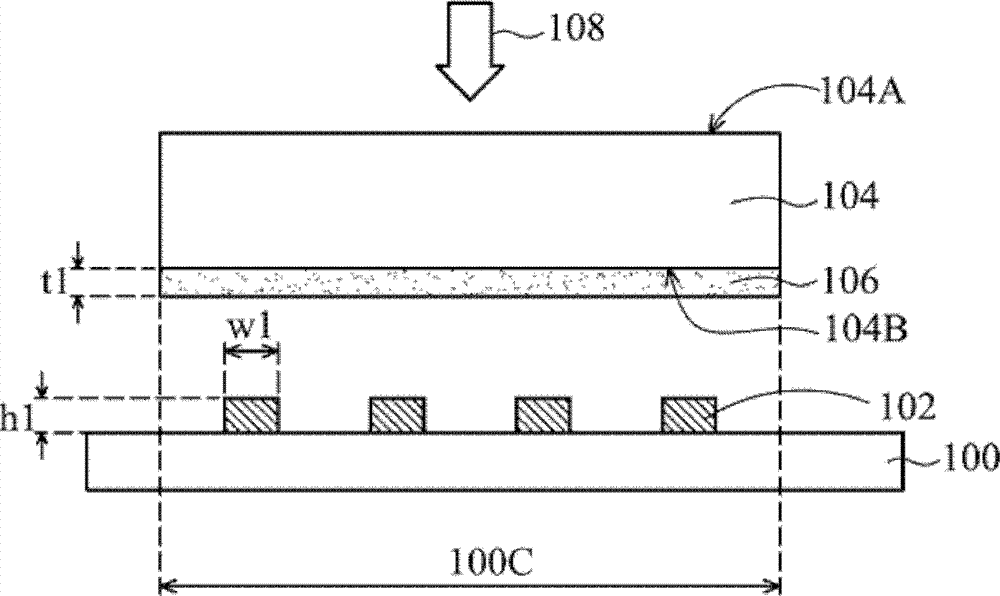

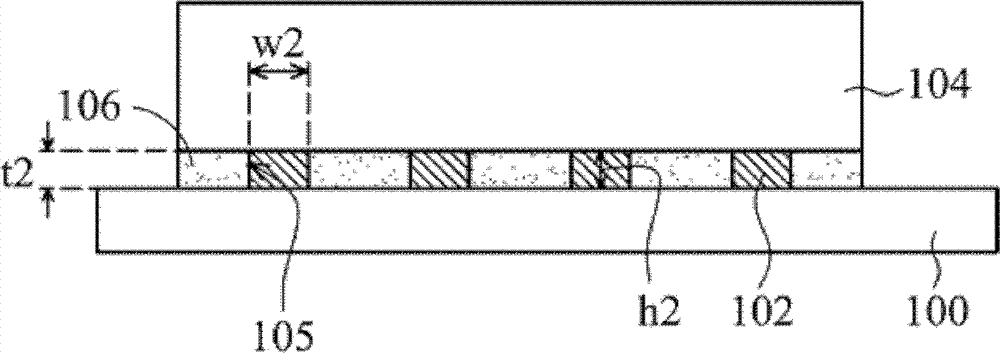

[0024] Figure 1B Provide a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More