Chip package testing device and lead frame used thereby

A test device and chip packaging technology, which is applied in semiconductor/solid-state device testing/measurement, electrical components, electric solid-state devices, etc., can solve problems such as unreasonable design size of glue injection channel, waste of lead frame materials, and affecting work efficiency. Achieve the effect of improving parallel test efficiency, increasing rigidity, and improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

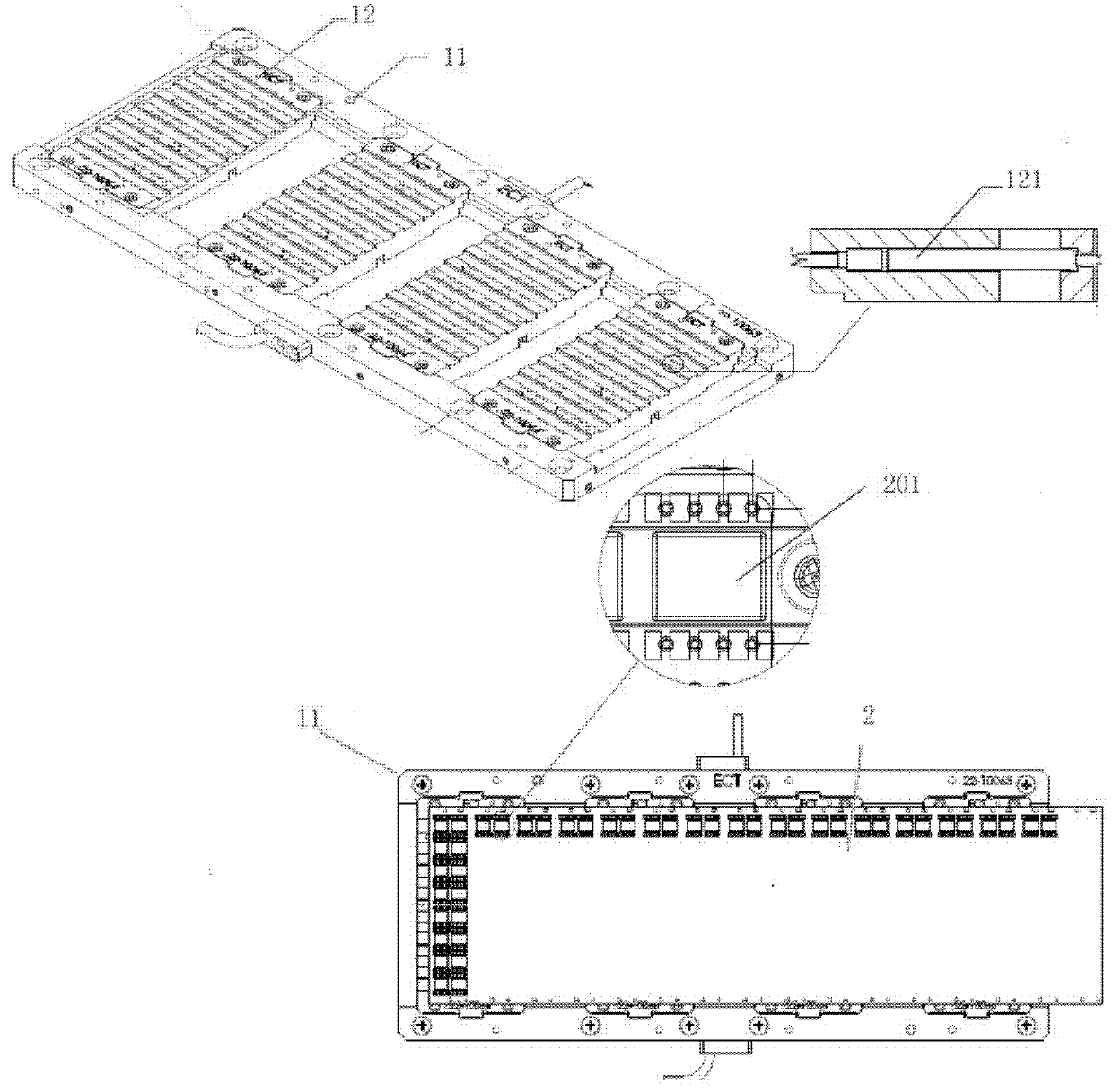

[0034] The present invention optimizes the STRIP TEST test method by developing a chip package test device with a higher density of package units and its dedicated lead frame, that is, it adopts two-dimensional code recognition technology or barcode technology, network technology and database technology, and ensures the test process. The safety, intelligence and efficiency of the test greatly improve the dependence of the test on manual operation and the potential mixing risks associated with it; at the same time, in order to give full play to the efficiency of the STRIP TEST system, the design of the lead frame is specially improved, which doubles the The unit frame encapsulates the density and number of units.

[0035] The specific embodiment of the present invention will be further described in detail below in conjunction with the accompanying drawings.

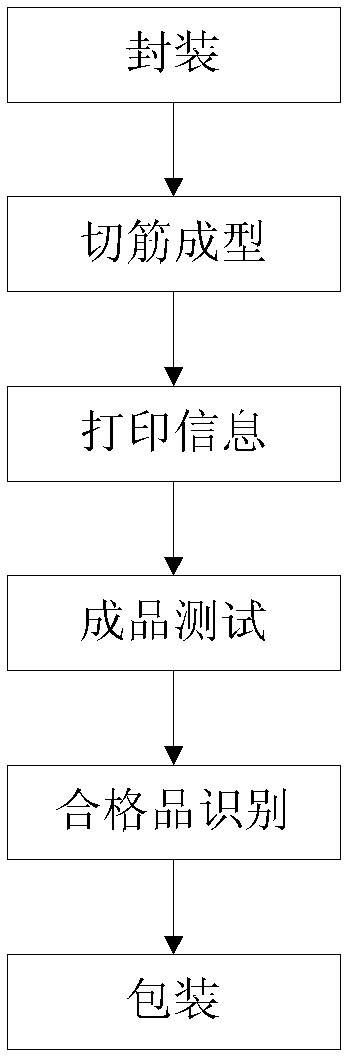

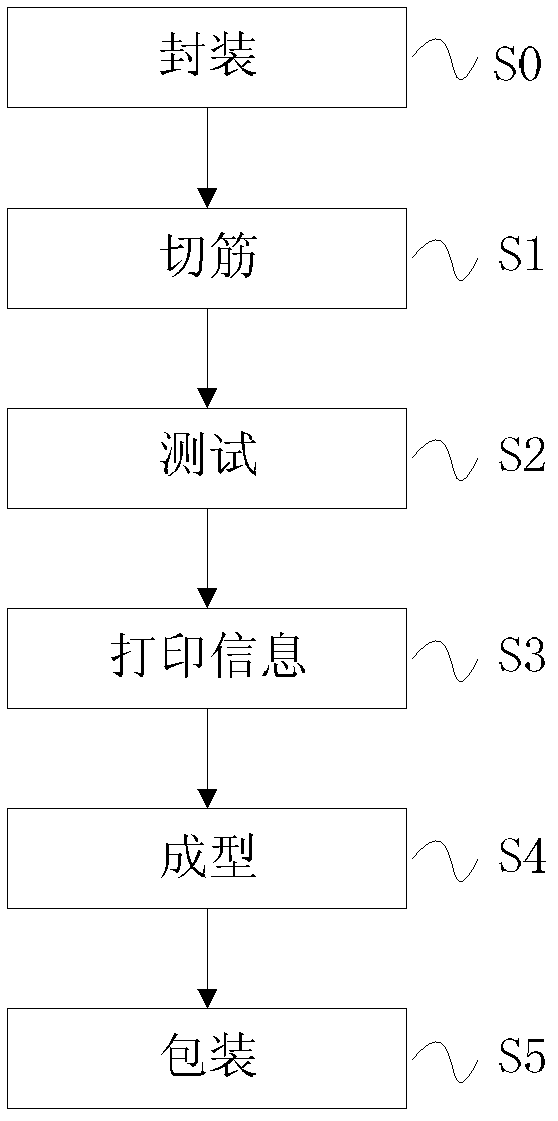

[0036] It should be noted that, compared with the traditional packaging and testing process, STRIP TEST puts more emphas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com