Architecture guided optimal system precision definition algorithm for custom integrated circuit

An integrated circuit, the best technology, applied in the field of automatic selection of fixed-point expression method or floating-point expression method, can solve the problem of sub-optimal expression format, system designer can't control exponent or mantissa, etc., to achieve power and The effect of improved performance characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

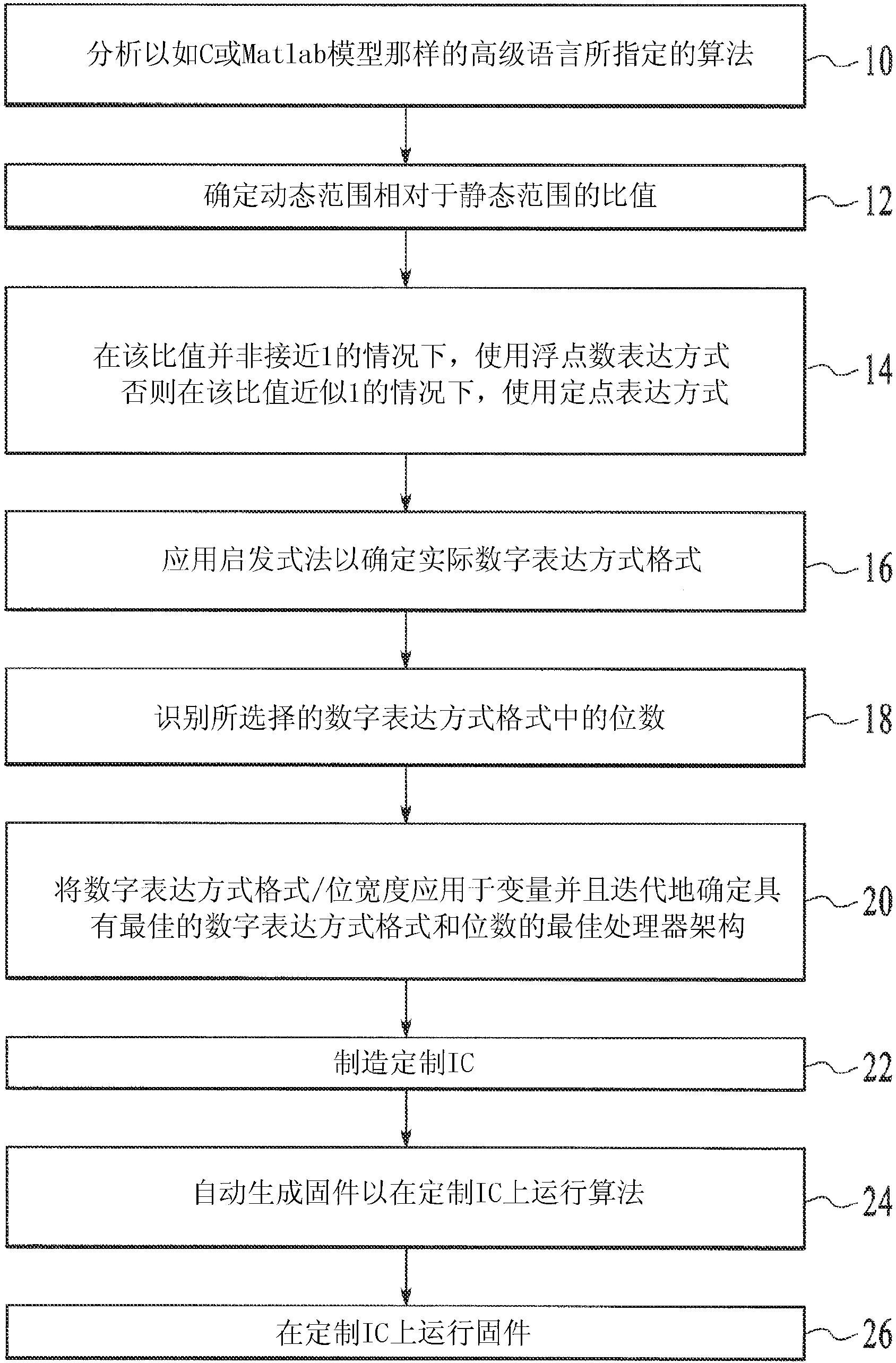

[0018] Figure 2A Example system operations for automatically generating custom ICs with automatic digital representation format selection are shown. The system automatically designs and generates custom integrated circuits based on an algorithmic process or code as input and using highly automated tools that require little human involvement.

[0019] now turn to reference Figure 2A , the process receives and analyzes an algorithm (10) specified in a high-level language such as C or Matlab model. In one embodiment, it is assumed that a first version of the product is developed using floating point representation. This could be any type of floating point representation but typical embodiments may use 32 bit IEEE floating point representation. The process entails identifying one or more of the following with the product's developer or system architecture.

[0020] Parameters in floating point format to optimize.

[0021] Working C code or model of the system.

[0022] Rea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More