TSV (through silicon via) Trench arrangement method in 3D integrated circuit

A technology of integrated circuits and layout methods, applied in the field of automatic layout, to meet the requirements of process spacing constraints and achieve the effect of compact layout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

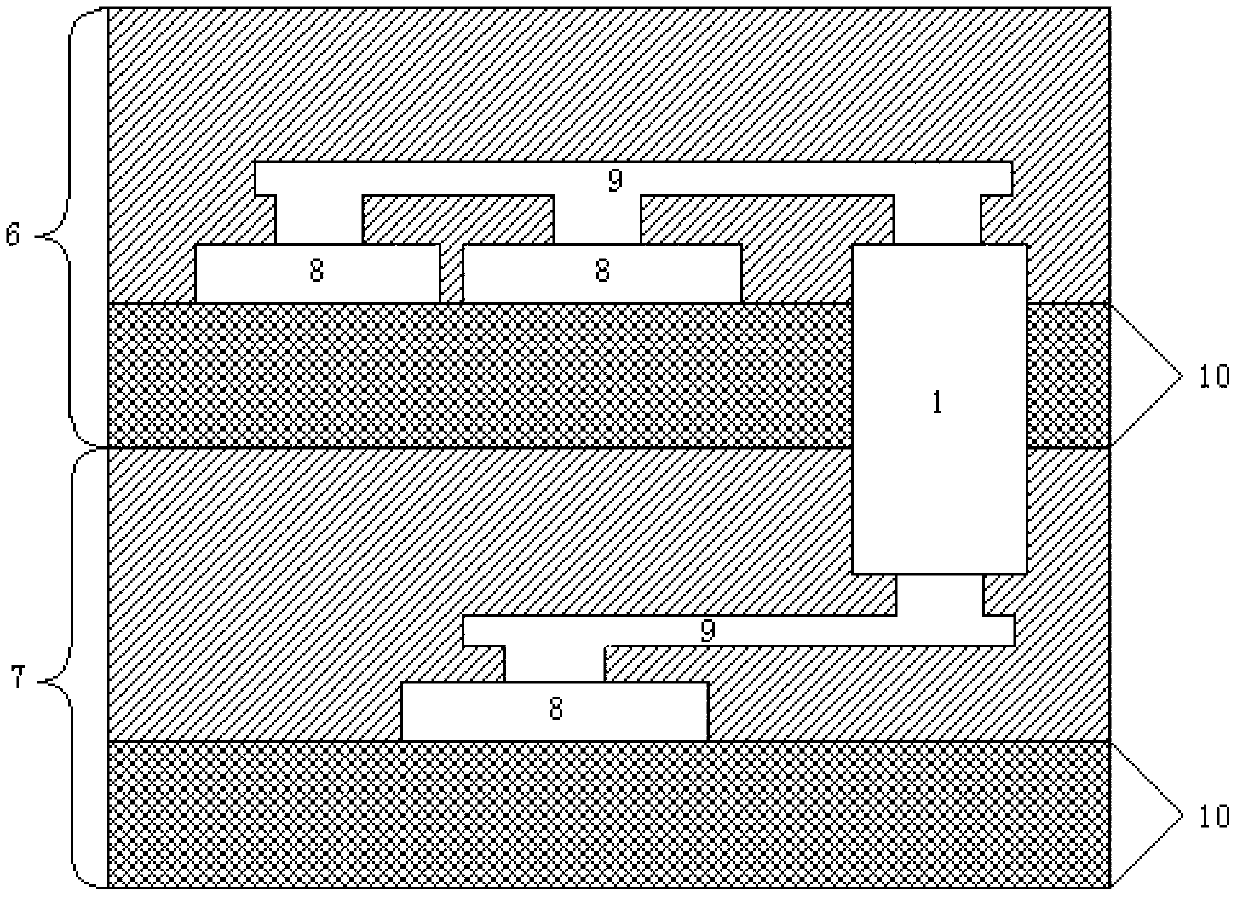

[0044] A schematic diagram of the structure of a 3D integrated circuit such as figure 1 shown. A 3D circuit is a structure in which multi-layer 2D chips are stacked in the vertical direction, and the structural relationship between any two layers of adjacent chips is as follows: figure 1 The top chip 6 and the bottom chip 7, the standard unit 8 in the chip is the basic structure for the storage and transmission of integrated circuit signals, and the metal interconnection line 9 connects the standard unit to complete the interconnection on the single-layer chip. TSV1 interconnection is used for cross-layer interconnection of standard cells to complete cross-layer transmission of signals. The structure of TSV1 is a via hole passing through two adjacent layers of the 3D integrated circuit chip.

[0045] The present invention is dedicated to optimizing the layout where TSV positions have been preliminarily determined, so that the spacing of all TSVs meets the requirements of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com