Methods for forming NMOS transistor and MOS transistor

A MOS transistor, transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as limited stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

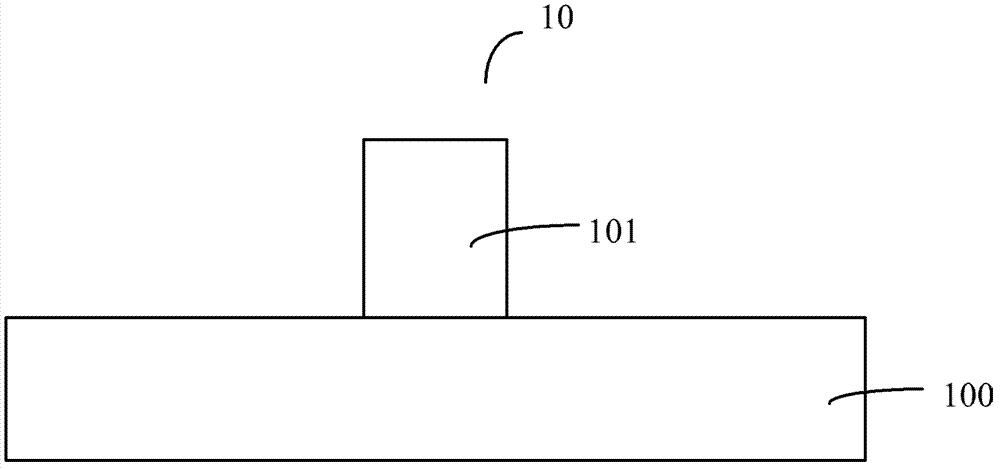

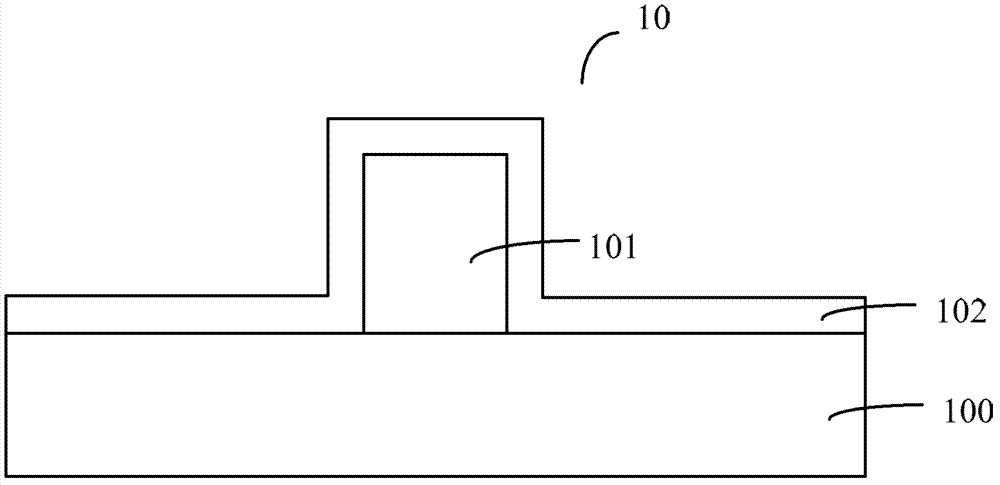

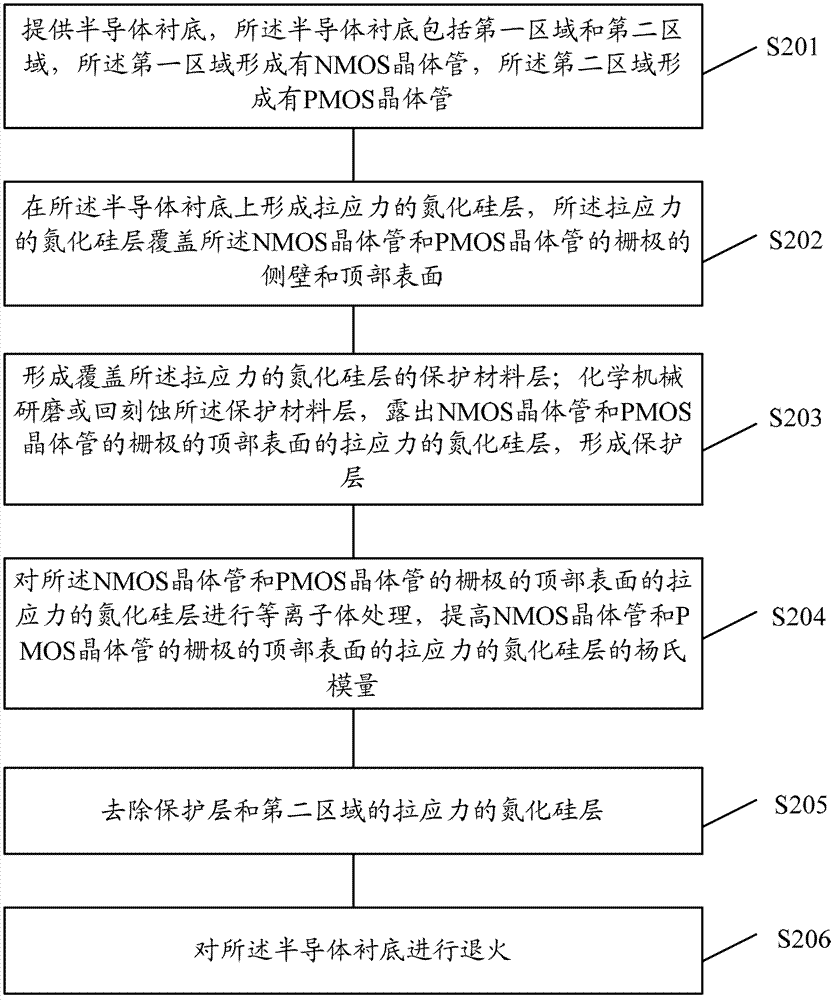

[0058] Currently, after the stress layer is formed, the semiconductor substrate needs to be annealed so that the stress in the stress layer is transferred to the channel region of the transistor. Expansion in the vertical direction causes the stress layer to deform, resulting in a reduction in the stress applied by the stress layer to the channel region, especially during the formation of the NMOS transistor, the silicon nitride layer of tensile stress is applied to the channel of the NMOS transistor The stress reduction in the region is particularly severe.

[0059] In order to solve the above problems, the inventor proposes a method for forming an NMOS transistor and a MOS transistor, wherein the method for forming the NMOS transistor includes: providing a semiconductor substrate on which an NMOS transistor is formed; A tensile-stressed silicon nitride layer is formed on the substrate, and the tensile-stressed silicon nitride layer covers the gate sidewall and top surface of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Stress | aaaaa | aaaaa |

| Stress | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More