Capacitor structure and its manufacturing method

A manufacturing method and capacitor technology, applied in the direction of electrical solid devices, semiconductor/solid device manufacturing, circuits, etc., can solve the problems that cannot meet the requirements of product design, achieve the effect of increasing the capacitance per unit area and saving the overall area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Please refer to figure 2 , Figure 3a-3e as well as Figure 4a~4c , this embodiment proposes a method for manufacturing a metal-polysilicon-polysilicon (metal-poly-poly, M-PIP) capacitor, including:

[0045] Step S100: providing a semiconductor substrate 310, on which a shallow trench isolation layer 320 is disposed; wherein, the semiconductor substrate 310 is a silicon substrate, and the shallow trench isolation layer 320 is silicon dioxide ,Such as Figure 3a shown;

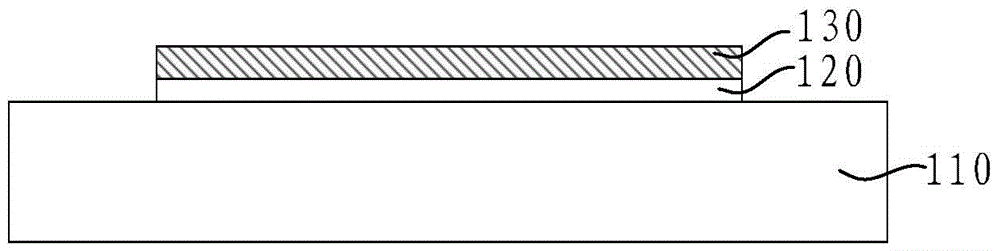

[0046] Step S200: sequentially forming the first dielectric layer 330 and the first polysilicon layer 340 on the shallow trench isolation layer 320, and then etching the first polysilicon layer 340 and the first dielectric layer 330 to expose The shallow trench isolation layer 320 and the semiconductor substrate 310, such as Figure 3a and Figure 4a shown;

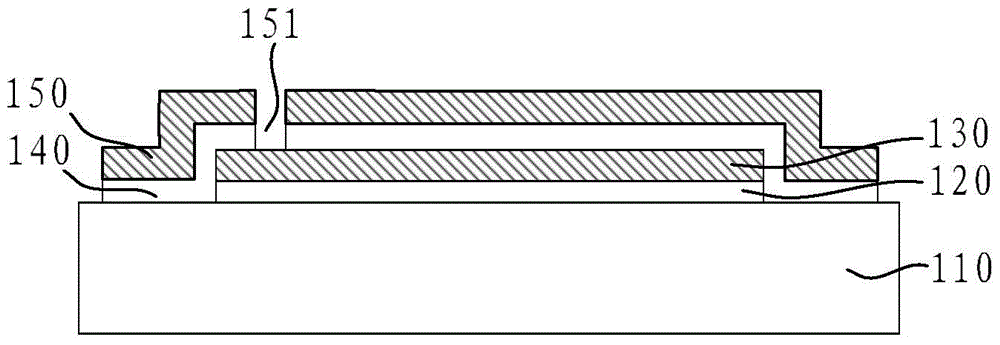

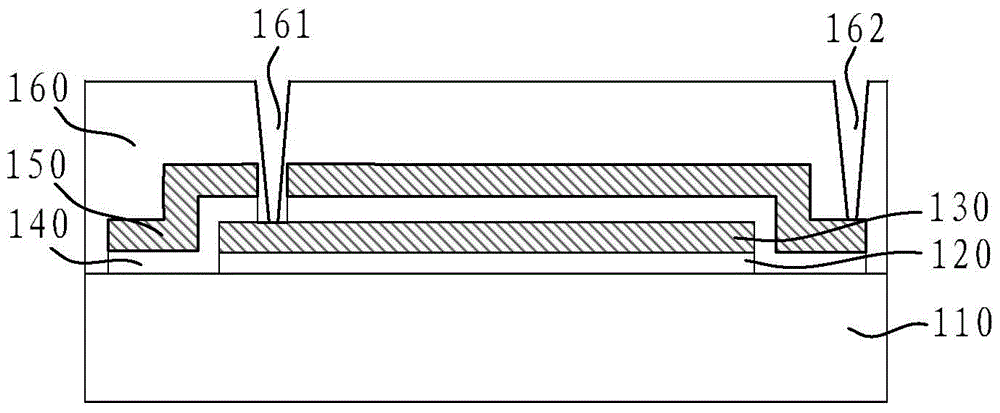

[0047]Step S300: sequentially forming a second dielectric layer 350 and a second polysilicon layer 360 on the shallow trench isolation laye...

Embodiment 2

[0059] Please refer to figure 2 And 5a-5e, this embodiment proposes a method for manufacturing a metal-poly-poly-substrate (M-PPS) capacitor, including:

[0060] Step S100: providing a semiconductor substrate 410, on which a plurality of shallow trench isolation layers 420 are provided; wherein, the semiconductor substrate 410 is a silicon substrate, and the shallow trench isolation layers 420 are two Silicon oxide, such as Figure 5a shown;

[0061] Step S200: sequentially forming a first dielectric layer 430 and a first polysilicon layer 440 on the semiconductor substrate 410 between the two shallow trench isolation layers 420, and then etching the first polysilicon layer 440 and the The first dielectric layer 430 exposes the semiconductor substrate 410 and the shallow trench isolation layer 420, such as Figure 5a shown; wherein, the material of the first dielectric layer 430 is silicon dioxide or silicon nitride;

[0062] Step S300: sequentially forming a second diele...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More