Forming method of semiconductor structure and forming method of MOS transistor

A MOS transistor and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high doping concentration, in-situ doping, limitations, etc., achieve high concentration uniformity, improve electrical performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

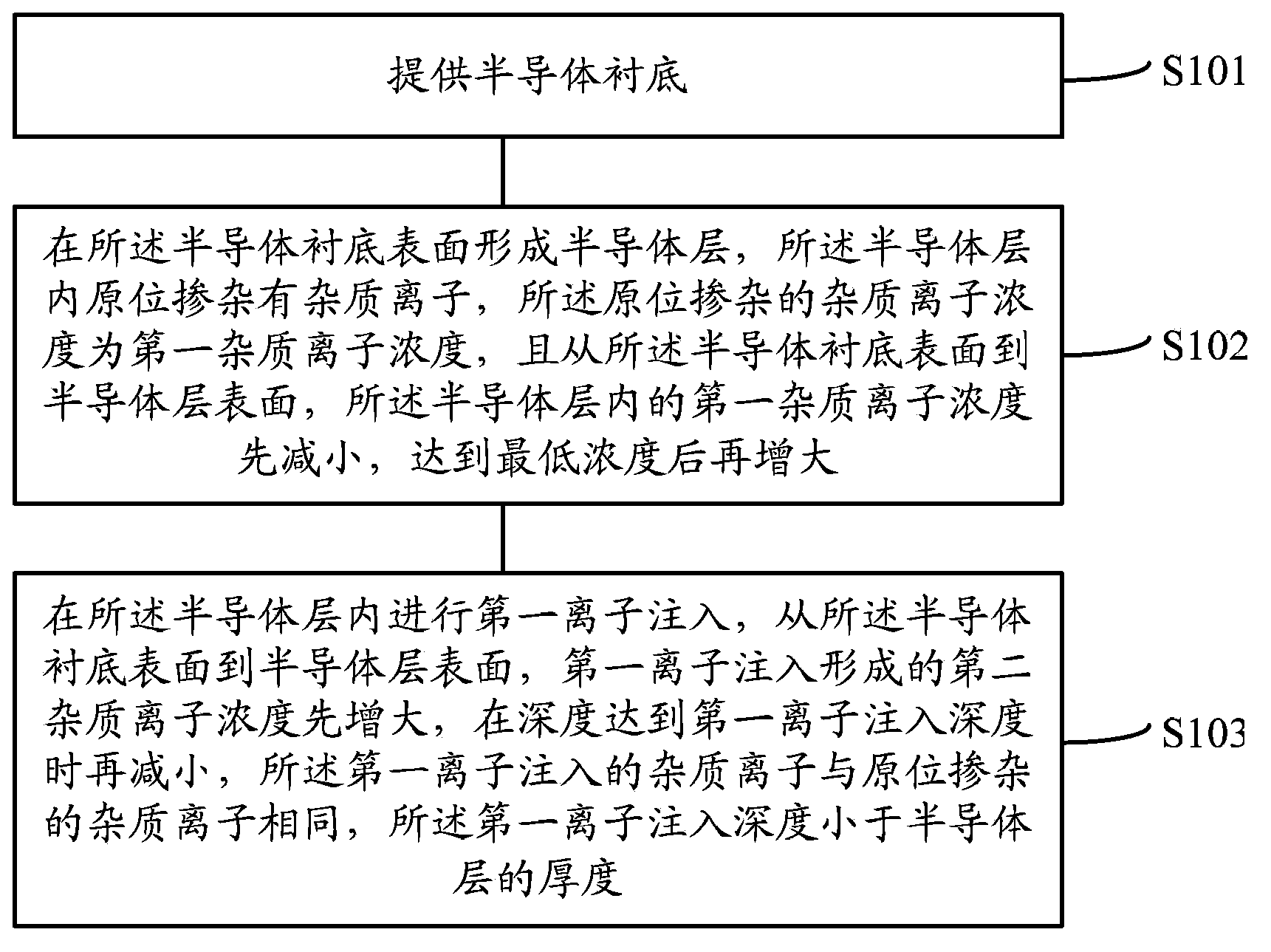

[0046] The first embodiment of the present invention firstly provides a method for forming a semiconductor structure, please refer to figure 2 , is a schematic flowchart of a method for forming a semiconductor structure according to an embodiment of the present invention, specifically including:

[0047] Step S101, providing a semiconductor substrate;

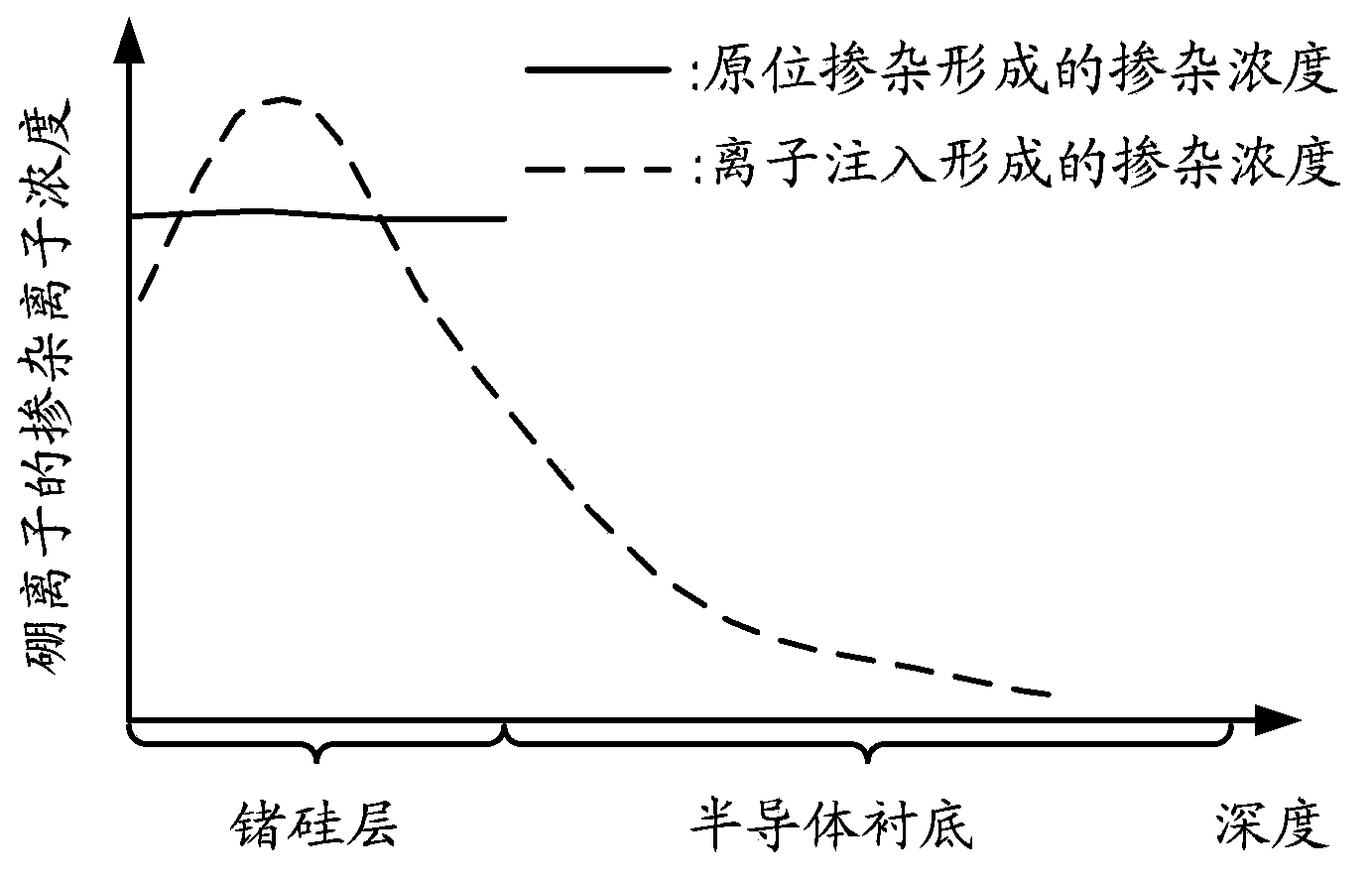

[0048] Step S102, forming a semiconductor layer on the surface of the semiconductor substrate, the semiconductor layer is in-situ doped with impurity ions, the concentration of the in-situ doped impurity ions is a first concentration of impurity ions, and from the semiconductor substrate From the bottom surface to the surface of the semiconductor layer, the concentration of the first impurity ion in the semiconductor layer decreases first, and then increases after reaching the lowest concentration;

[0049] Step S103, performing the first ion implantation in the semiconductor layer, from the surface of the semiconductor subst...

no. 2 example

[0066] The second embodiment of the present invention also provides a method for forming a MOS transistor, please refer to Figure 6 , is a schematic flowchart of a method for forming a MOS transistor according to an embodiment of the present invention, specifically including:

[0067] Step S201, providing a semiconductor substrate, and forming a gate structure on the surface of the semiconductor substrate;

[0068] Step S202, forming trenches in the semiconductor substrate on both sides of the gate structure;

[0069] Step S203, filling the trench with a stress material to form a source / drain region, the source / drain region is in-situ doped with impurity ions, and the concentration of the in-situ doped impurity ions is the third impurity ion Concentration, and from the bottom surface of the source / drain region to the surface of the source / drain region, the concentration of the third impurity ion in the source / drain region decreases first, and then increases after reaching th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More