Semi-blind oversampling clock data recovery circuit with high locking range

A technology for clock data recovery and locking range, which is applied in the direction of electrical components, automatic power control, etc., can solve the problem of low locking range, and achieve the effect of improving the locking range, increasing the locking range, and reducing the workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to further illustrate the advantages of the present invention and the specific technical means adopted, the specific implementation and circuit structure of the present invention will be described in detail below in conjunction with the drawings.

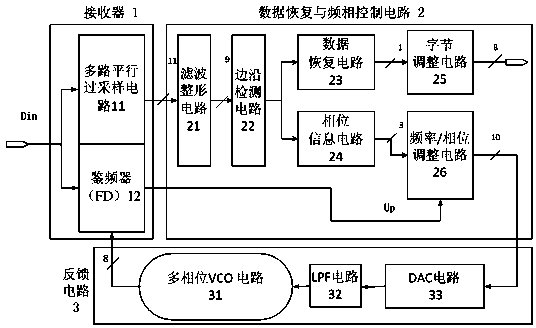

[0019] figure 1 The semi-blind oversampling clock data recovery circuit with a high locking range is shown, which includes a receiver 1 composed of multiple parallel oversampling circuits 11 and a frequency discriminator FD12; a filter shaping circuit 21, an edge detection circuit 22, The data recovery and frequency phase control circuit 2 composed of data recovery circuit 23, phase information circuit 24, byte adjustment circuit 25 and frequency / phase adjustment circuit 26, the feedback circuit composed of multi-phase VCO circuit 31, LPF circuit 32 and DAC circuit 33 Circuit 3.

[0020] The input terminal of the frequency discriminator FD12 is connected to the input signal Din, the output signal up is connected to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More