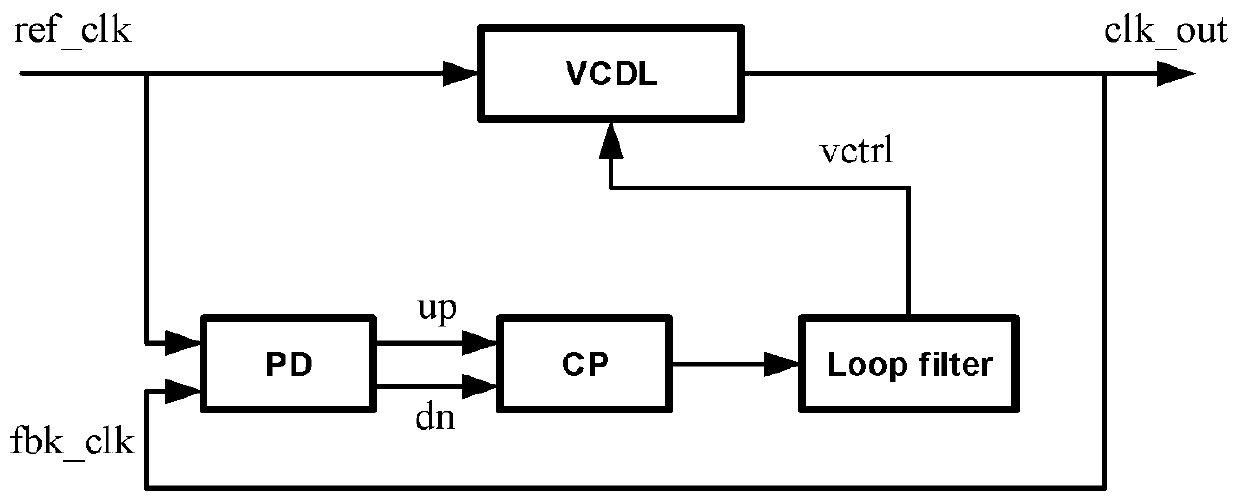

Phase discrimination circuit of delay phase-locked loop

A delay-locked loop and delay circuit technology, which is applied in the field of phase-detection circuits of delay-locked loops, and can solve the problems of inability to lock and small delay range of voltage-controlled delay chains.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

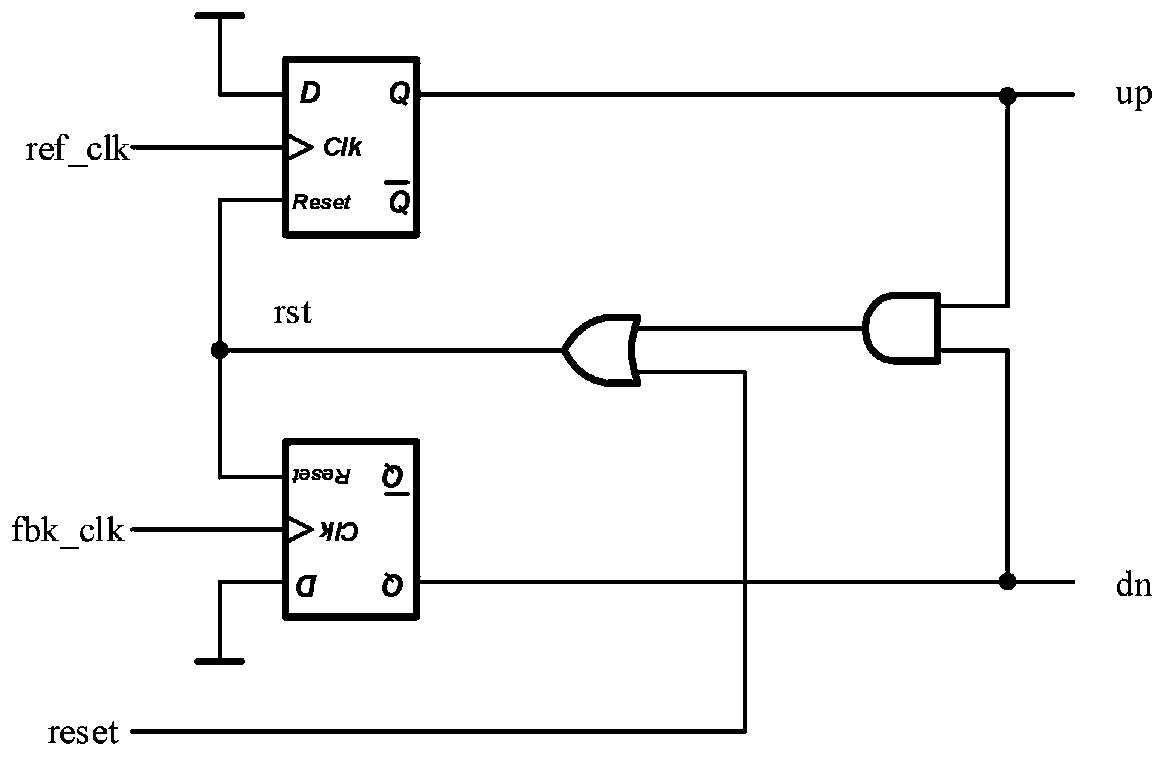

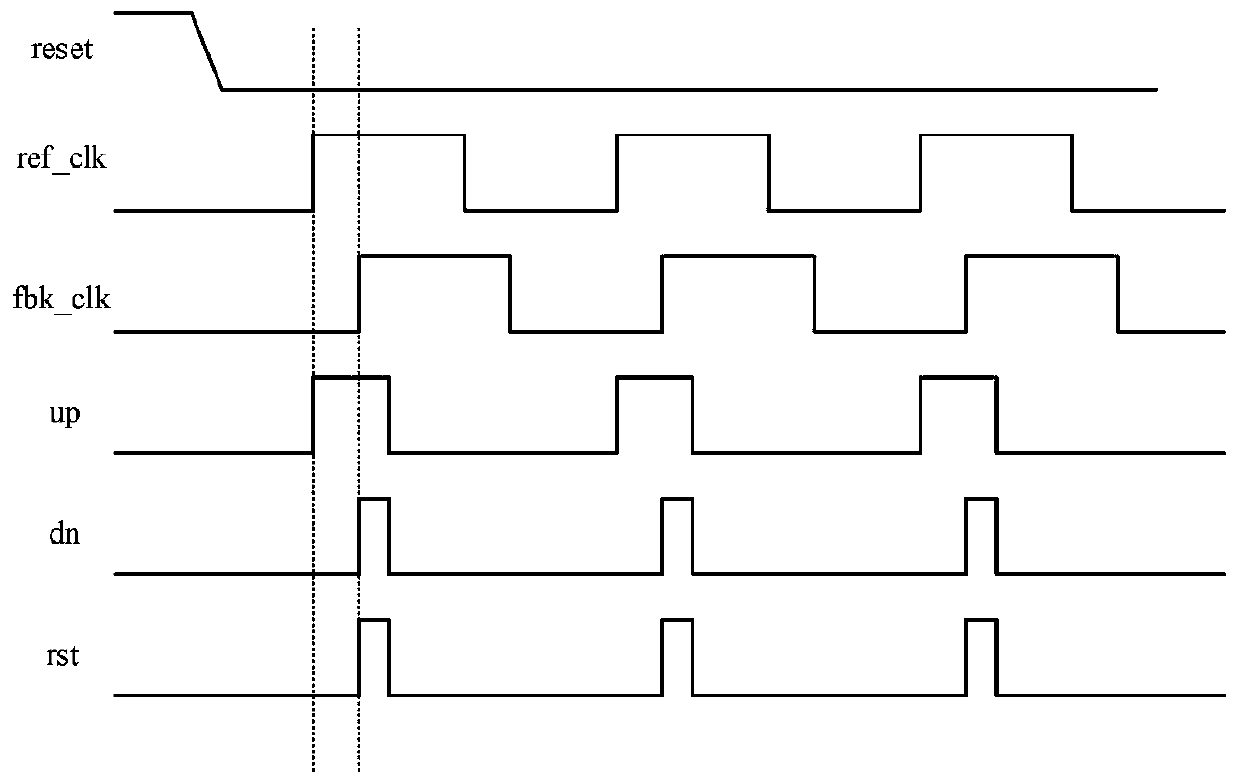

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the objectives, technical solutions and advantages of the present invention clearer, the technical solutions in the embodiments of the present invention will be described clearly and completely in conjunction with the accompanying drawings of the present invention. Obviously, the described embodiments are part of the present invention. Examples, not all examples. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative work shall fall within the protection scope of the present invention. Unless otherwise defined, the technical terms or scientific terms used herein shall be the ordinary meanings understood by those with ordinary skills in the field to which the present invention belongs. As used herein, "comprising" and other similar words mean that the elements or objects appearing before the word cover the elements or objects listed after the word and their equivalents, but ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More