Retention time sequence optimization method based on multiplexing of buffer unit

A buffer unit, hold time technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as inability to optimize timing, too high, increase design area and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

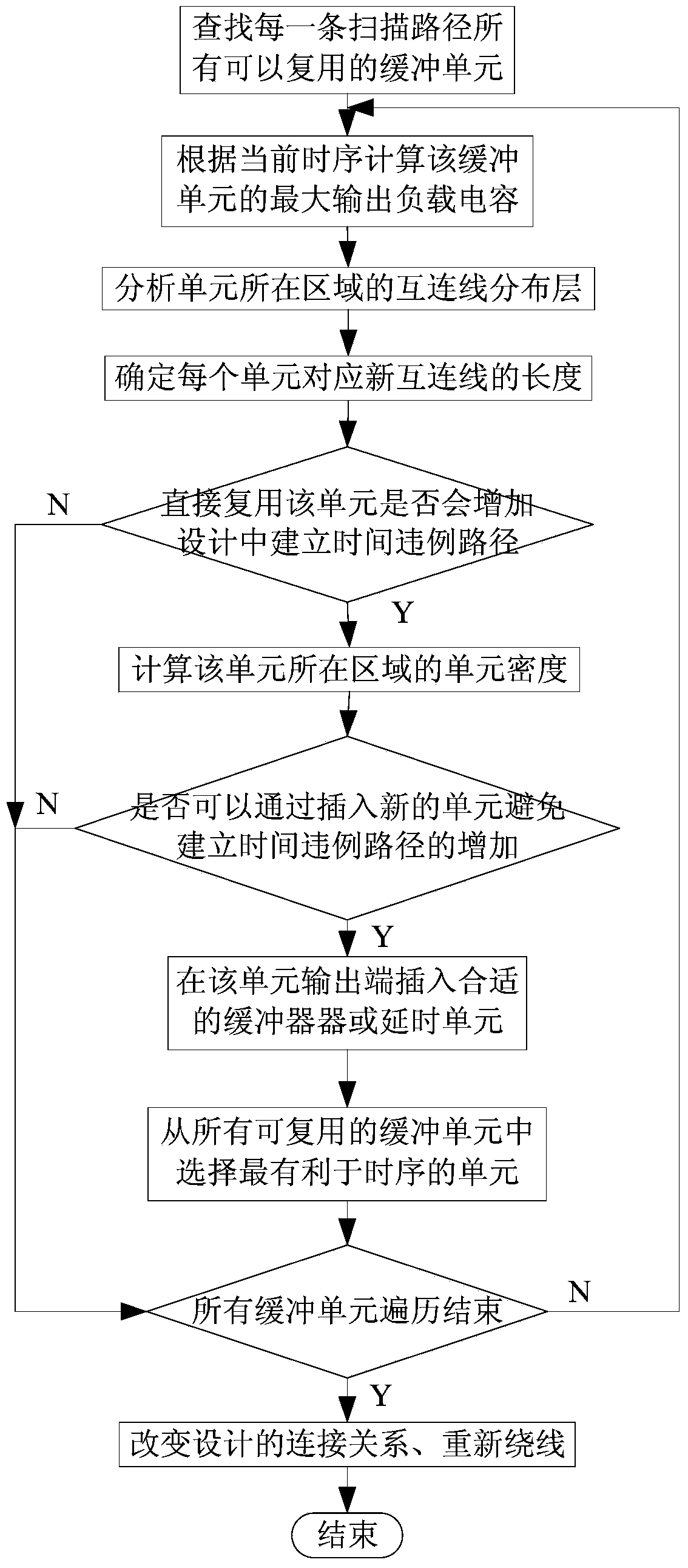

[0048] Such as figure 1 As shown, the implementation steps of the hold time sequence optimization method based on buffer unit multiplexing in this embodiment are as follows:

[0049] 1) In the design to be optimized, find the buffer units on the functional data path that have the same starting point as the scan path that holds the timing violation as reusable buffer units, and designate one of the buffer units as the current buffer unit.

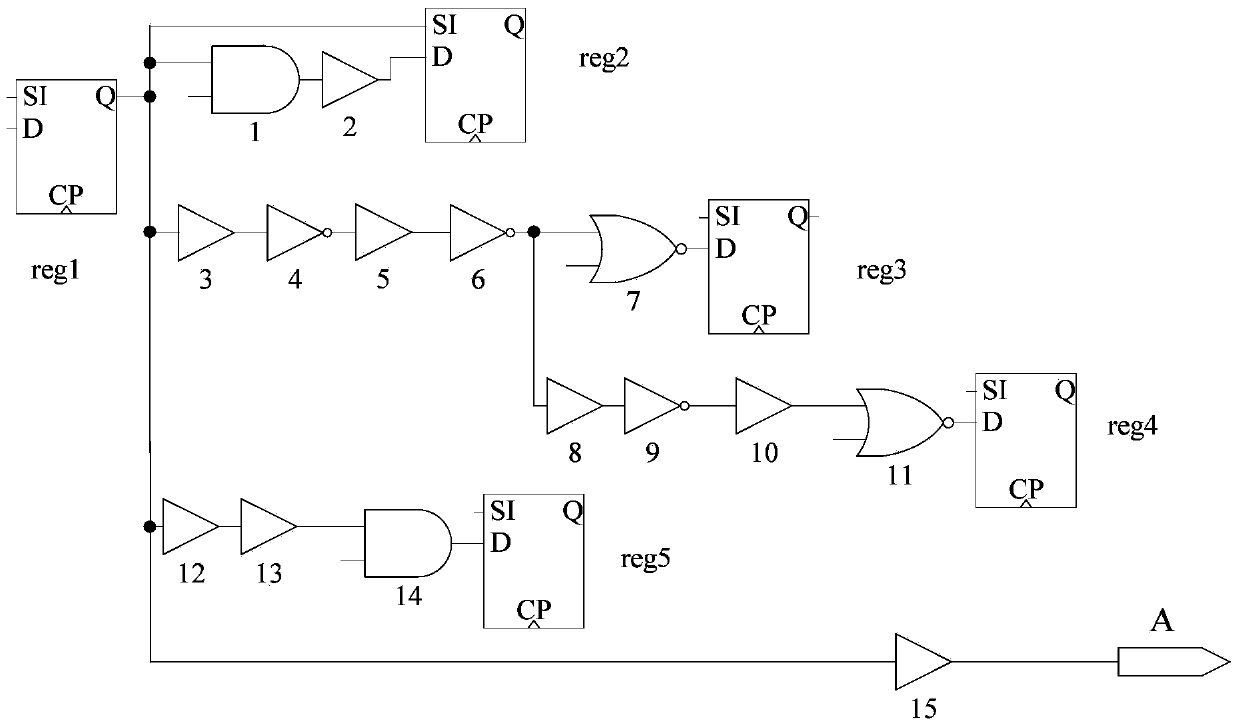

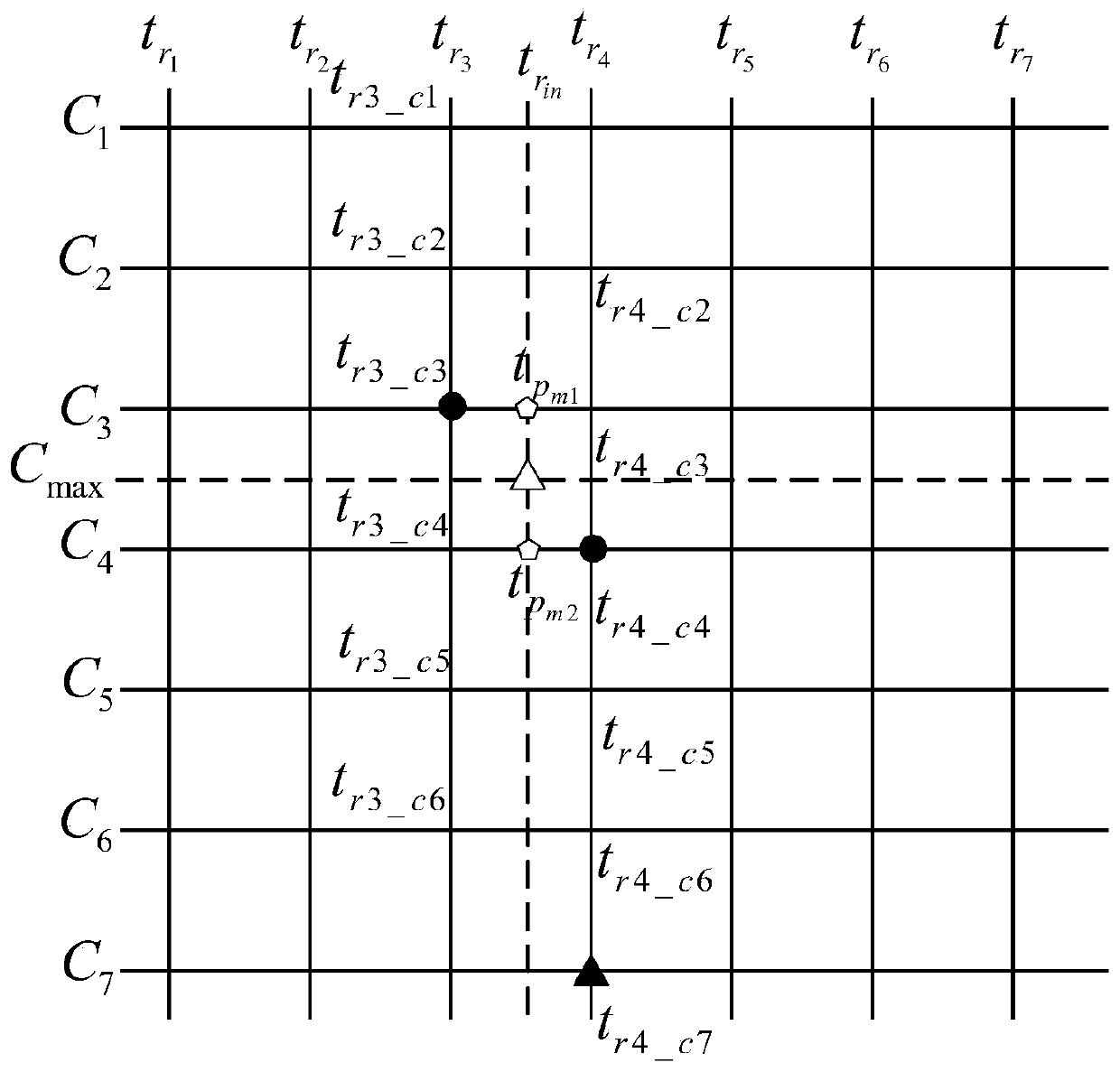

[0050] Since there may be multiple functional data paths at the same starting point, and there may also be buffer units in the port path, this embodiment divides all the functional data paths with the same starting point of the scanning path, and the logical units between the starting register and the non-buffering unit in the port path All the buffer units in between are searched, so as to find the buffer units on the functional data path with the same starting point in each scan path in the design. right figure 2 Take the path shown as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More