Double-bit flash memory, and manufacturing method and operation method thereof

A dual-bit, flash memory technology, applied in the field of dual-bit flash memory, the manufacture of dual-bit flash memory, and the operation of dual-bit flash memory, can solve the problems of data reliability, small distance, and easy interference of storage units.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

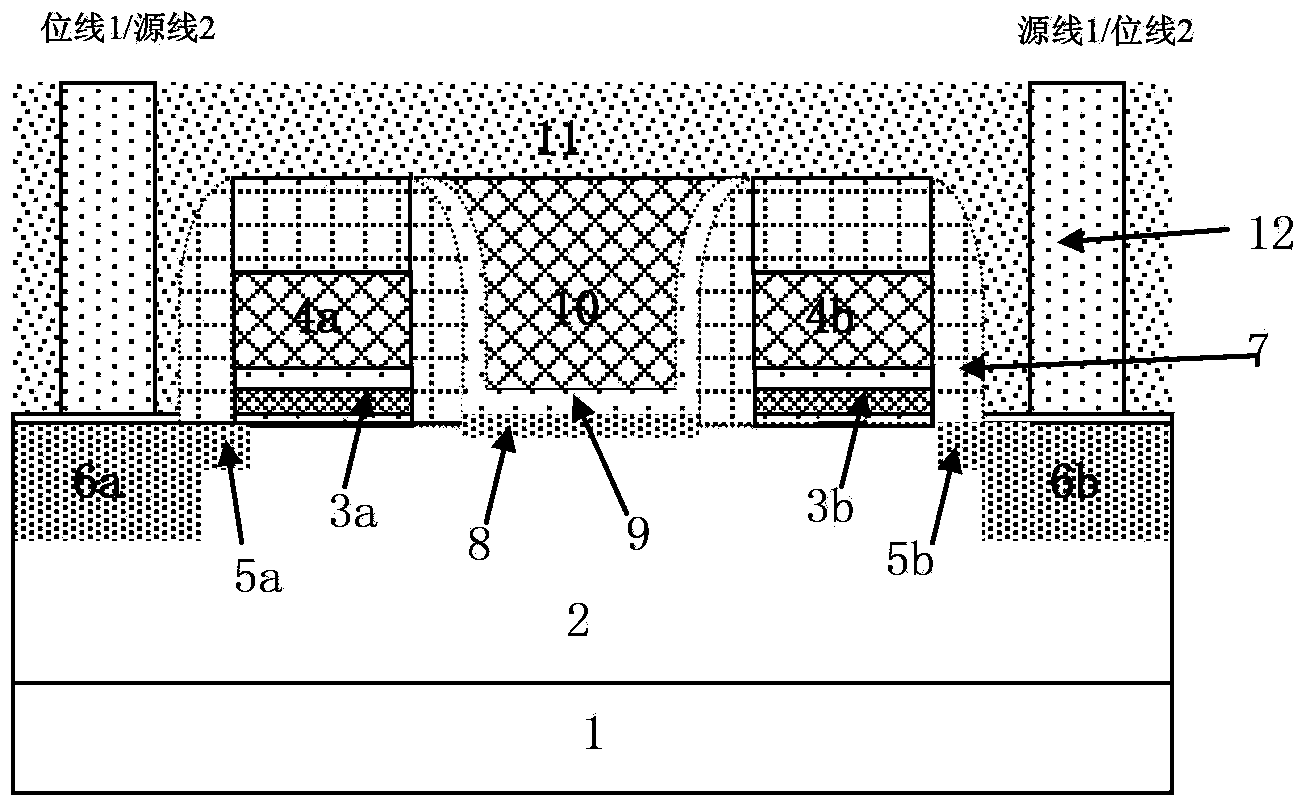

[0051] Such as image 3 Shown is a schematic diagram of the cell structure of the dual-bit flash memory in the embodiment of the present invention; the cell structure of the dual-bit flash memory in the embodiment of the present invention includes: a first SONOS memory, a second SONOS memory, and a selection tube.

[0052] The substrate structure used in the cell structure of the dual-bit flash memory in the embodiment of the present invention is a semiconductor substrate such as a silicon substrate. A deep N-well 1 is formed on the silicon substrate and defined by shallow trench isolation on the silicon substrate. An active region is formed. A P well 2 is formed in the active region of the cell structure region of the dual-bit flash memory in the embodiment of the present invention, and the P well 2 is located on the deep N well 1.

[0053] The gate structure of the first SONOS memory includes an ONO layer 3a composed of a first oxide layer, a second nitride layer, and a third oxid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More