Method for designing mapping scheme and topological structure between task and node in on-chip network

A mapping scheme and network-on-chip technology, applied to general-purpose stored program computers, etc., can solve problems such as not being able to better reflect the actual situation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] The present invention will be further described in detail below in combination with specific embodiments. However, it should not be understood that the scope of the above subject matter of the present invention is limited to the following embodiments, and all technologies realized based on the content of the present invention belong to the scope of the present invention.

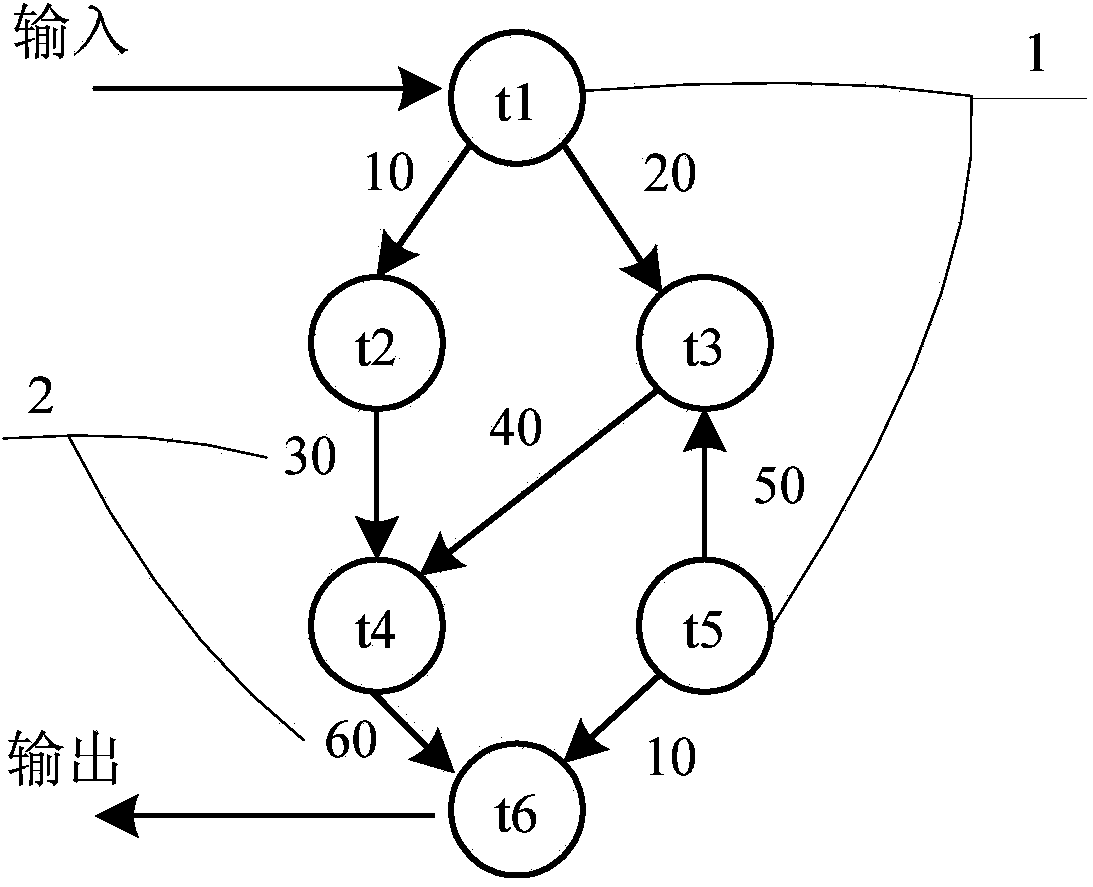

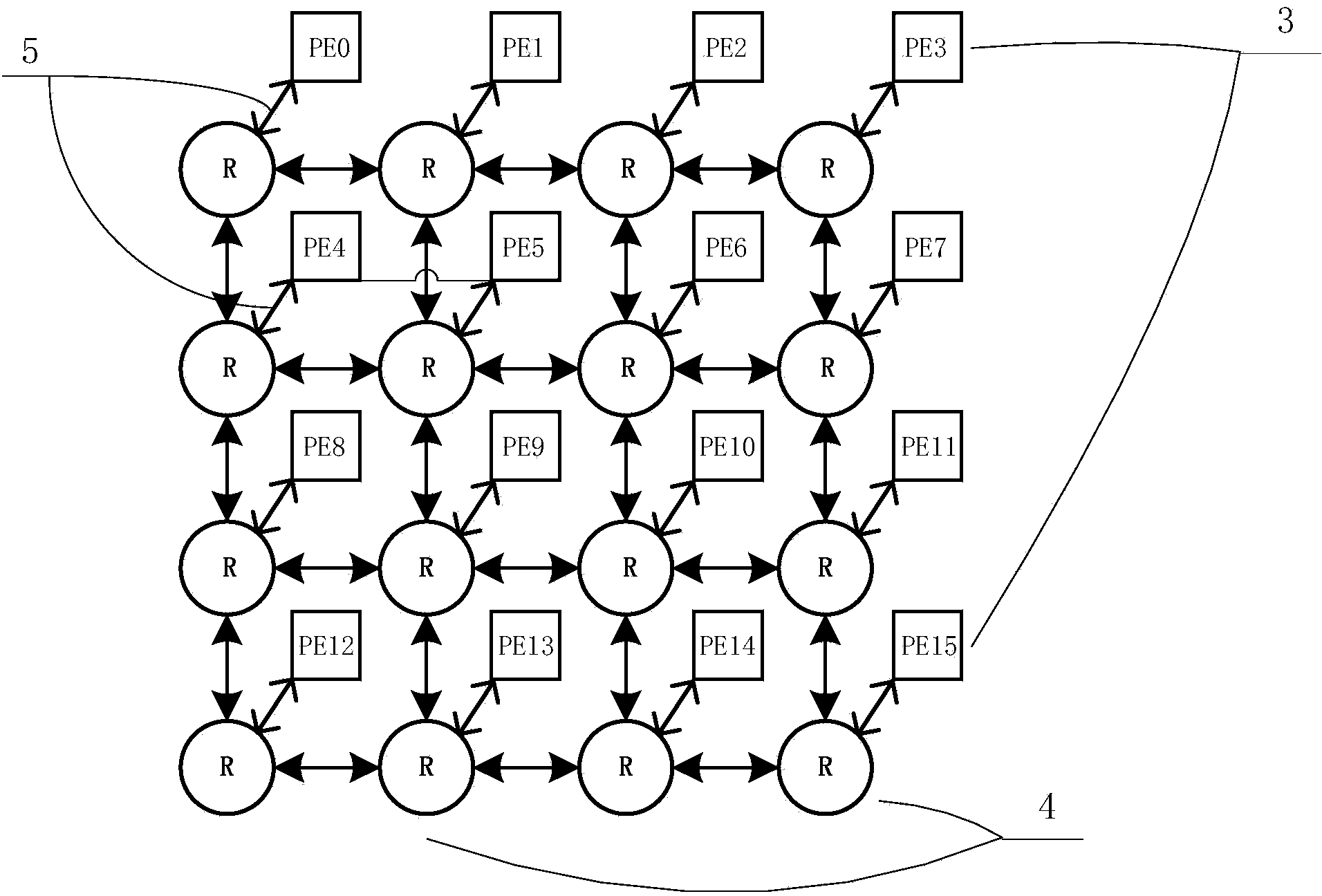

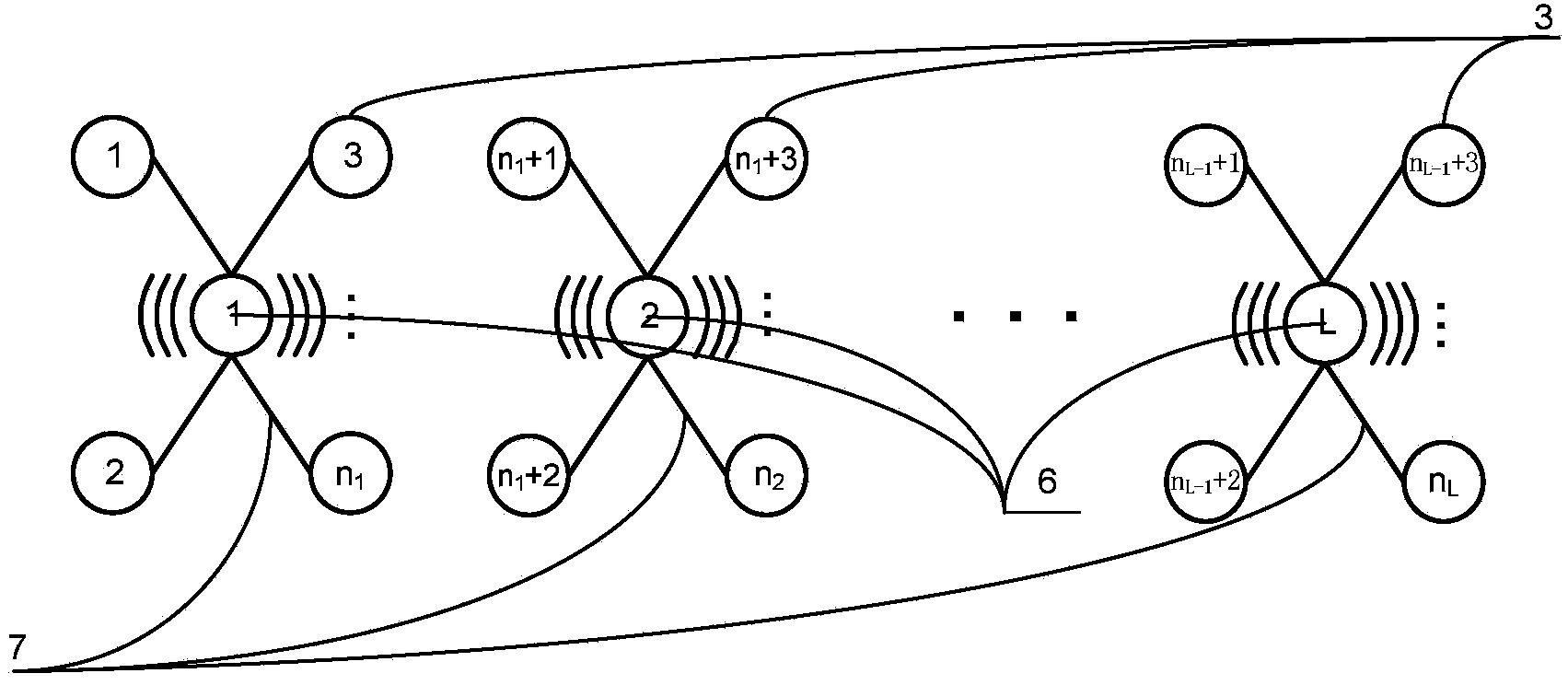

[0073] The present invention separates power consumption and response time as the priority index of the assessment scheme, but considers power consumption and response time at the same time in the process of finding the optimal scheme, so that the found scheme minimizes power consumption and system delay at the same time, Therefore, the performance of the network designed by using this optimized scheme is the best, and compared with other methods for finding the priority scheme of mapping between tasks and nodes under multiple objective functions, it has the characteristics of complexity and simple imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More