Method for preparing storage of vertical structure on basis of buried layer

A vertical structure and memory technology, applied in the micro-nano field, can solve the problems of time-consuming and cost-intensive, and achieve the effect of superior process compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

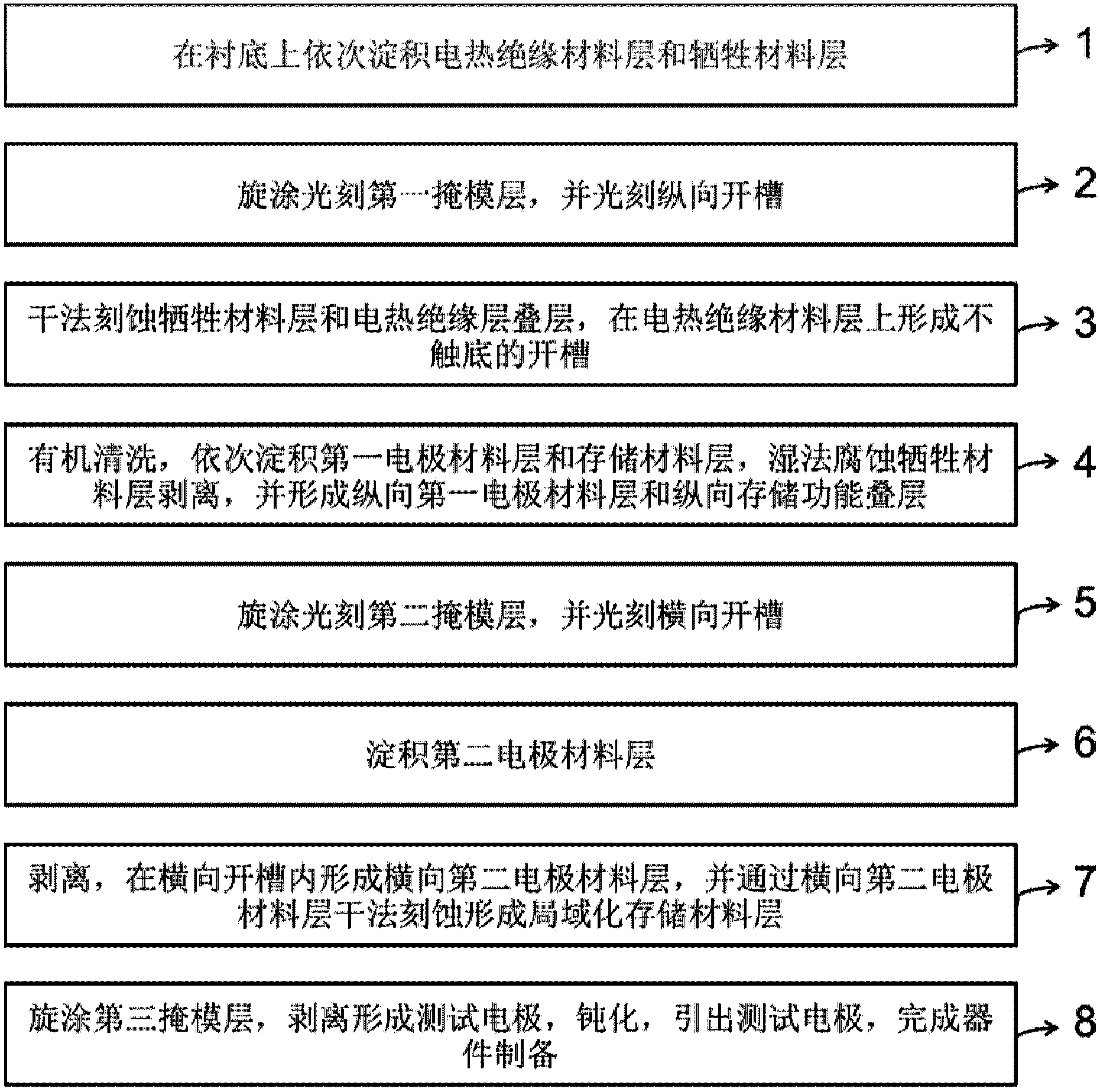

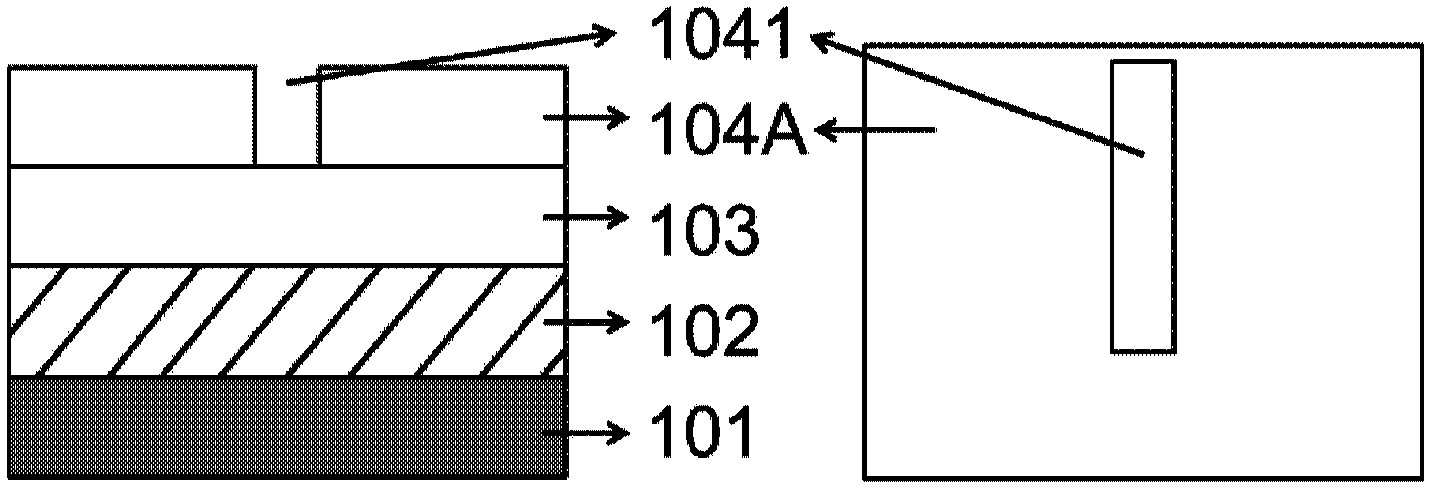

[0021] figure 1 It shows a flow chart of the method for preparing a vertical structure memory based on a buried layer proposed by the present invention. Figure 2A - Figure 2k shows a schematic diagram of the manufacturing process flow of the vertical structure memory based on the buried layer proposed by the present invention. See figure 1 , Figure 2A - As shown in Figure 2k, the present invention provides a method for fabricating a vertical structure memory based on a buried layer. The method includes:

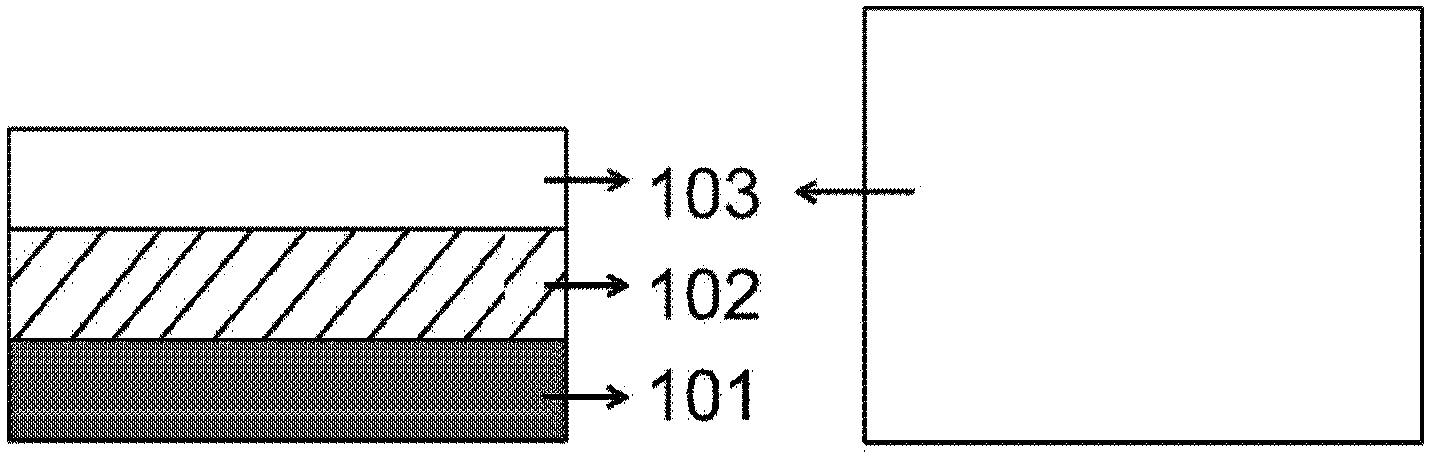

[0022] Step 1: On the substrate 101, sequentially deposit an electrothermal insulating material layer 102 and a sacrificial material layer 103, such as Figure 2A Shown

[0023] The material of the substrate 101 can be s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More