How the transistor is formed

A transistor and semiconductor technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as poor transistor performance, improve performance, enhance reliability, and avoid excessive reduction.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background, the performance of the transistor with the high-K dielectric layer and the metal gate structure in the prior art is not good.

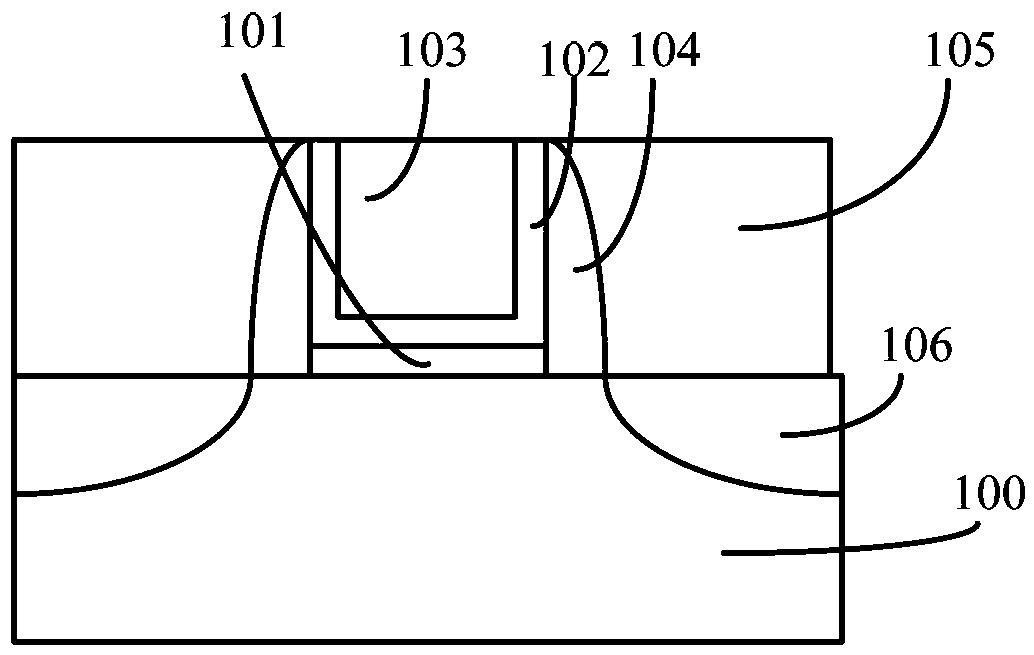

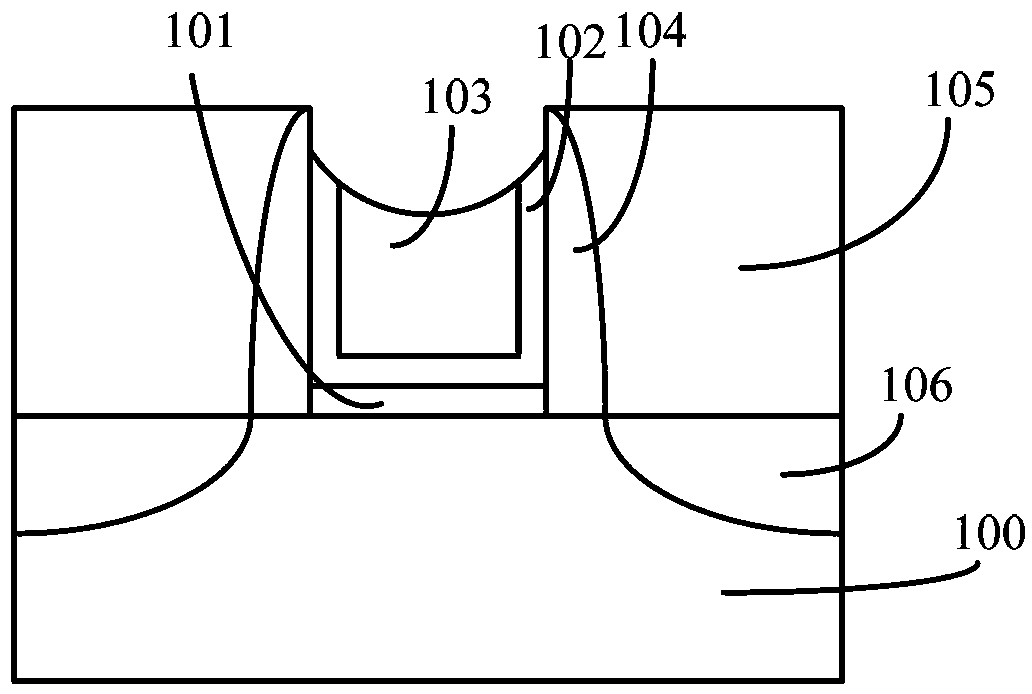

[0033] Existing technologies are forming as figure 1 After the shown transistor with high-K dielectric layer and metal gate structure, it is necessary to reduce the height of the work function layer 102 and the metal gate layer 103, so that the surface of the work function layer 102 and the metal gate layer 103 An insulating layer flush with the surface of the dielectric layer 101 is formed, so that the subsequently formed electrical interconnection structure for the transistor can be electrically isolated from the work function layer 102 and the metal gate layer 103 . Specifically, the method for reducing the work function layer 102 and the metal gate layer 103 is: etching the metal gate layer 103 so that the top surface of the metal gate layer 103 is lower than the dielectric layer 101 and the work function lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More