FPGA based high-speed network strategy matching method

A matching method and high-speed network technology, applied in the field of network matching, can solve the problems of large hardware space occupation, complex logic operation, low efficiency, etc., and achieve the effect of low storage space occupation, simple and efficient logic processing, and improved matching efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

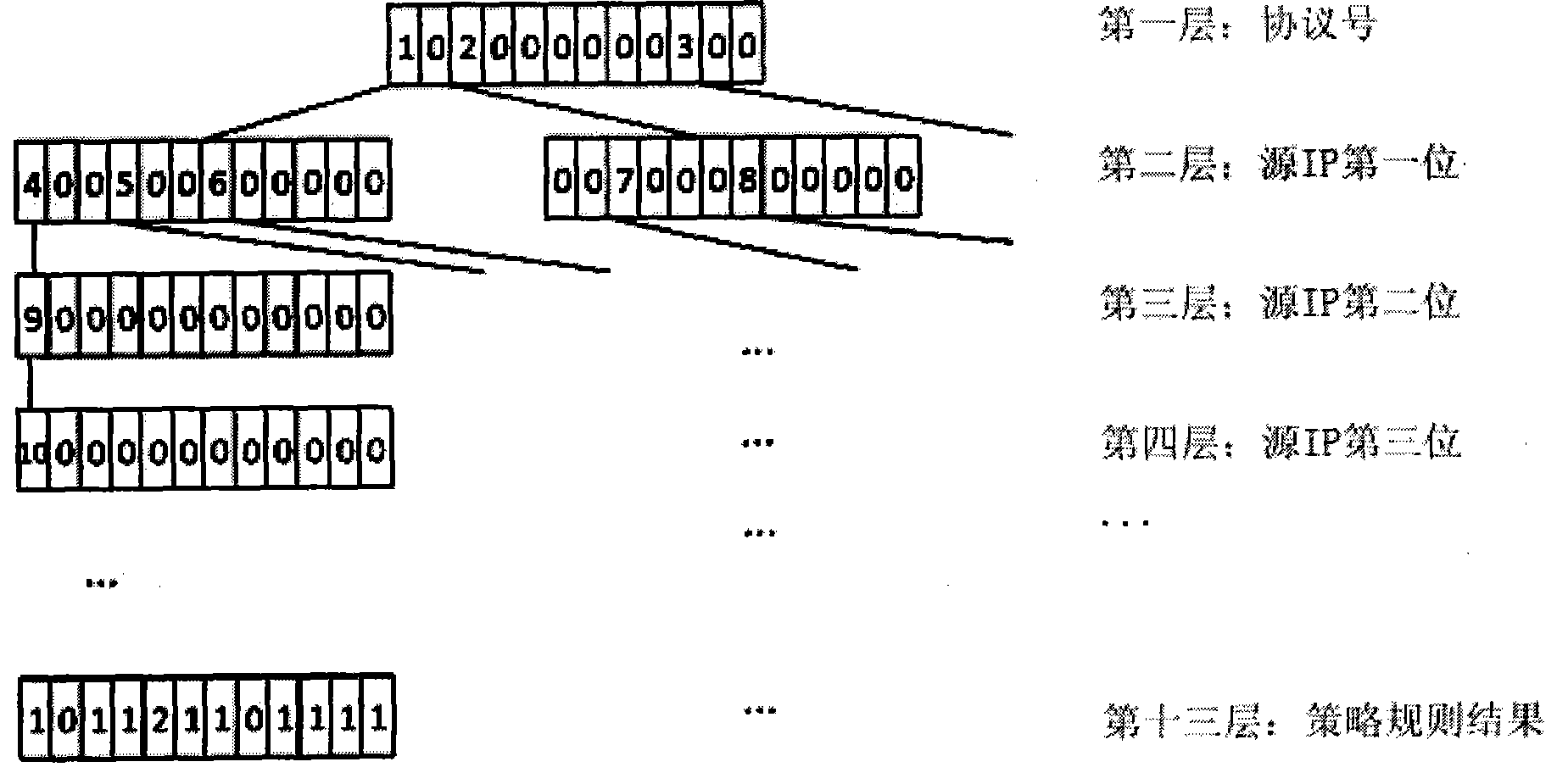

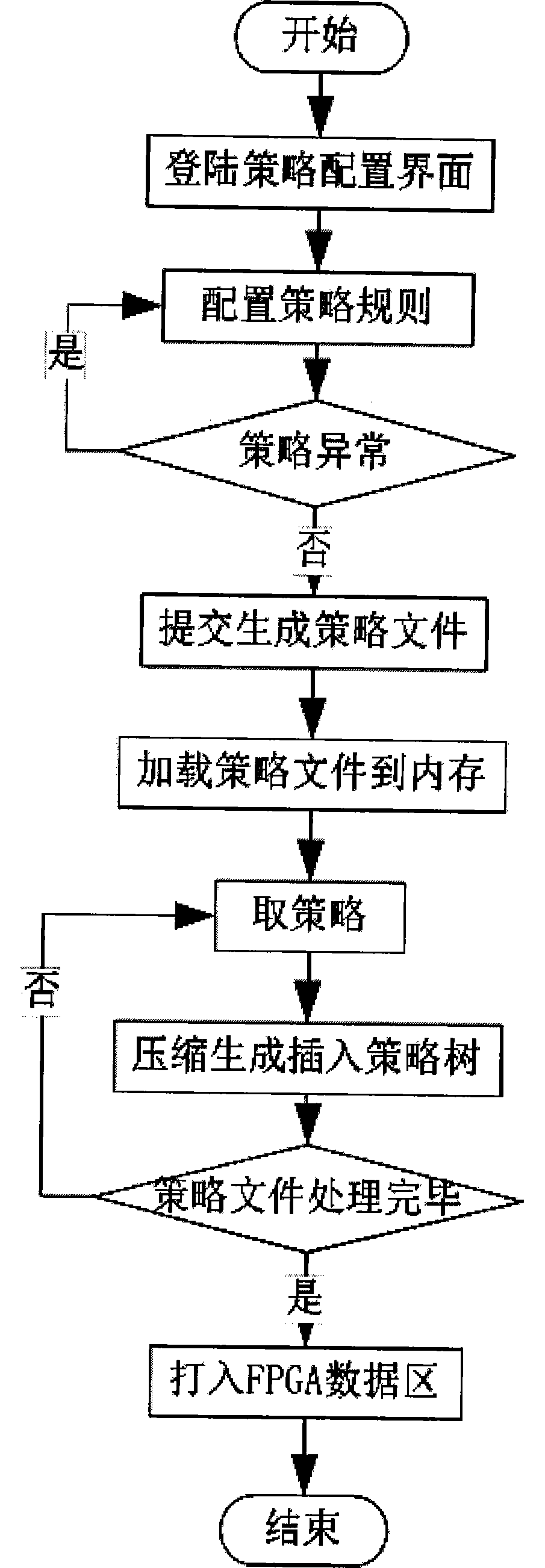

[0034] like image 3 , 4 As shown, an FPGA-based high-speed network strategy matching method of the present invention includes a strategy tree generation method and a strategy tree matching method;

[0035] The strategy tree generation method includes the following steps:

[0036] Step 1: Set a number of network policy matching conditions that need to be configured on the network policy related interface: quintuple and policy result (such as: clear communication, secret communication, discard, padding, etc.);

[0037] Step 2: After the interface configuration is completed, a custom binary mode policy data file is generated in the system background;

[0038] Step 3: read the policy data file into memory;

[0039] Step 4: read a policy record from the policy data file;

[0040] Step 5: According to the key information in the described policy record, insert the FPGA policy tree according to the protocol number, source IP, destination IP, source port, destination port and poli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More