Integrated satellite navigation chip and manufacture method thereof

A satellite navigation and chip technology, which is applied in the field of satellite navigation, can solve problems such as insufficient connection between the core algorithm of the radio frequency chip and the baseband processing chip, restricting the rapid development of the Beidou satellite navigation industry, and poor confidentiality of technical solutions, so as to reduce secondary The effect of development difficulty, low cost, area and volume reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

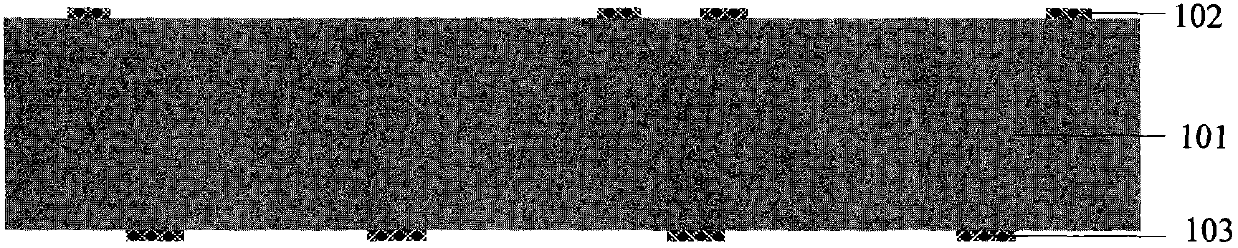

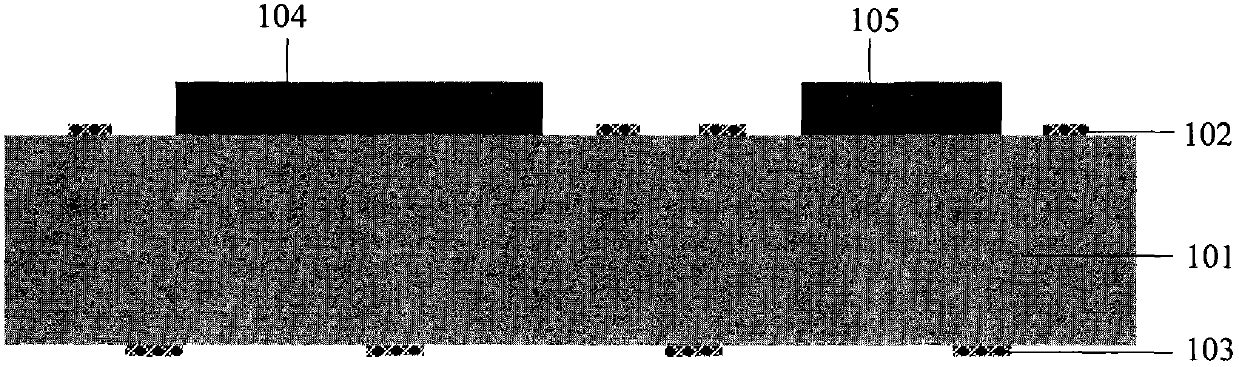

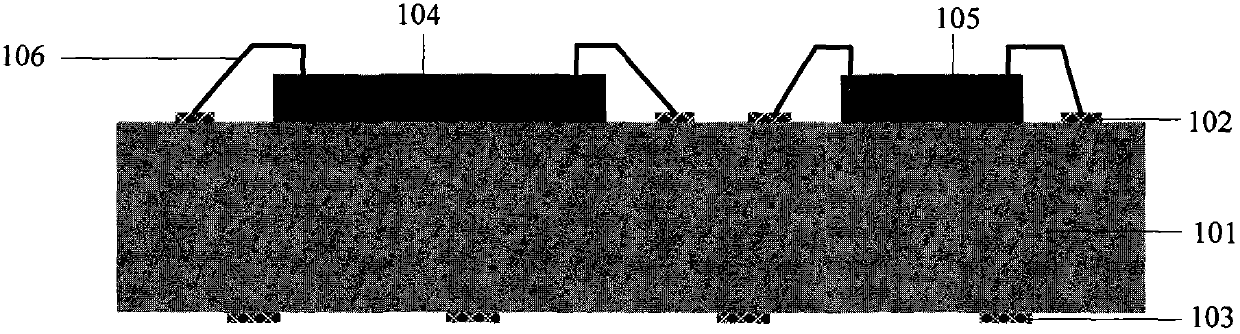

[0041] Figure 1a to Figure 1e It is a cross-sectional schematic diagram of a specific implementation process for completing an integrated satellite navigation chip according to the present invention.

[0042] Step 1, design and produce such as Figure 1a The shown two-layer printed circuit substrate 101 for realizing the logic connection and supporting function among multiple chips can be manufactured by conventional substrate technology, except that there are two layers on the substrate for realizing the functional electrical connection of the integrated navigation chip. The redistribution layer, and the pad structure 102 on the upper surface for the bonding wire pad of the surface die, generally composed of copper, nic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More