A flip-flop design method against single-event upset and single-event transient pulse

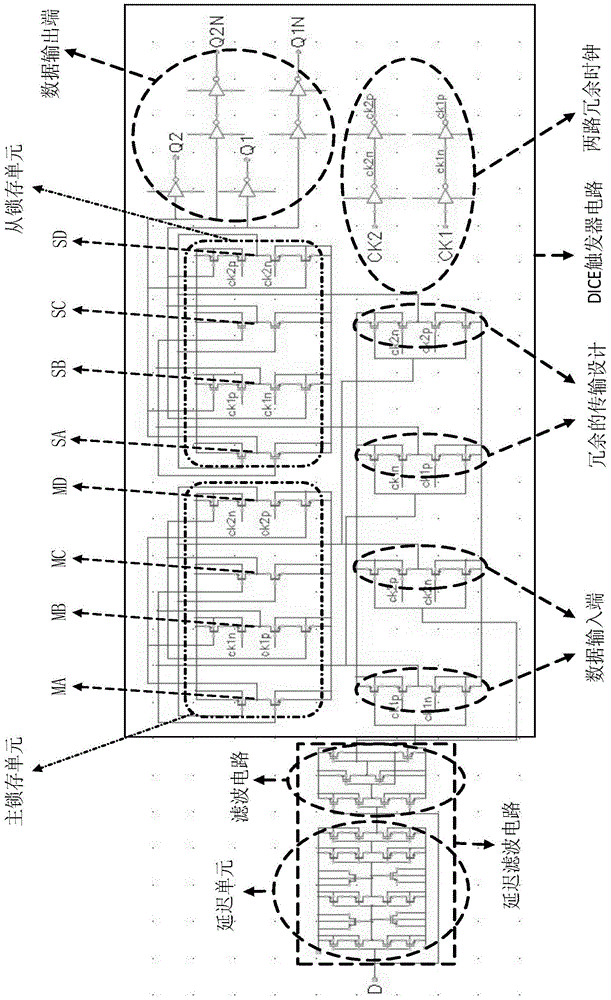

A single-event transient and single-event anti-single-event technology is applied in the direction of pulse generation, pulse technology, and electric pulse generation. It can solve problems such as accidental capture of data, weak SET protection at data input terminals, and wrong data collected by triggers. Reduce power consumption overhead, improve the ability to resist SEU/SET, and avoid the effects of clock overlap

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

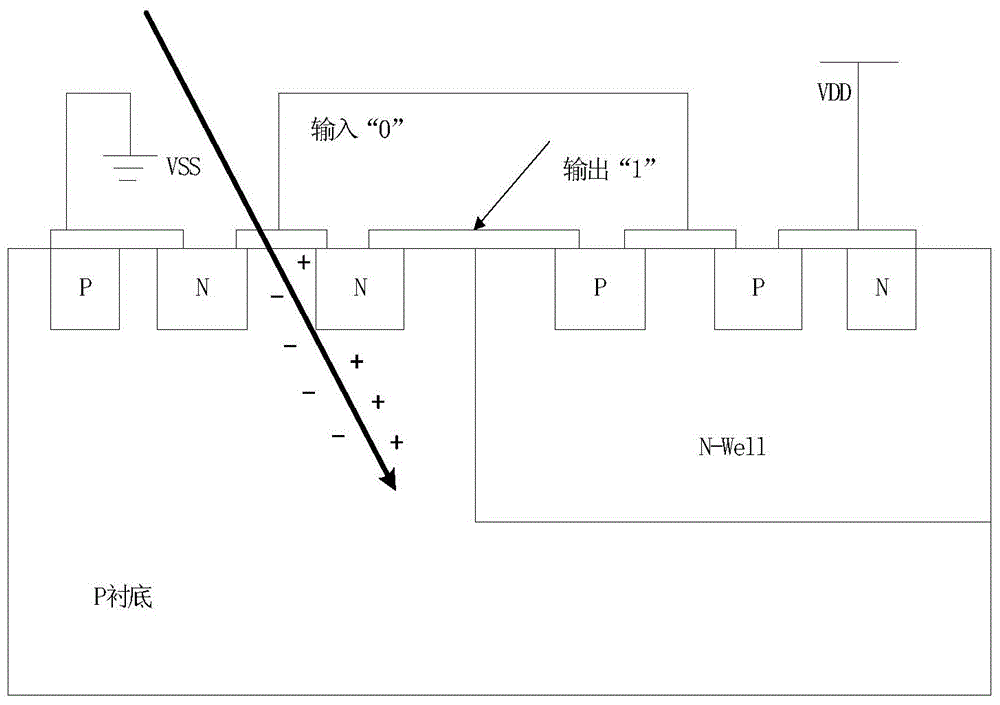

[0046] Single event flipping and single event transient effects will cause the function of the flip-flop unit in the CMOS integrated circuit to be faulty, and it cannot be recovered, resulting in abnormal function of the entire device.

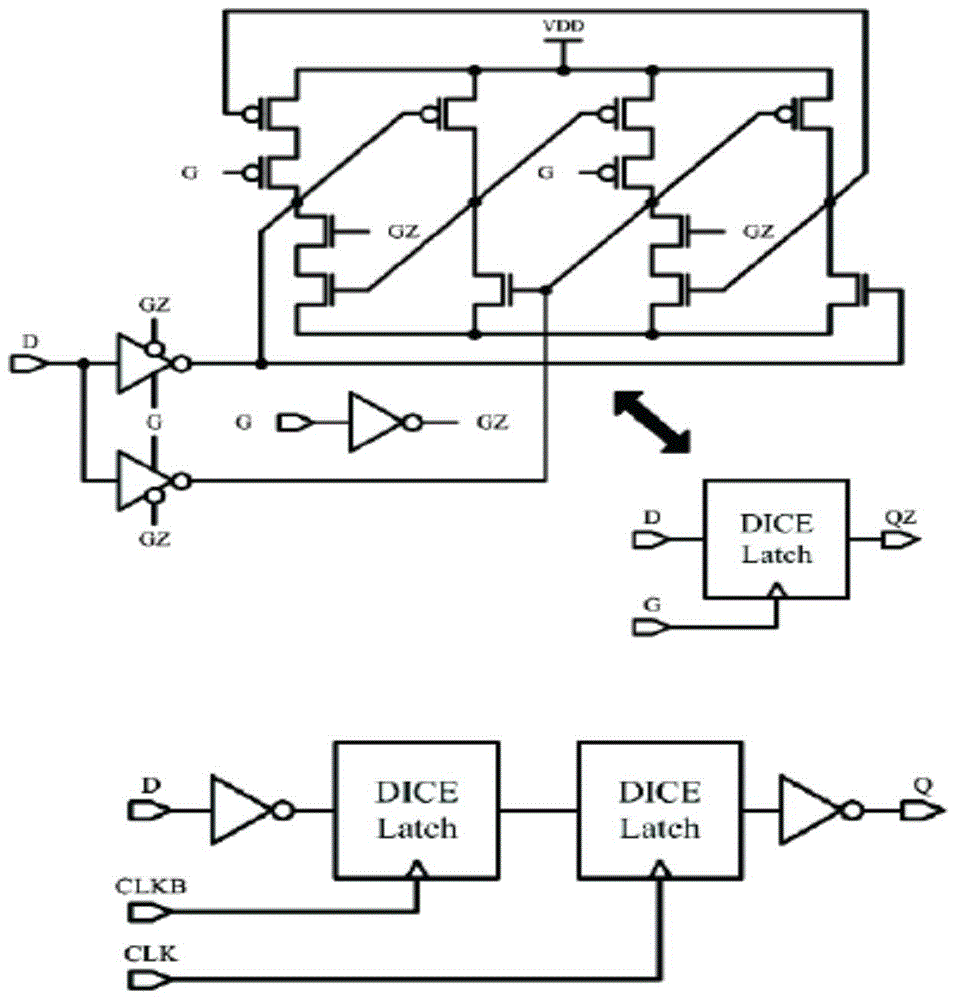

[0047] In a variety of anti-SEU flip-flop designs, the flip-flop unit of the DICE structure has less loss in speed, area and power consumption, and has a better protection effect. figure 2 It is a schematic diagram of a basic DICE latch unit and "master-slave" flip-flop circuit. It can be seen that there are 4 charge storage nodes inside the DICE latch, and every 2 storage nodes store the same logic level value. When the incident energy particles flip the potential of one of the nodes, the remaining 3 storage nodes can The level value is restored through DICE's double interlocking structure. Only when two related storage nodes (nodes that store the same logic level) are simultaneously affected by high-energy particles can the entire circuit flip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More