How transistors are made

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as uneven threshold voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

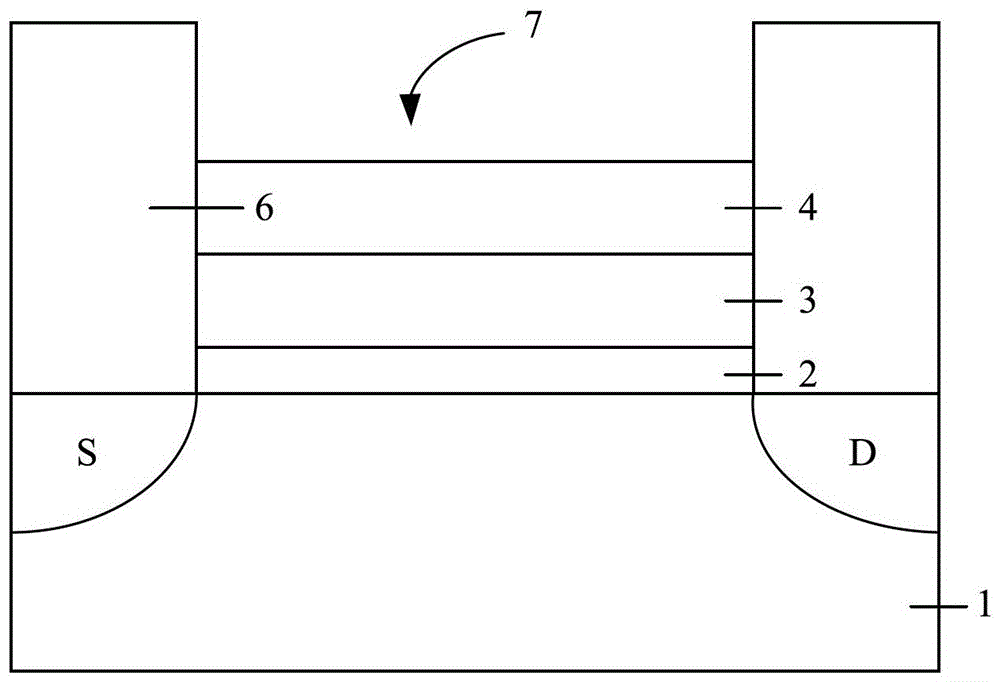

[0041] The manufacturing method of the metal gate transistor mentioned in the background art is likely to cause irregular damage to the protective layer, and an oxide layer with uneven depth is formed on the surface of the protective layer, resulting in uneven threshold voltage of the transistor.

[0042] In order to solve the above-mentioned technical problems, the inventor made a lot of analysis on the manufacturing method of the above-mentioned metal gate transistor. Through in-depth analysis, the inventor found that:

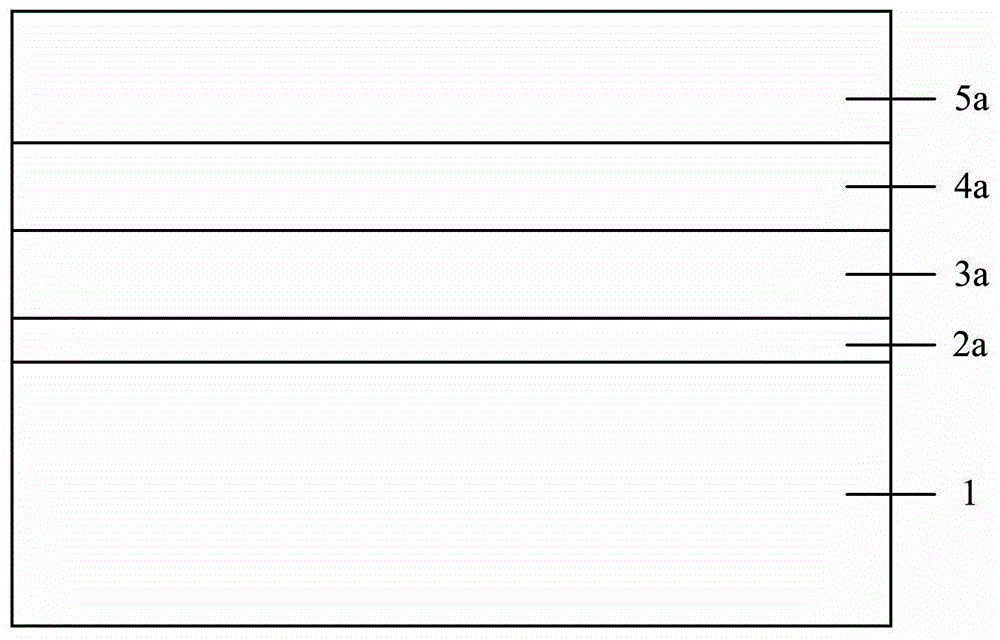

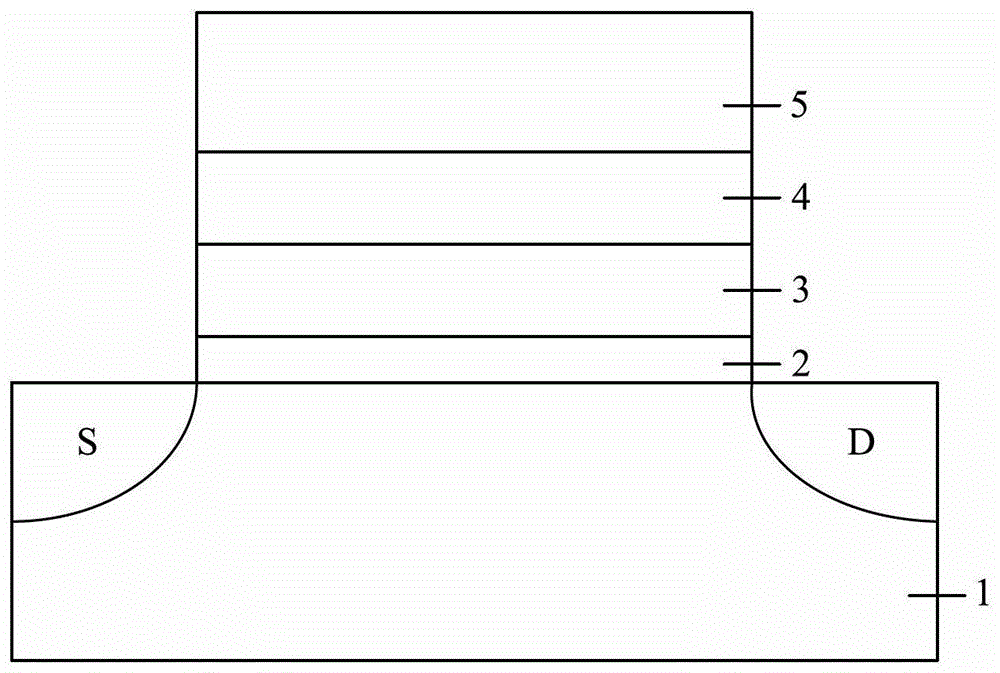

[0043] combined reference figure 2 and image 3, when removing the polysilicon layer 5, dry etching is often used. Due to the high etching rate of the polysilicon layer 5 and the etching effect on the protective layer 4, the polysilicon layer 5 is removed to form a dummy gate. During the process of trench 7, it is easy to cause irregular damage to protective layer 4 by over-etching, and the irregular damage itself will cause uneven threshold voltage. In a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More