Patents

Literature

30results about How to "Threshold voltage uniform" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

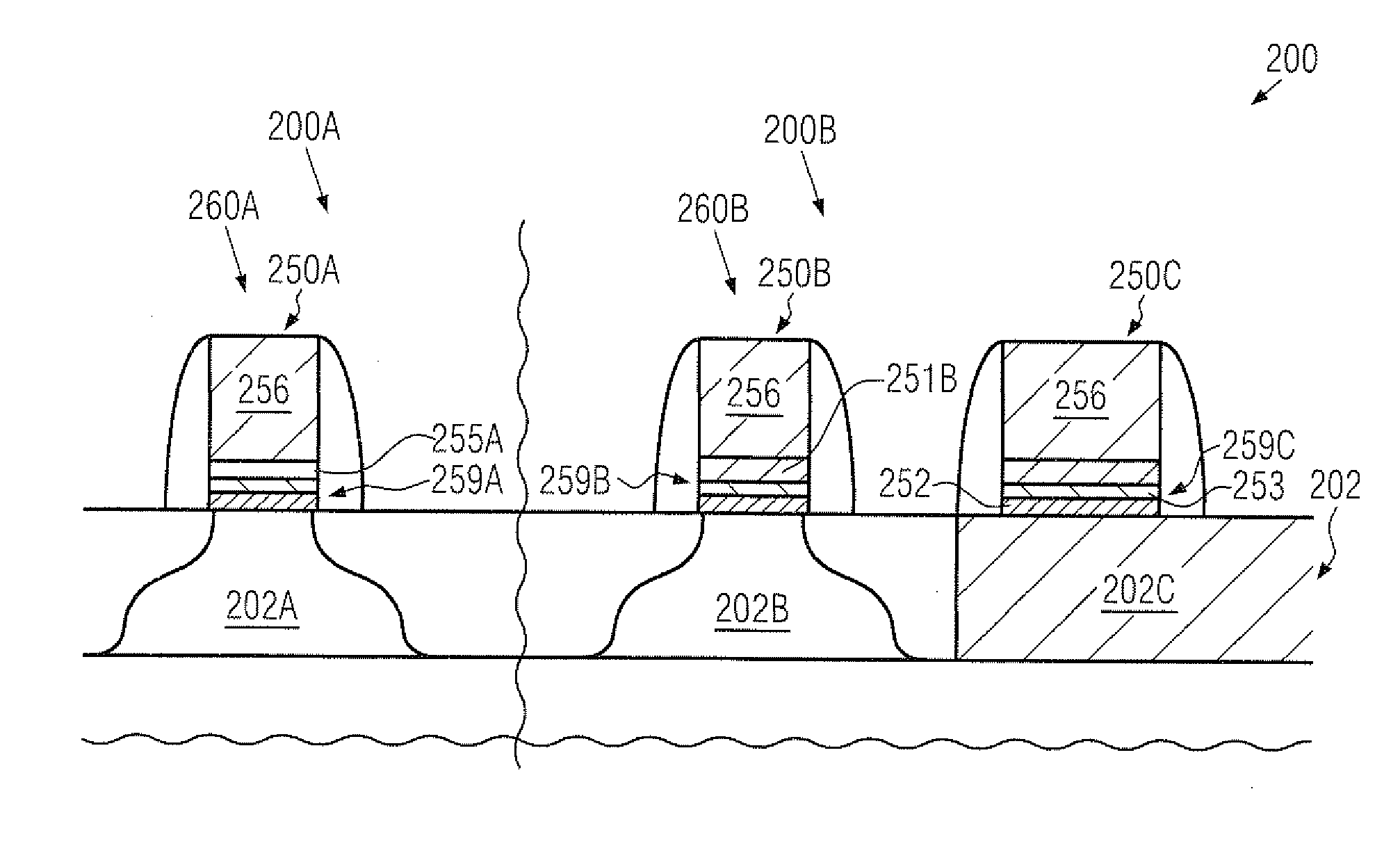

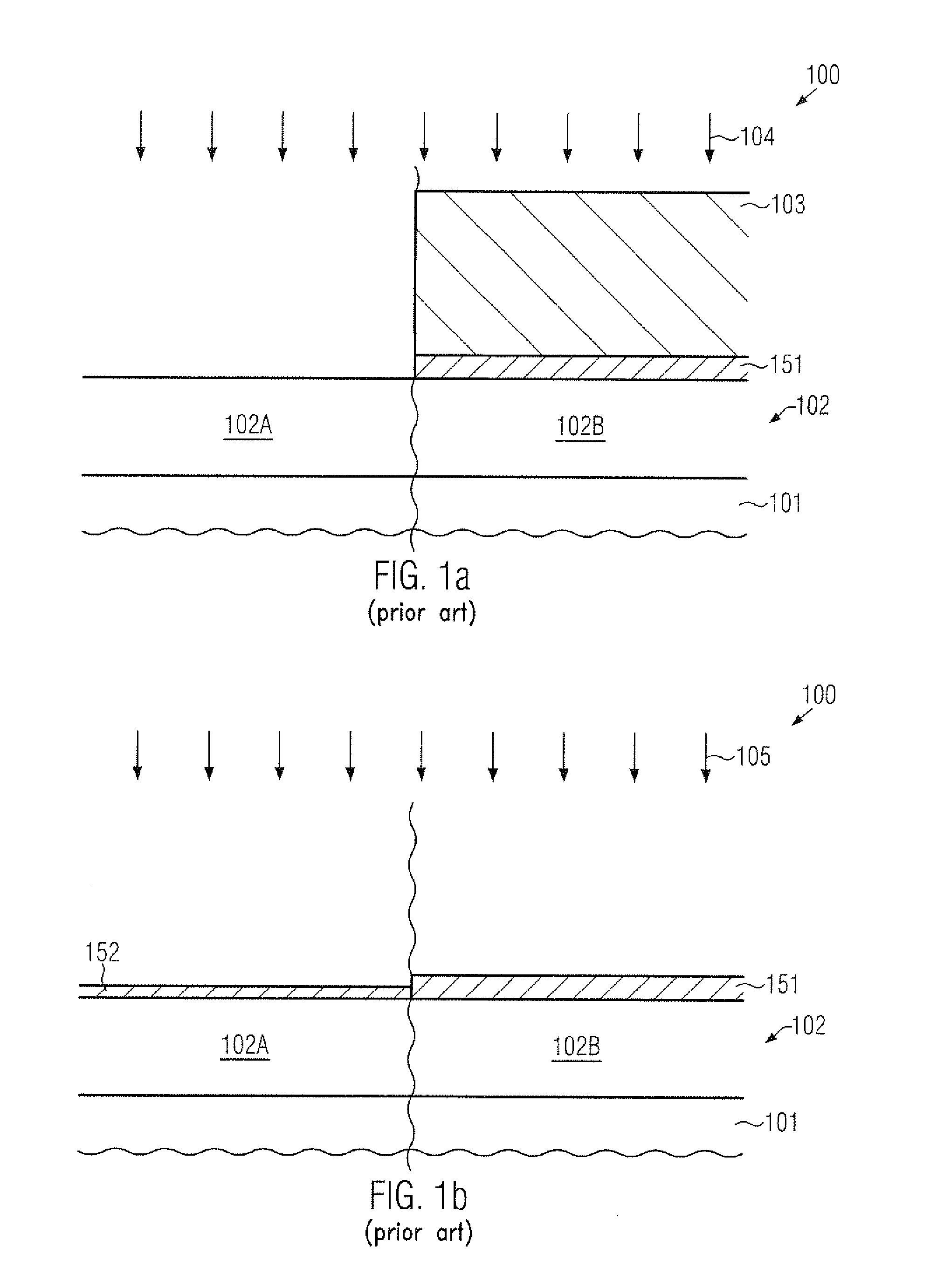

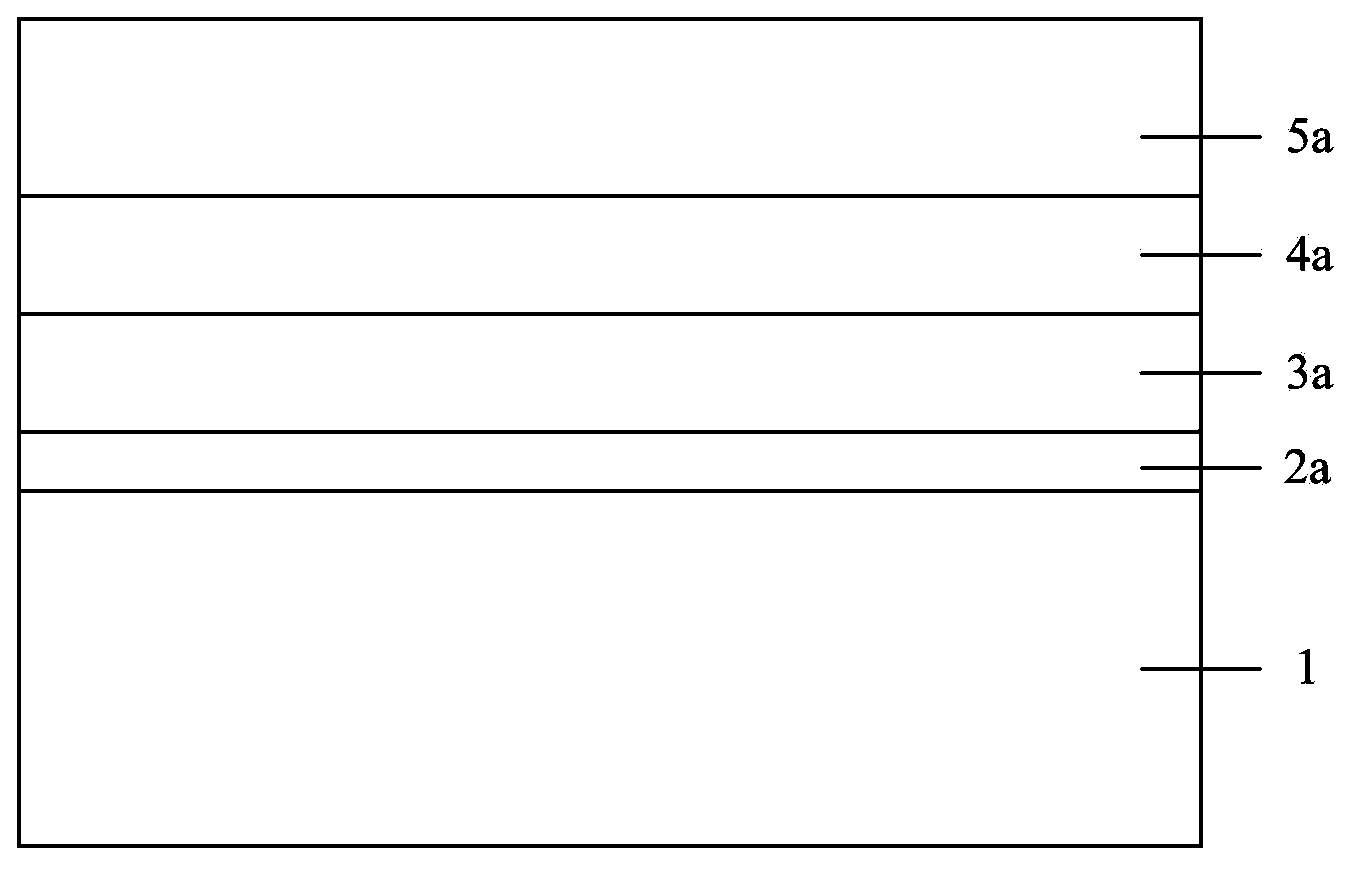

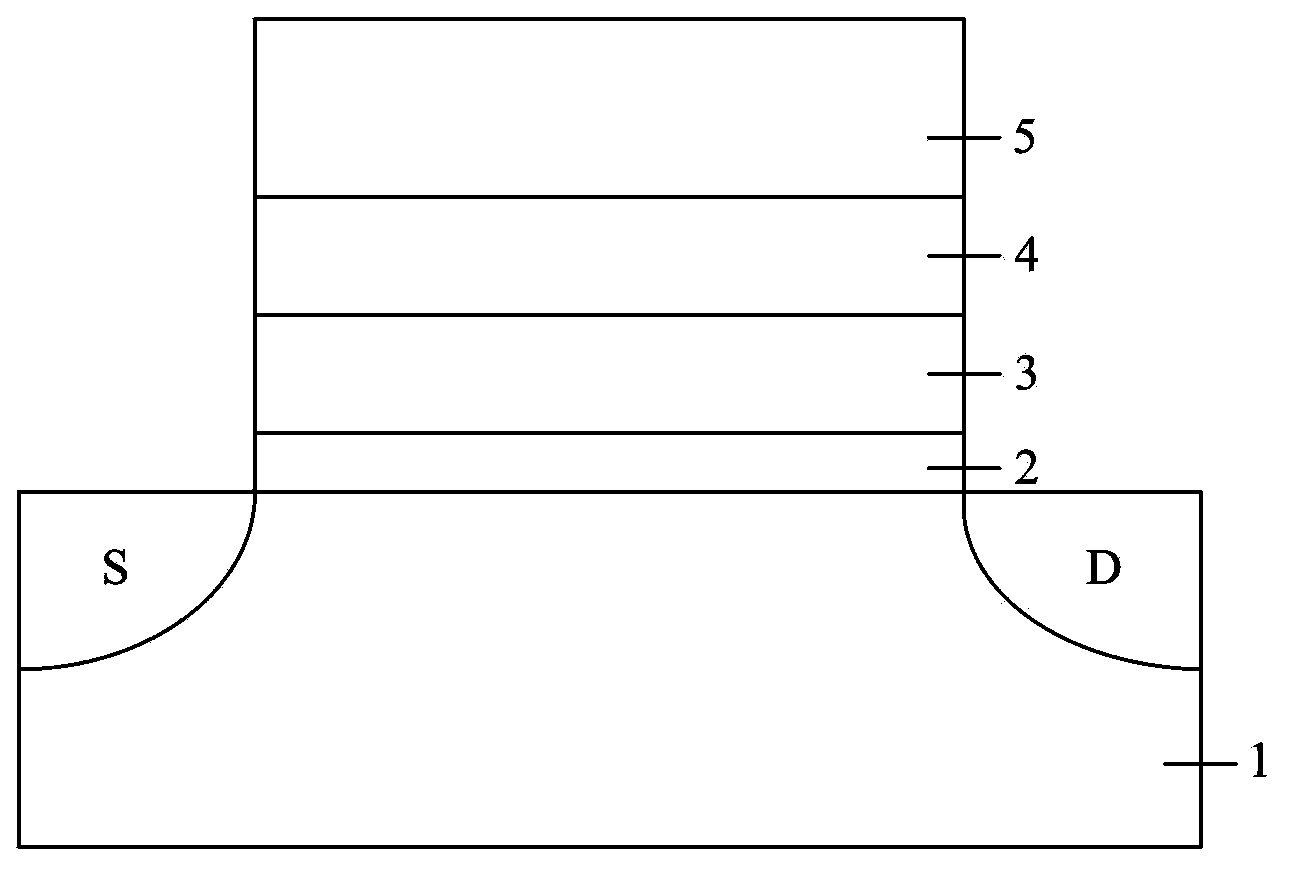

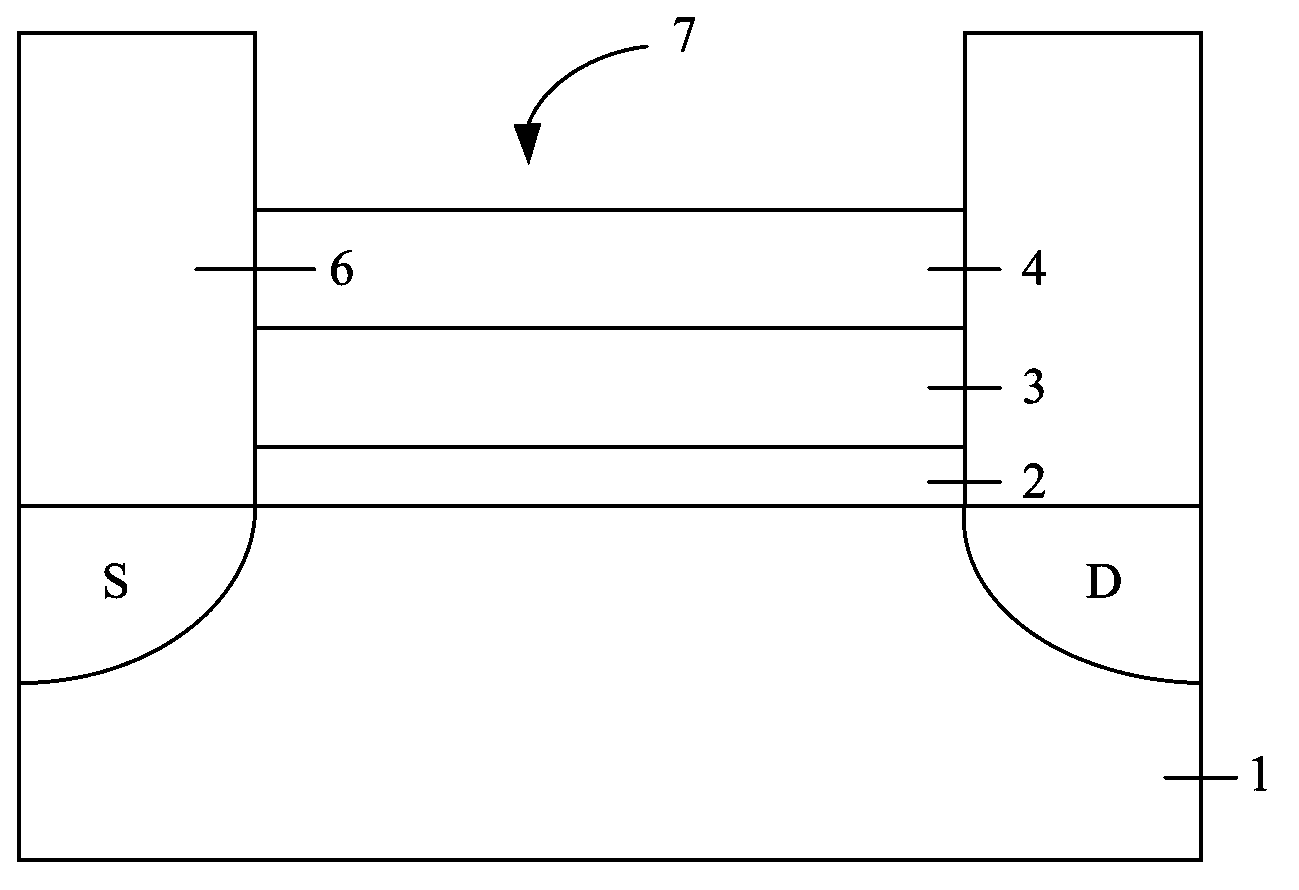

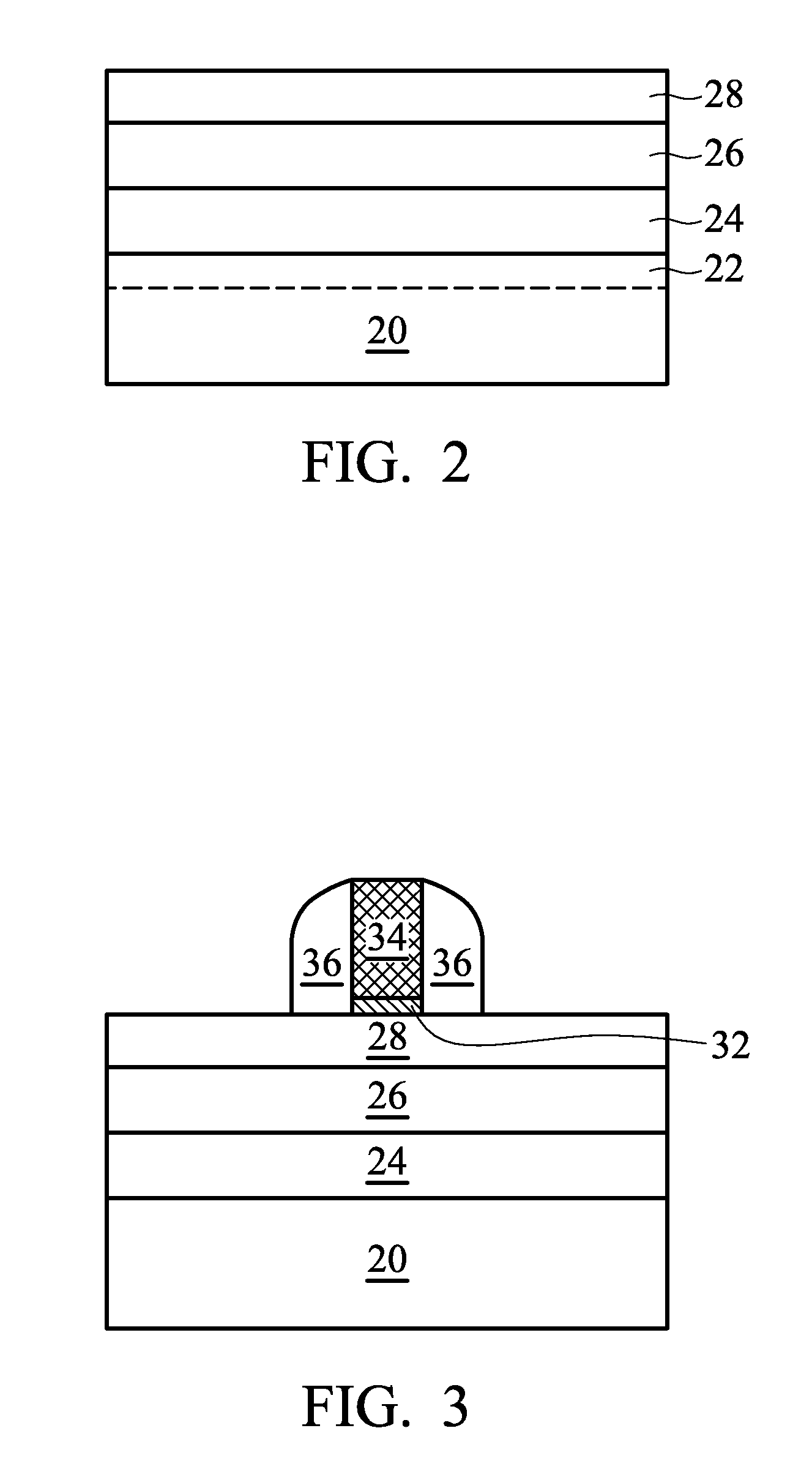

Work function adjustment in high-k gate stacks including gate dielectrics of different thickness

ActiveUS20110049642A1Improve evenlyReduce thicknessTransistorSolid-state devicesElectricityGate dielectric

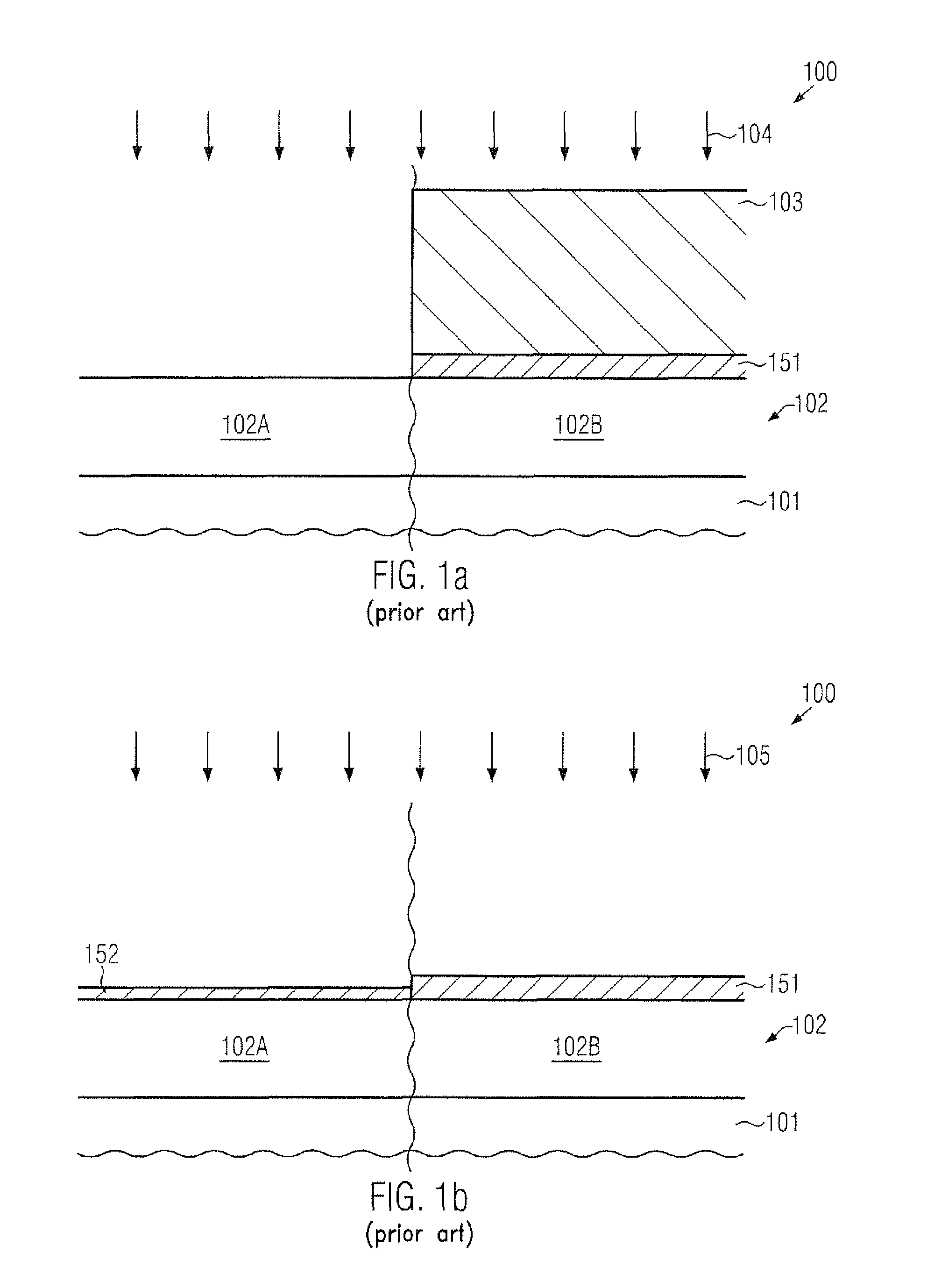

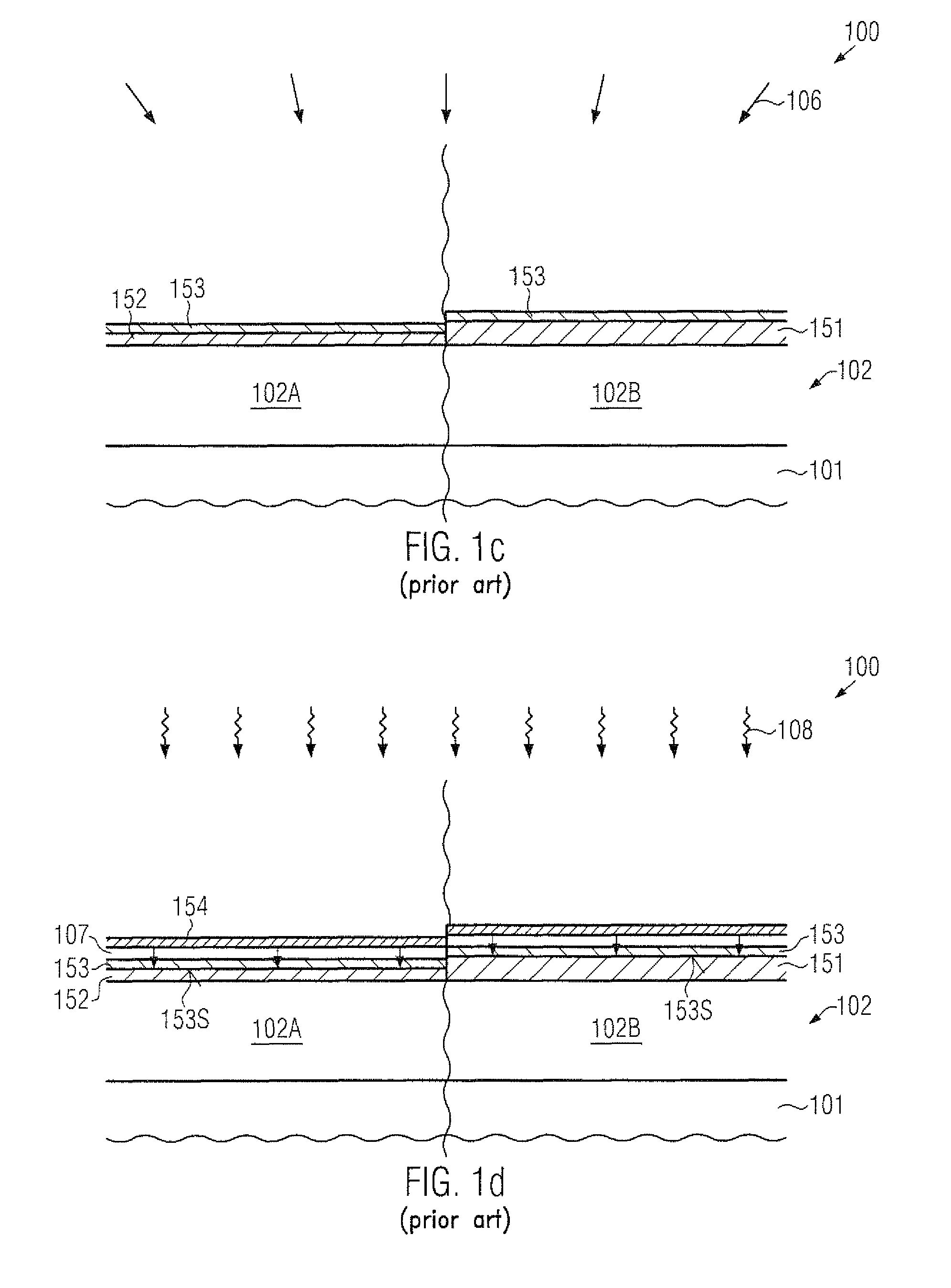

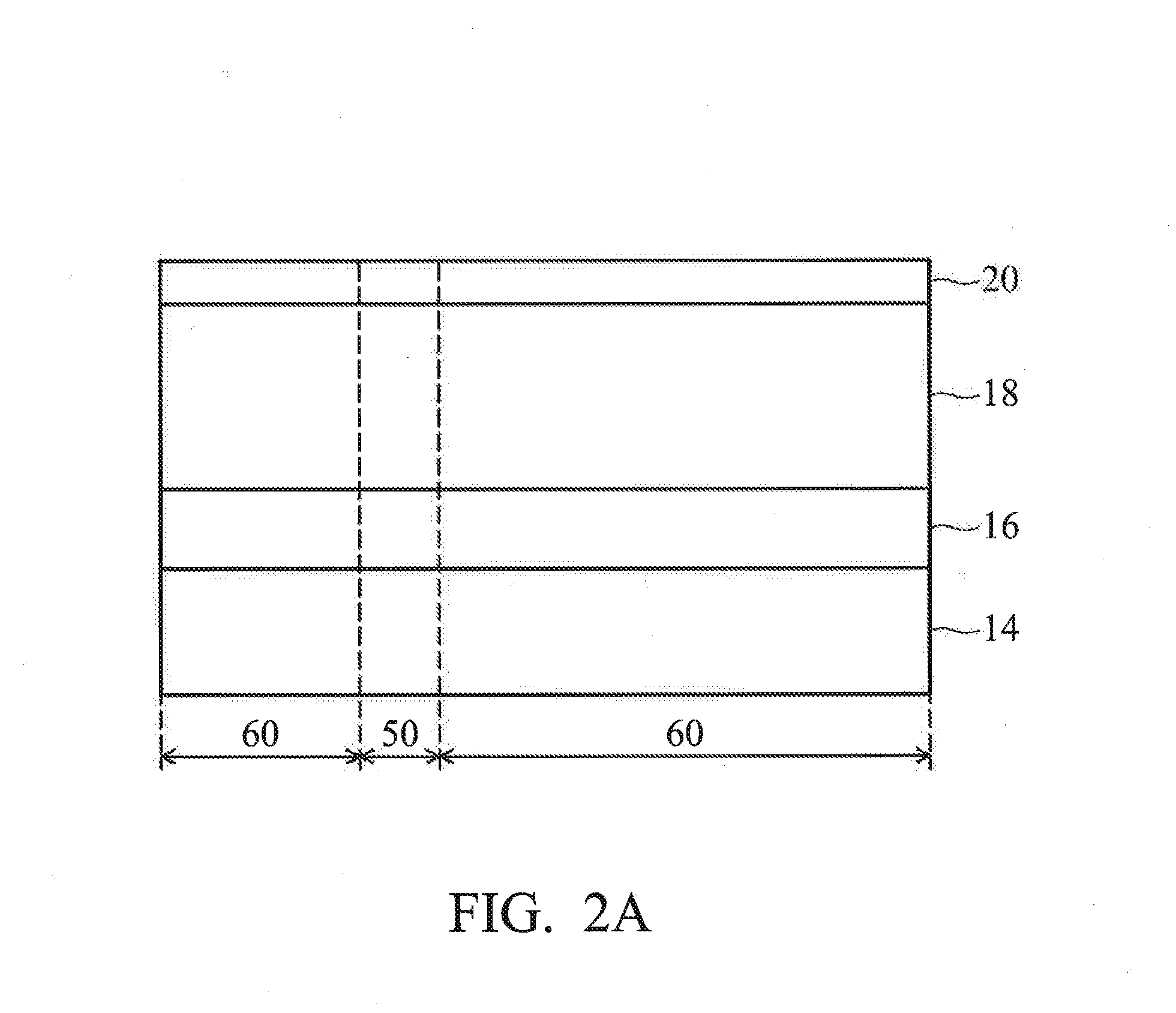

In sophisticated manufacturing techniques, the work function and thus the threshold voltage of transistor elements may be adjusted in an early manufacturing stage by providing a work function adjusting species within the high-k dielectric material with substantially the same spatial distribution in the gate dielectric materials of different thickness. After the incorporation of the work function adjusting species, the final thickness of the gate dielectric materials may be adjusted by selectively forming an additional dielectric layer so that the further patterning of the gate electrode structures may be accomplished with a high degree of compatibility to conventional manufacturing techniques. Consequently, extremely complicated processes for re-adjusting the threshold voltages of transistors having a different thickness gate dielectric material may be avoided.

Owner:GLOBALFOUNDRIES US INC

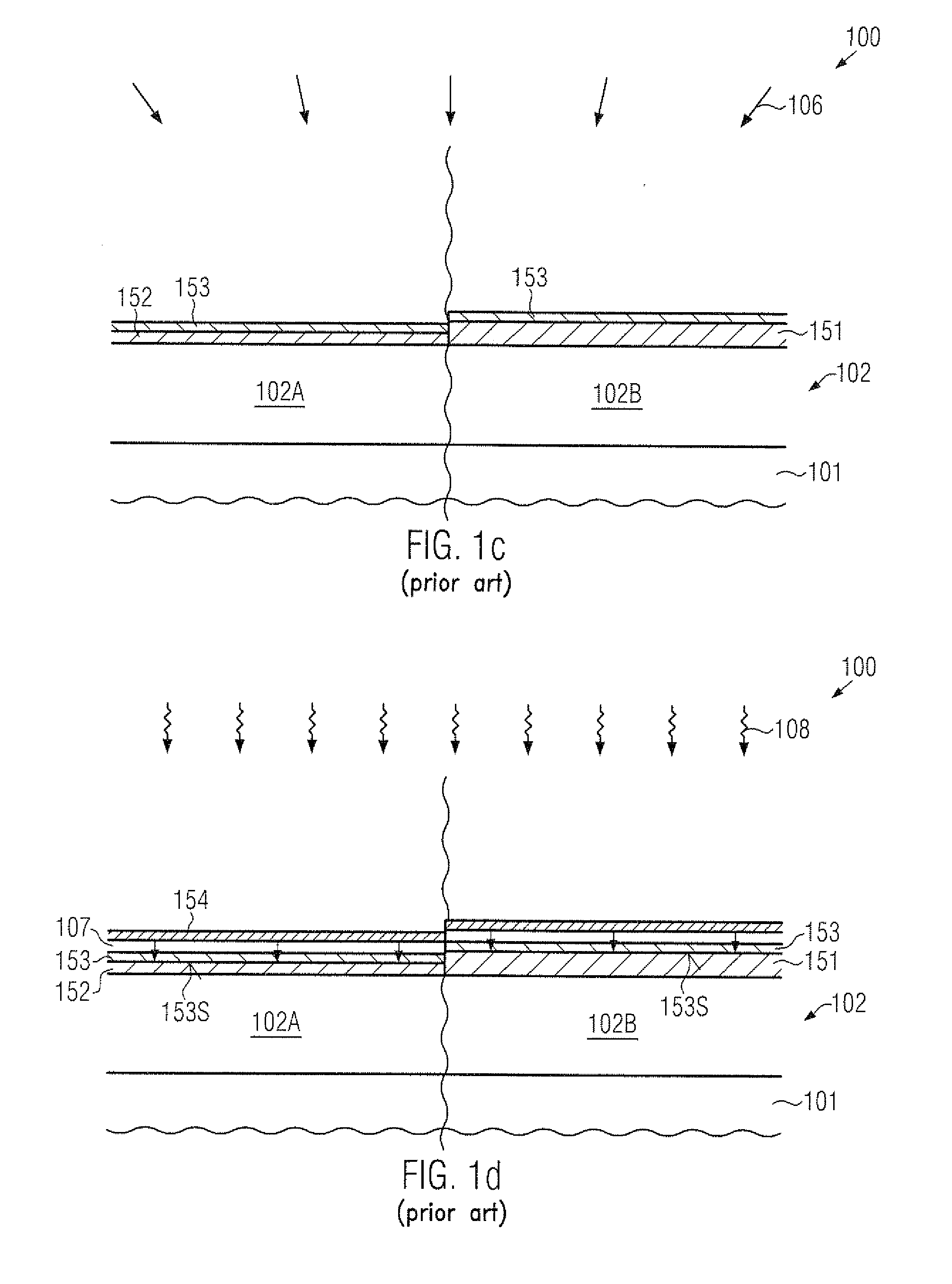

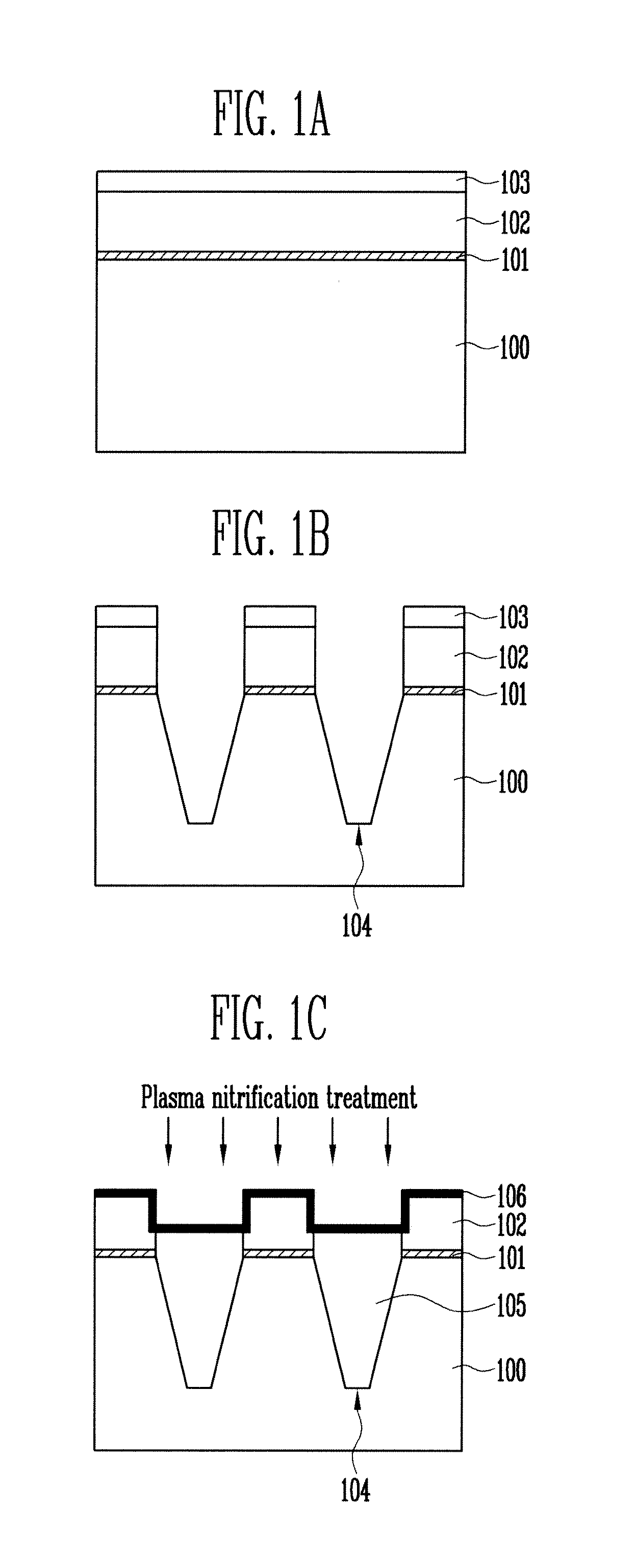

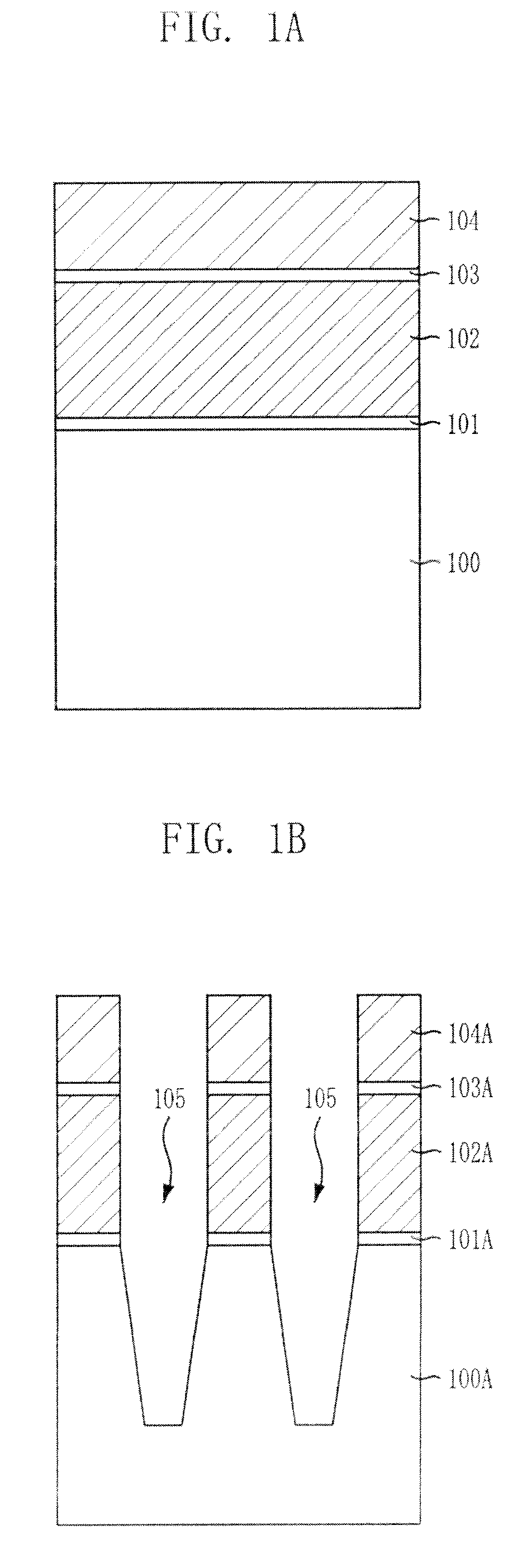

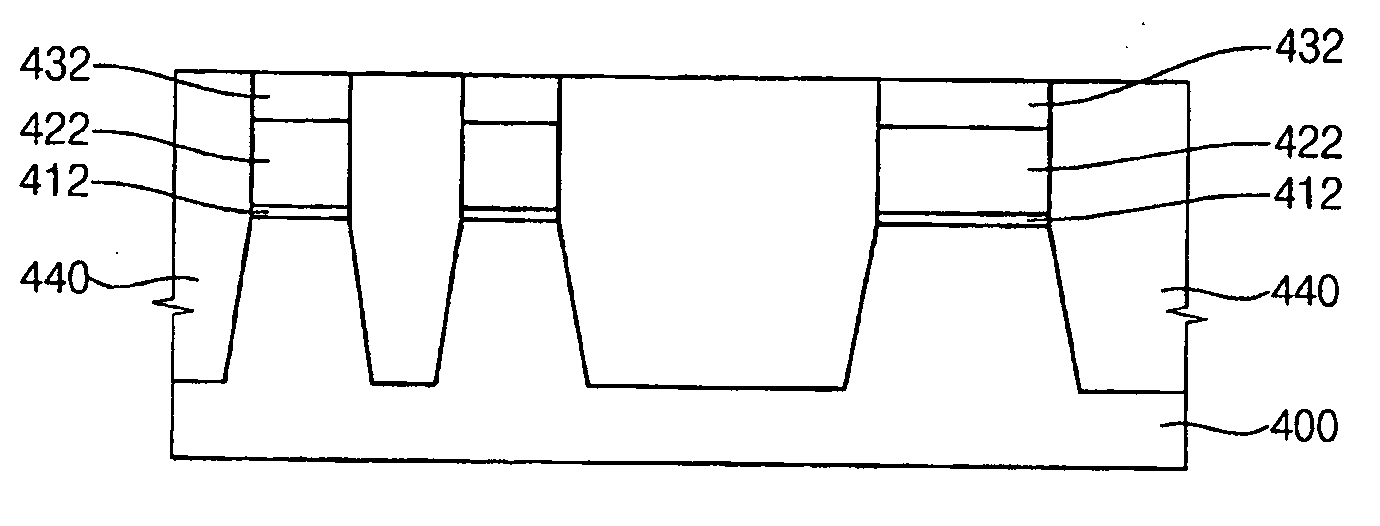

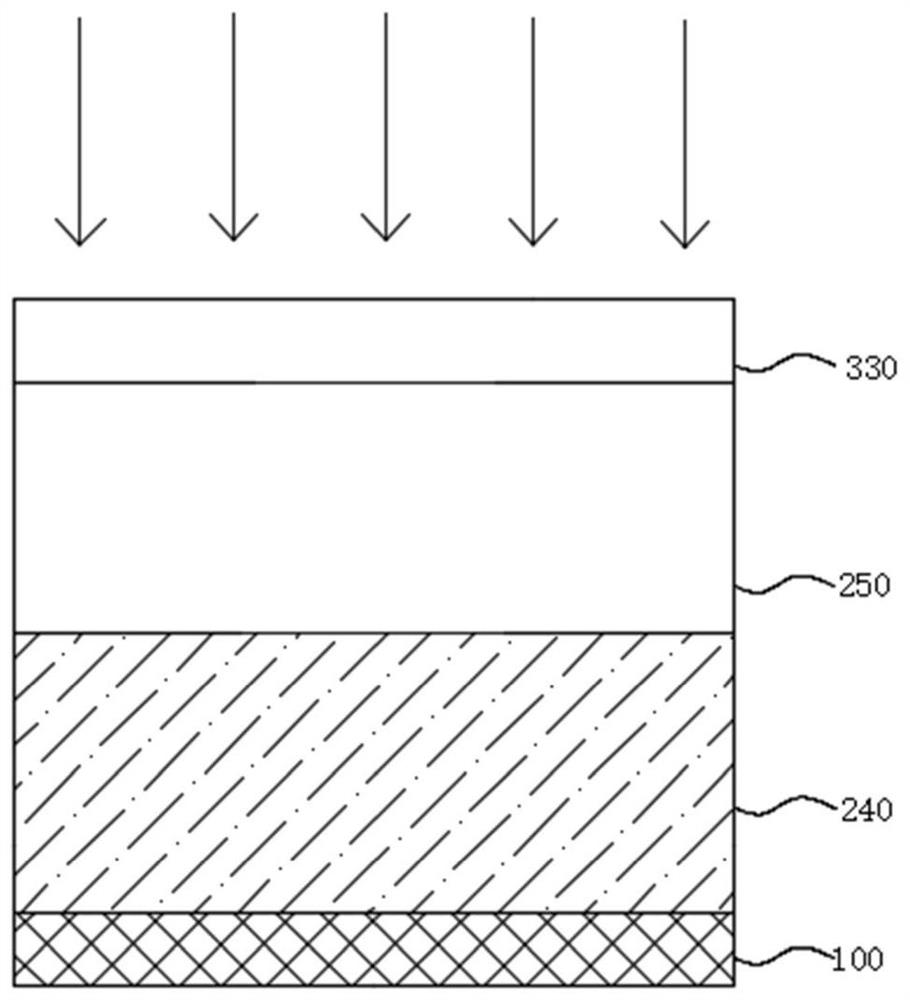

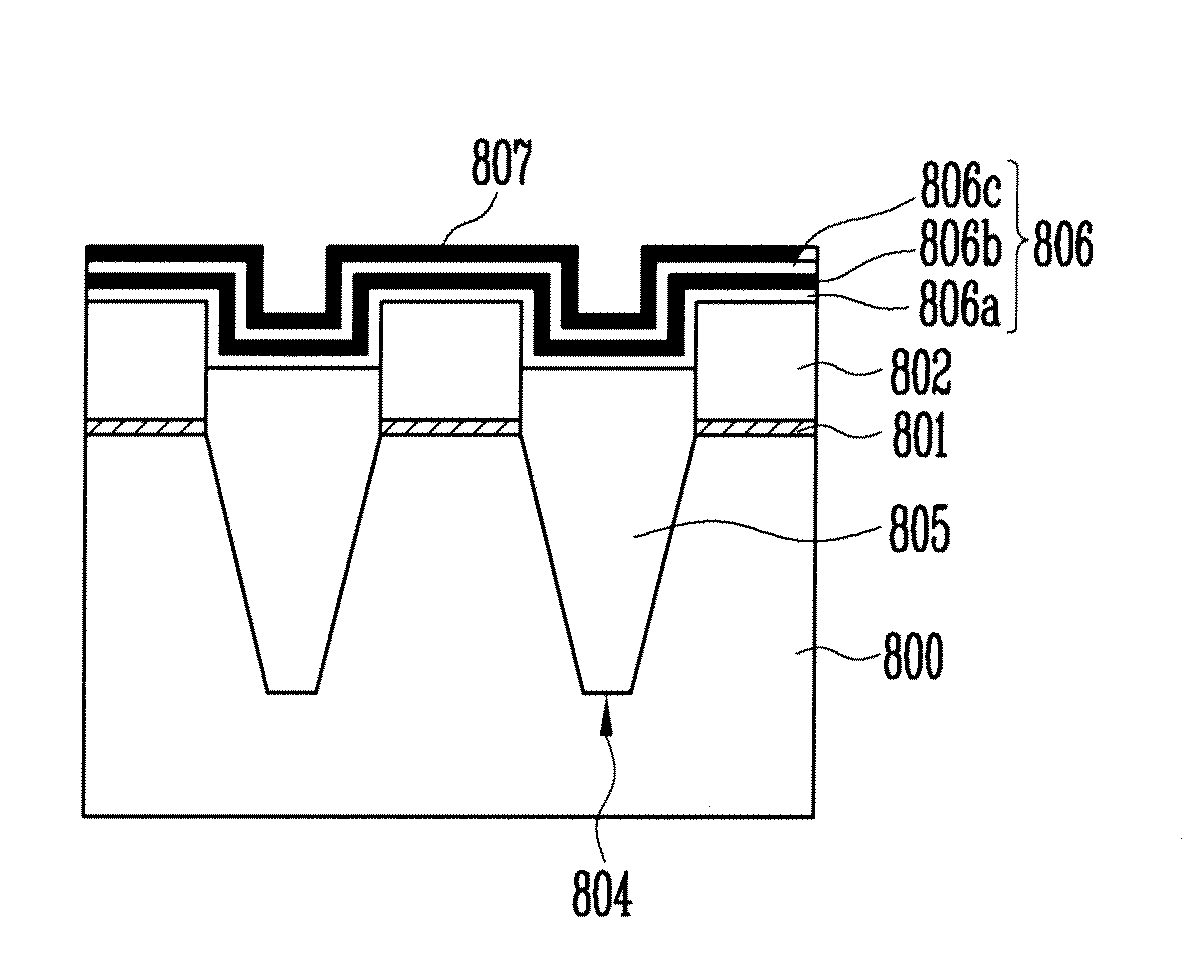

Method of Manufacturing Nonvolatile Memory Device

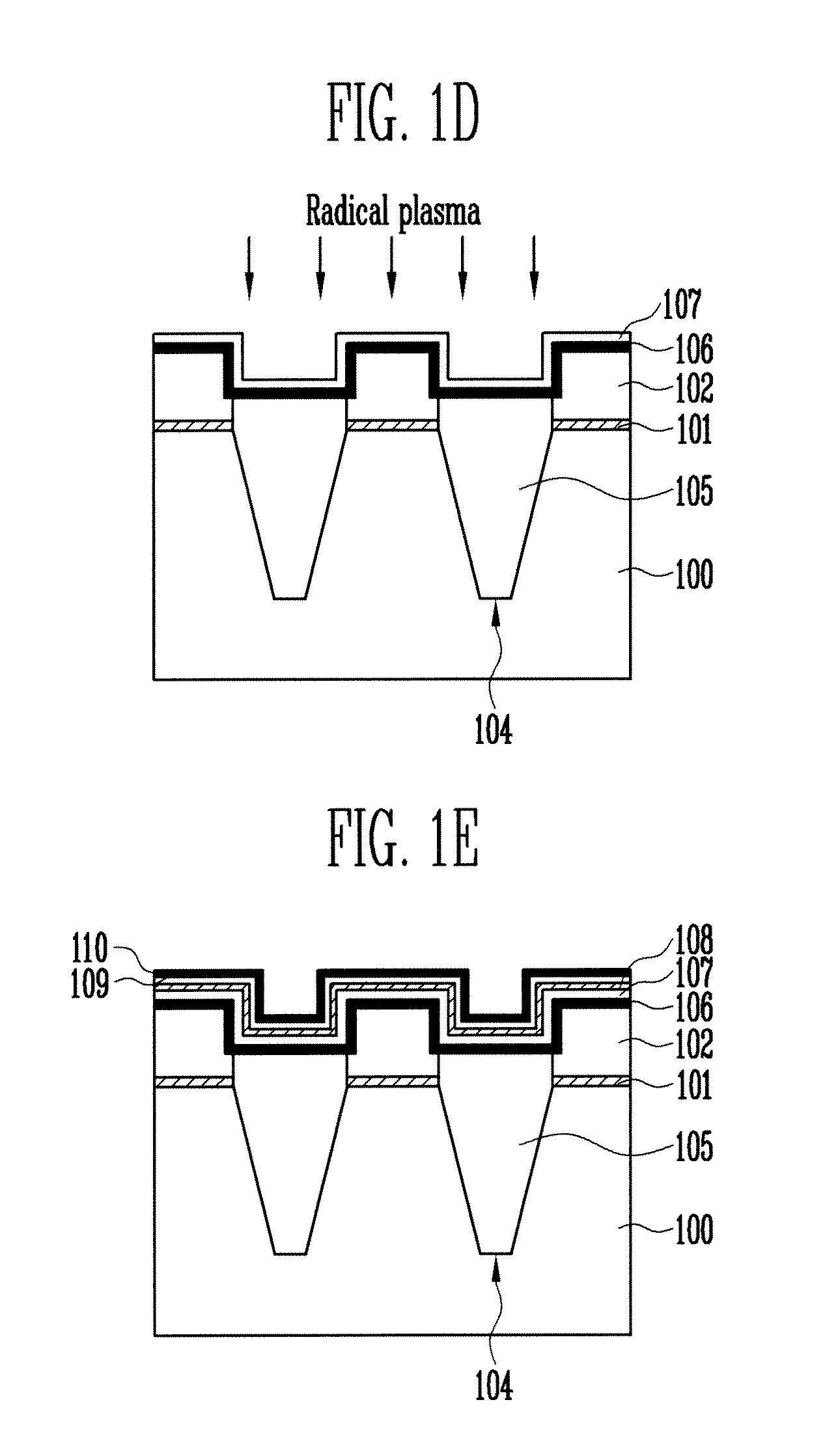

InactiveUS20100297826A1Suppress smile phenomenonImprove film qualitySolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerEngineering

In one embodiment of a method of manufacturing a nonvolatile memory device, a tunnel insulating layer and a charge trap layer are first formed over a semiconductor substrate that defines active regions and isolation regions. The tunnel insulating layer, the charge trap layer, and the semiconductor substrate formed in the isolation regions are etched to form trenches for isolation in the respective isolation regions. The trenches for isolation are filled with an insulating layer to form isolation layers in the respective trenches. A lower passivation layer is formed over an entire surface including top surfaces of the isolation layers. A first oxide layer is formed over an entire surface including the lower passivation layer. Meta-stable bond structures within the lower passivation layer are removed. A nitride layer, a second oxide layer, and an upper passivation layer are sequentially formed over an entire surface including the first oxide layer.

Owner:SK HYNIX INC

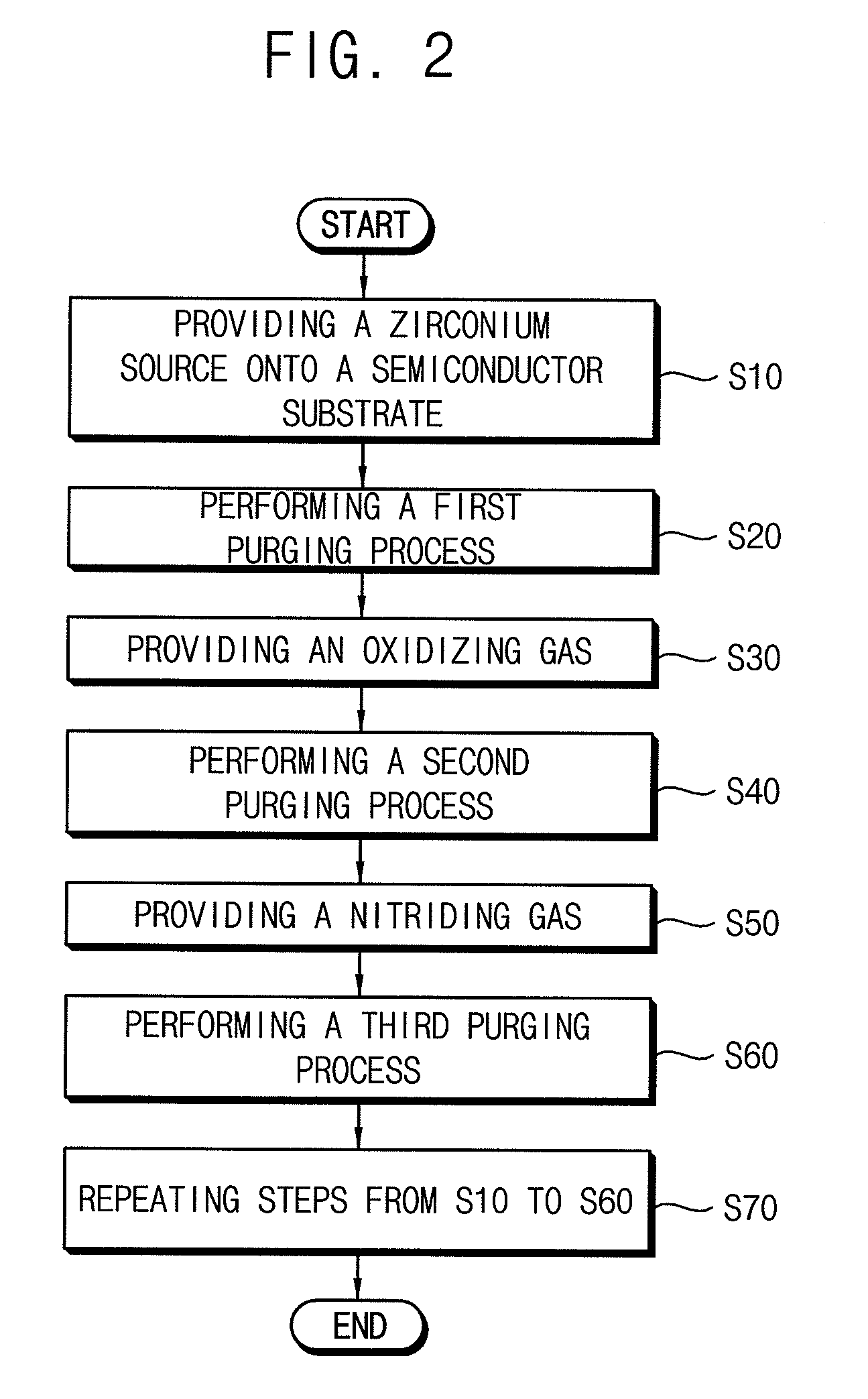

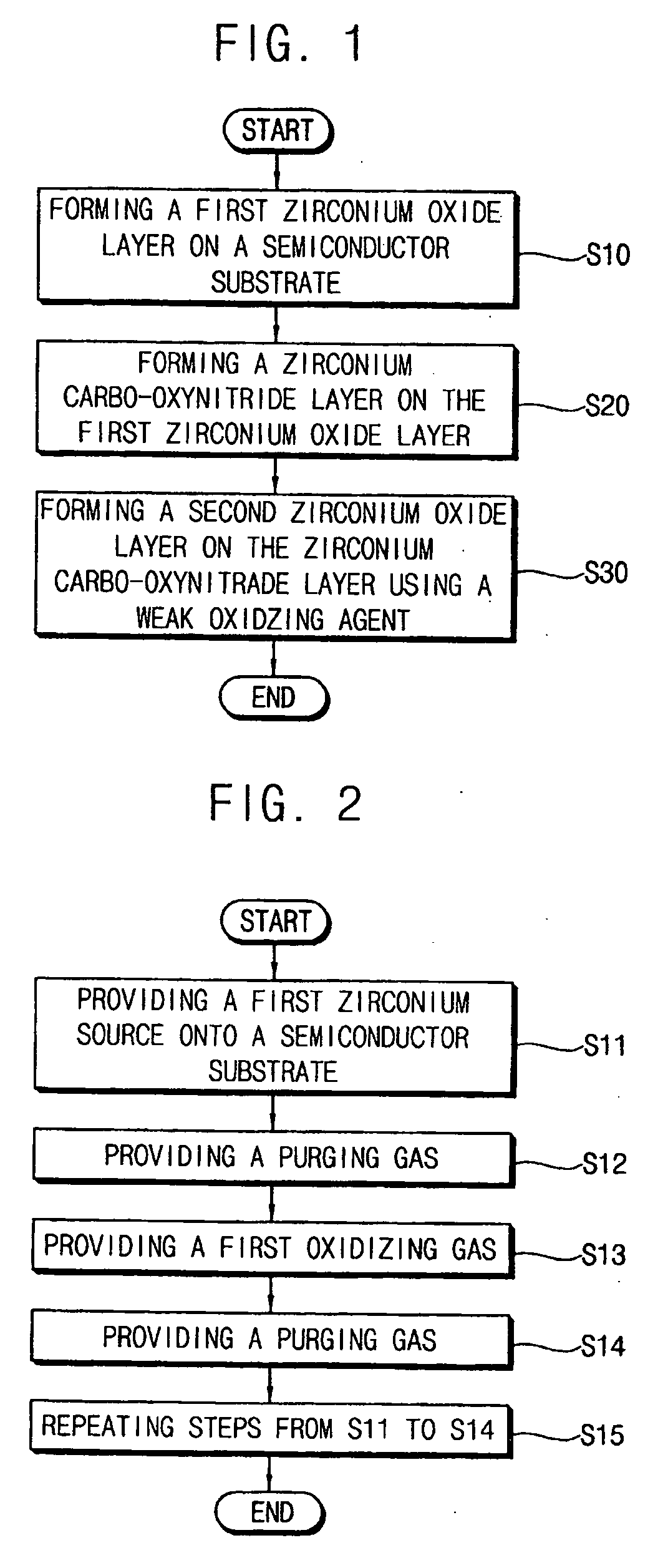

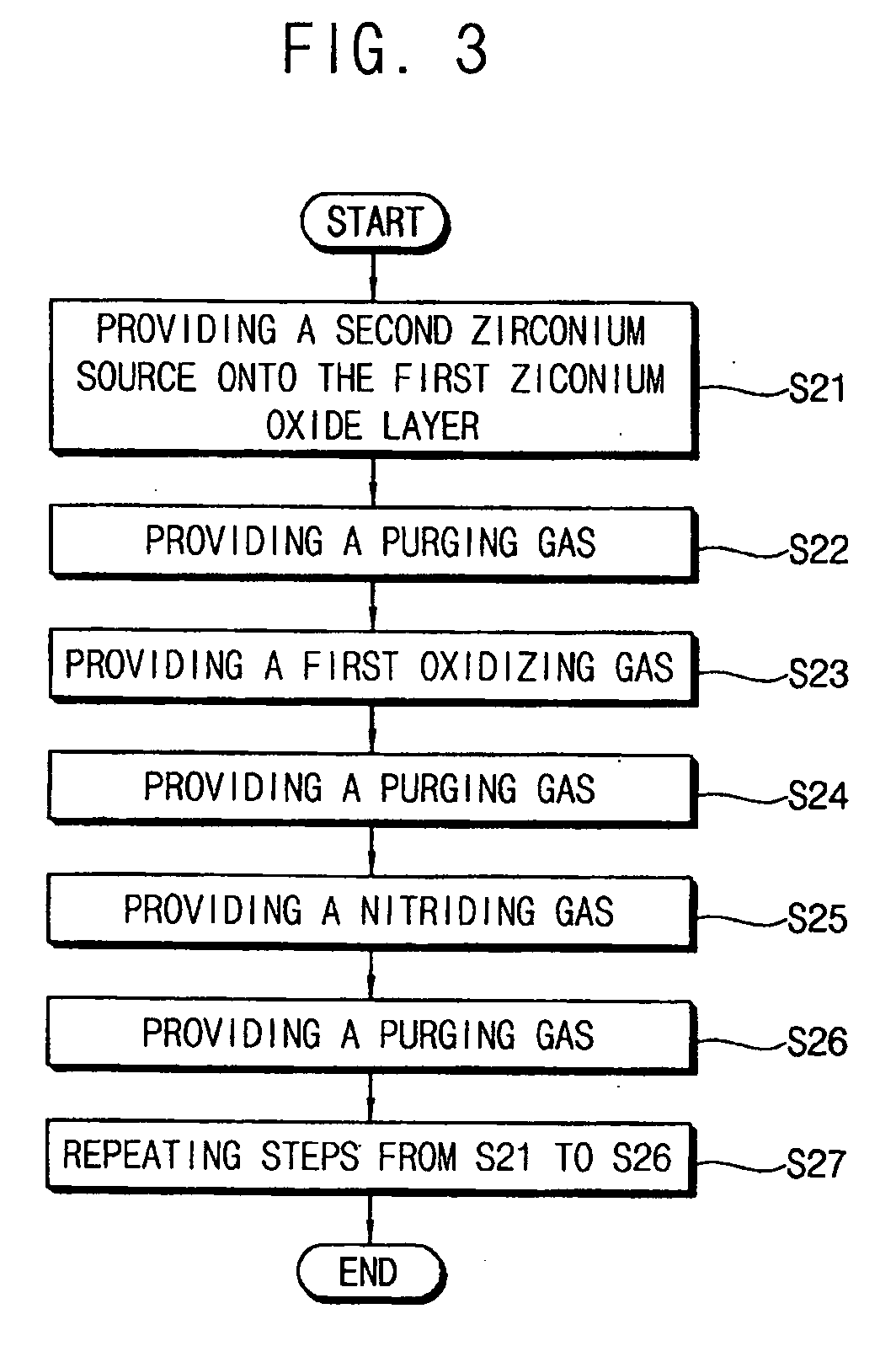

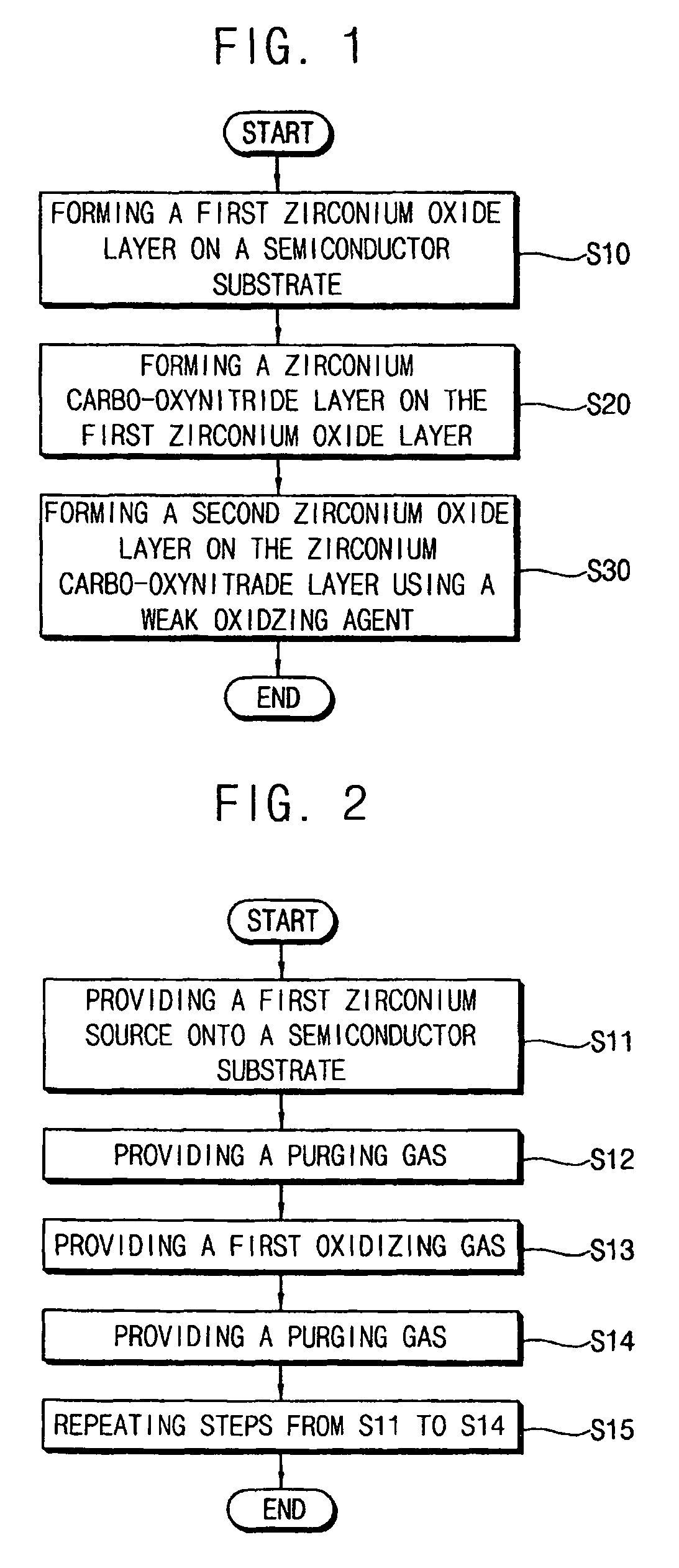

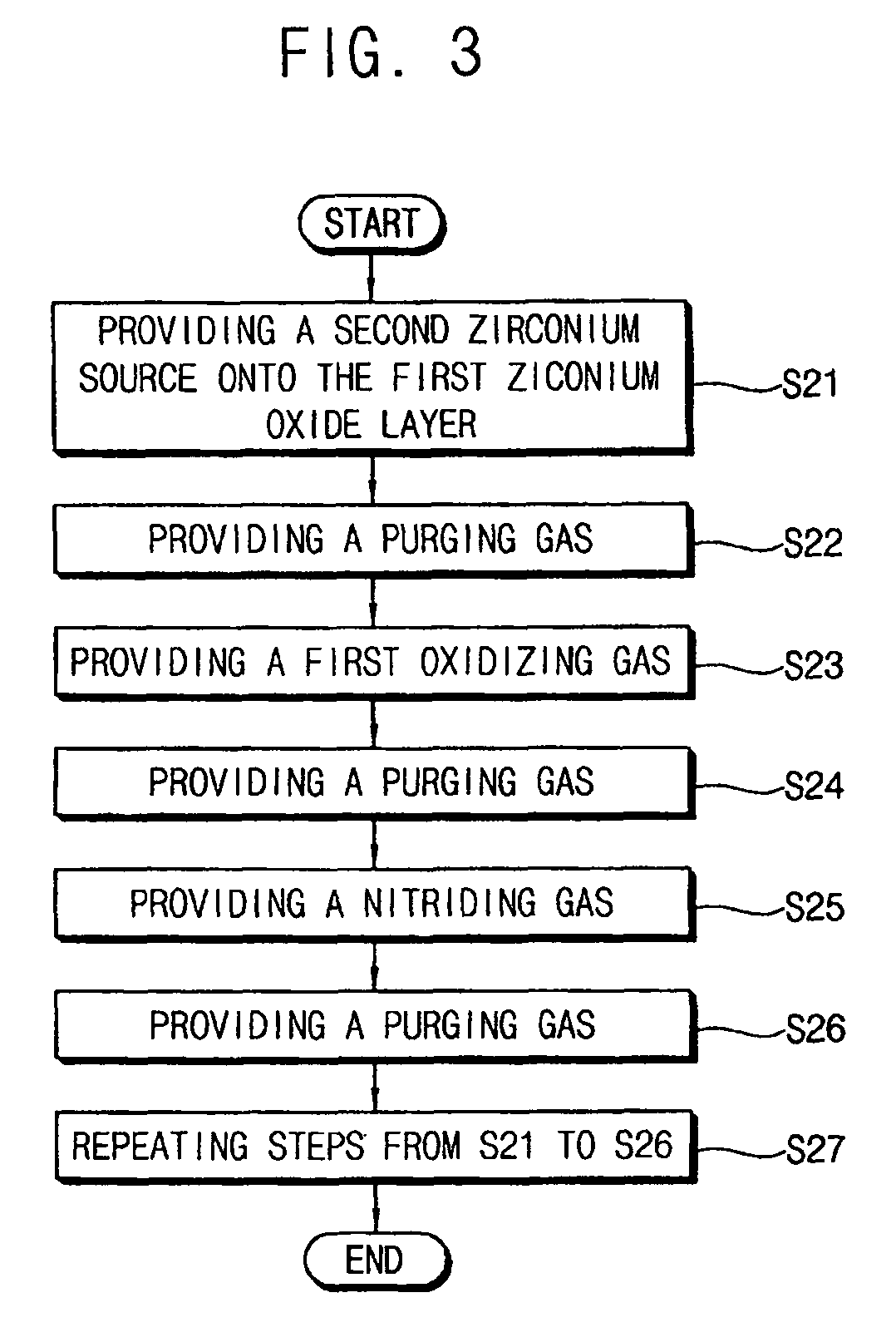

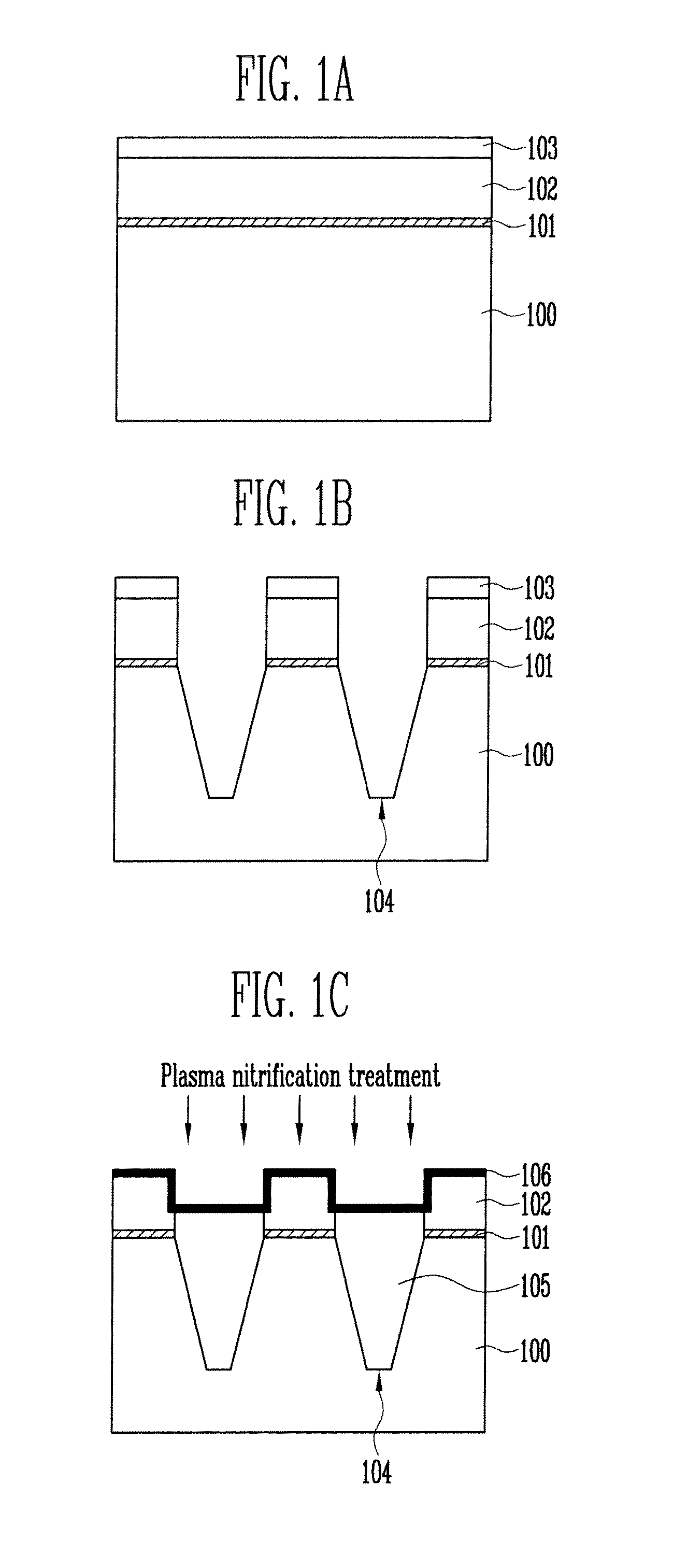

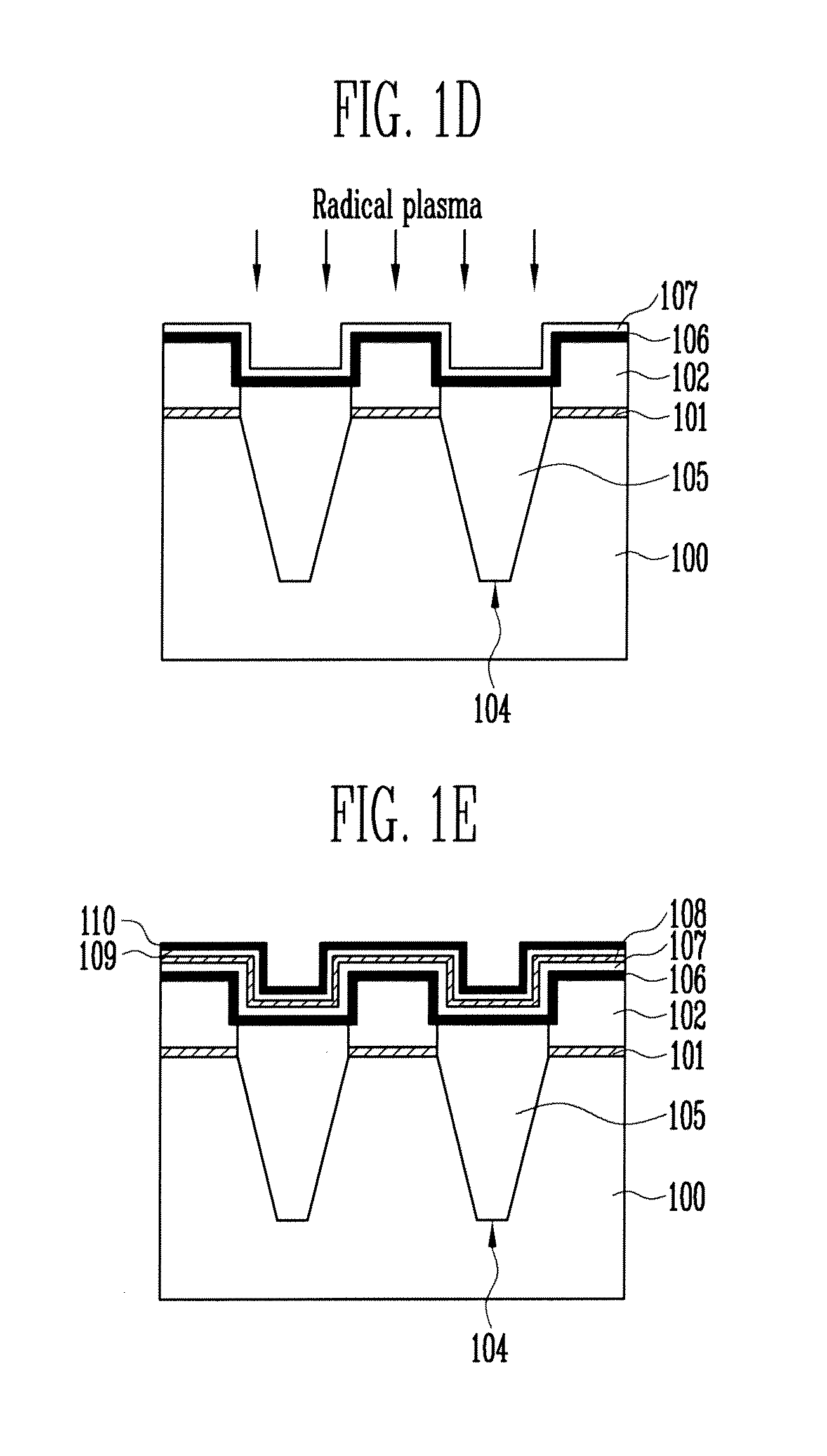

Method of manufacturing semiconductor devices

ActiveUS20090233434A1Stable structureThreshold voltage uniformSemiconductor/solid-state device manufacturingCapacitorsDevice materialNitrogen

In semiconductor devices and methods of manufacturing semiconductor devices, a zirconium source having zirconium, carbon and nitrogen is provided onto a substrate to form an adsorption layer of the zirconium source on the substrate. A first purging process is performed to remove a non-adsorbed portion of the zirconium source. An oxidizing gas is provided onto the adsorption layer to form an oxidized adsorption layer of the zirconium source on the substrate. A second purging process is performed to remove a non-reacted portion of the oxidizing gas. A nitriding gas is provided on the oxidized adsorption layer to form a zirconium carbo-oxynitride layer on the substrate, and a third purging process is provided to remove a non-reacted portion of the nitriding gas.

Owner:SAMSUNG ELECTRONICS CO LTD

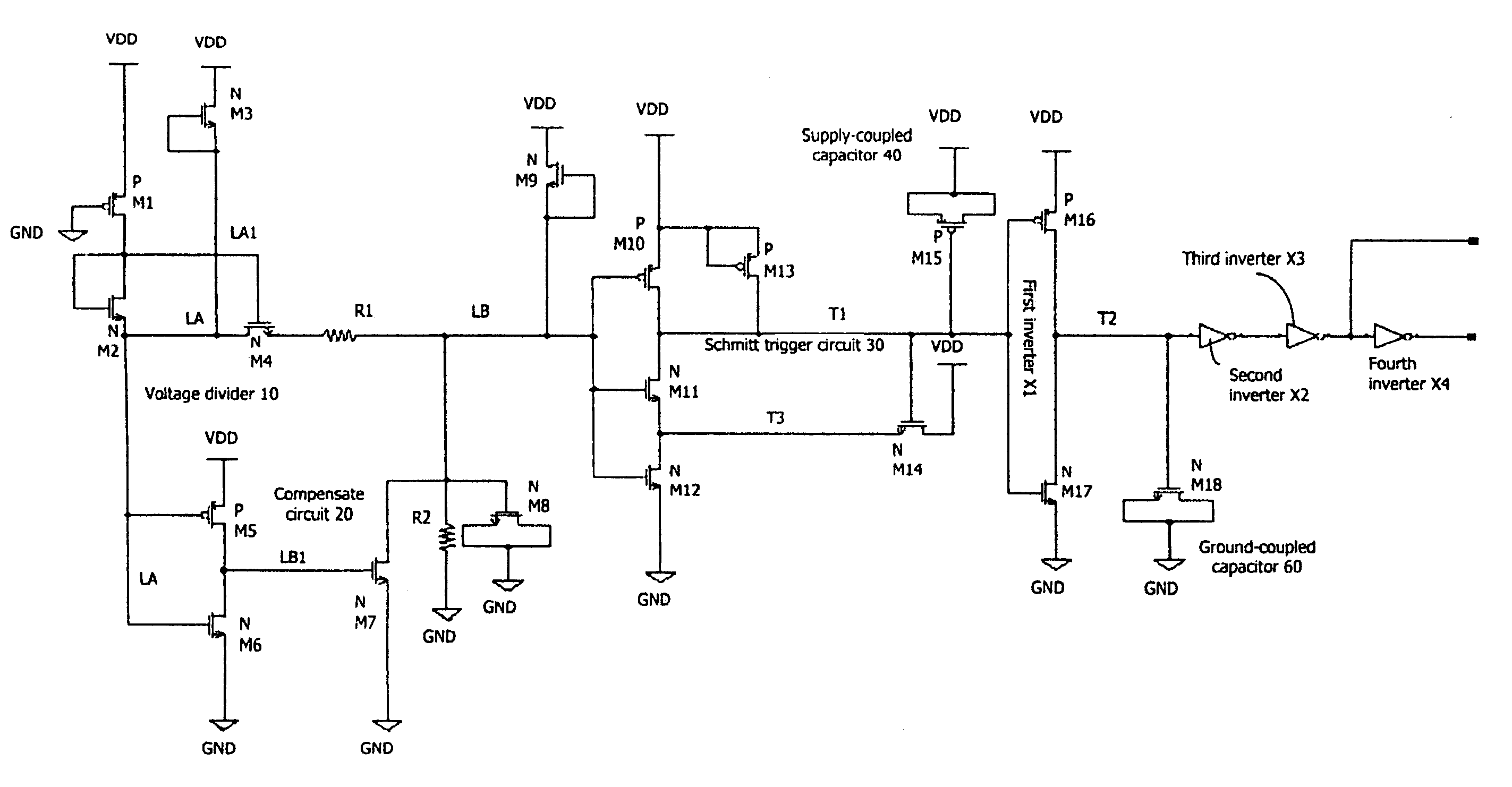

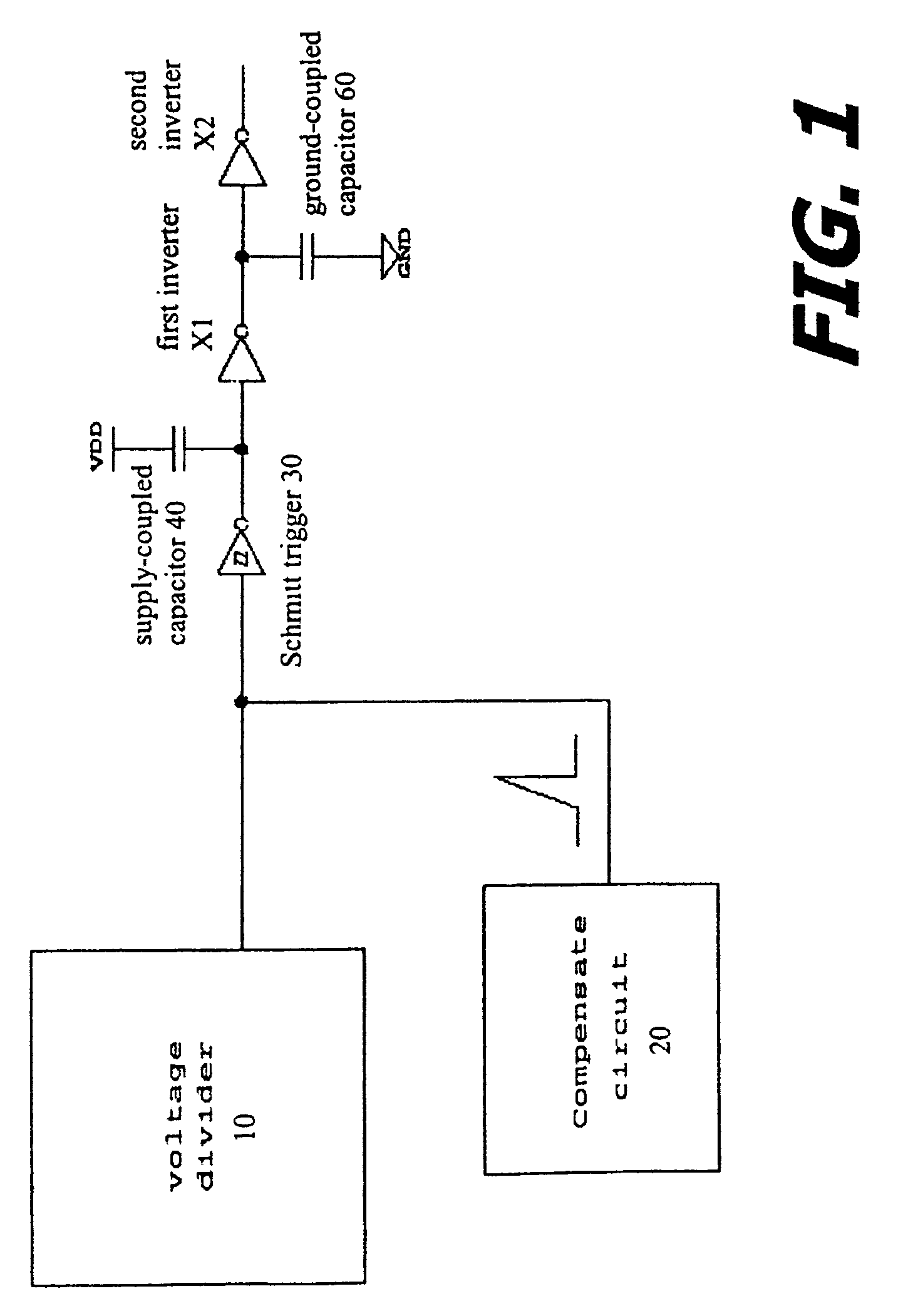

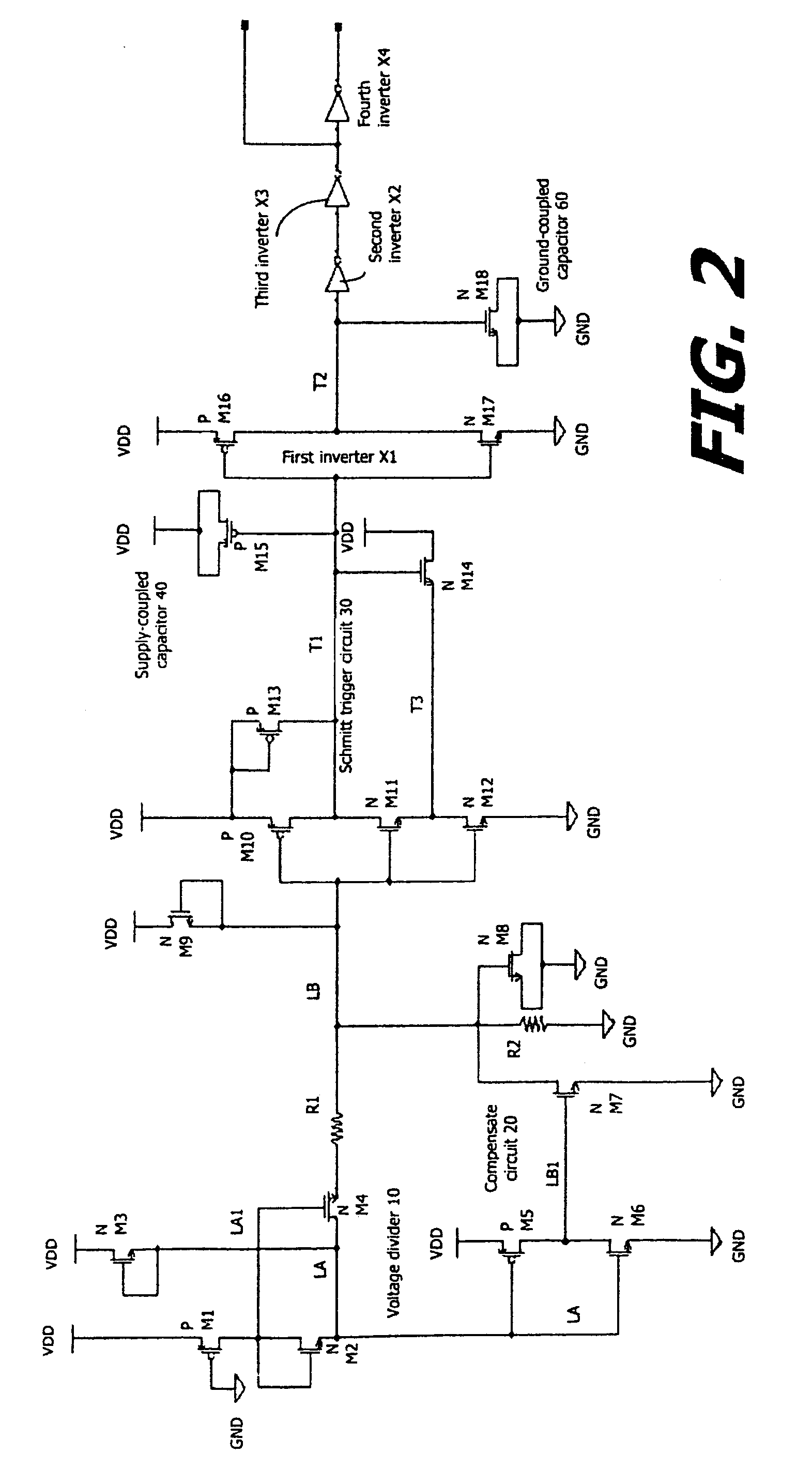

Power-on reset circuit with supply voltage and temperature immunity, ultra-low DC leakage current, and fast power crash reaction

InactiveUS7135898B2Threshold voltage uniformEliminate needPulse automatic controlElectronic switchingPower-on resetElectricity

A power-on reset circuit includes a Schmitt trigger circuit, a voltage divider, and a compensate circuit. The Schmitt trigger circuit includes a plurality of MOS devices of a uniform threshold voltage (Vt) for determining a power reset trigger level. The voltage divider is coupled to an input of the Schmitt trigger circuit for tracking the supply signal. The compensate circuit is operative to generate a small reset pulse to compensate for temperature and the supply signal variation effect.

Owner:MACRONIX INT CO LTD

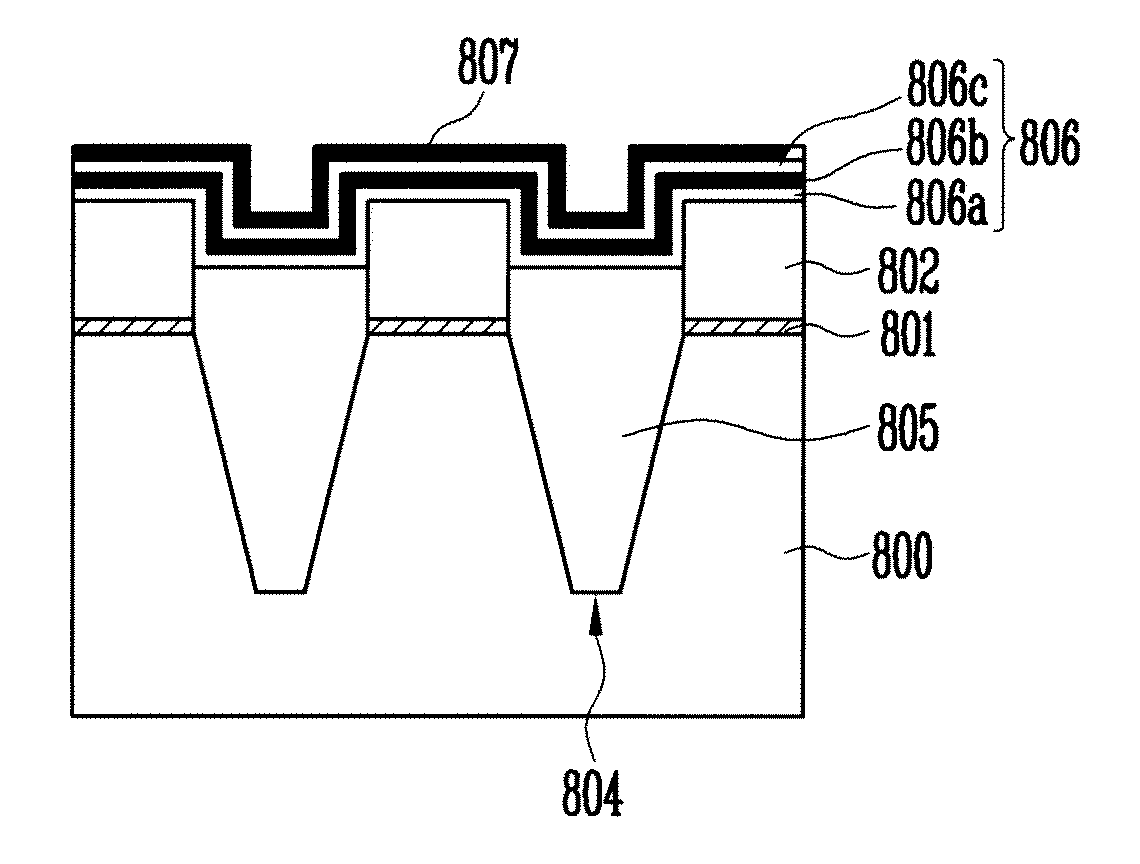

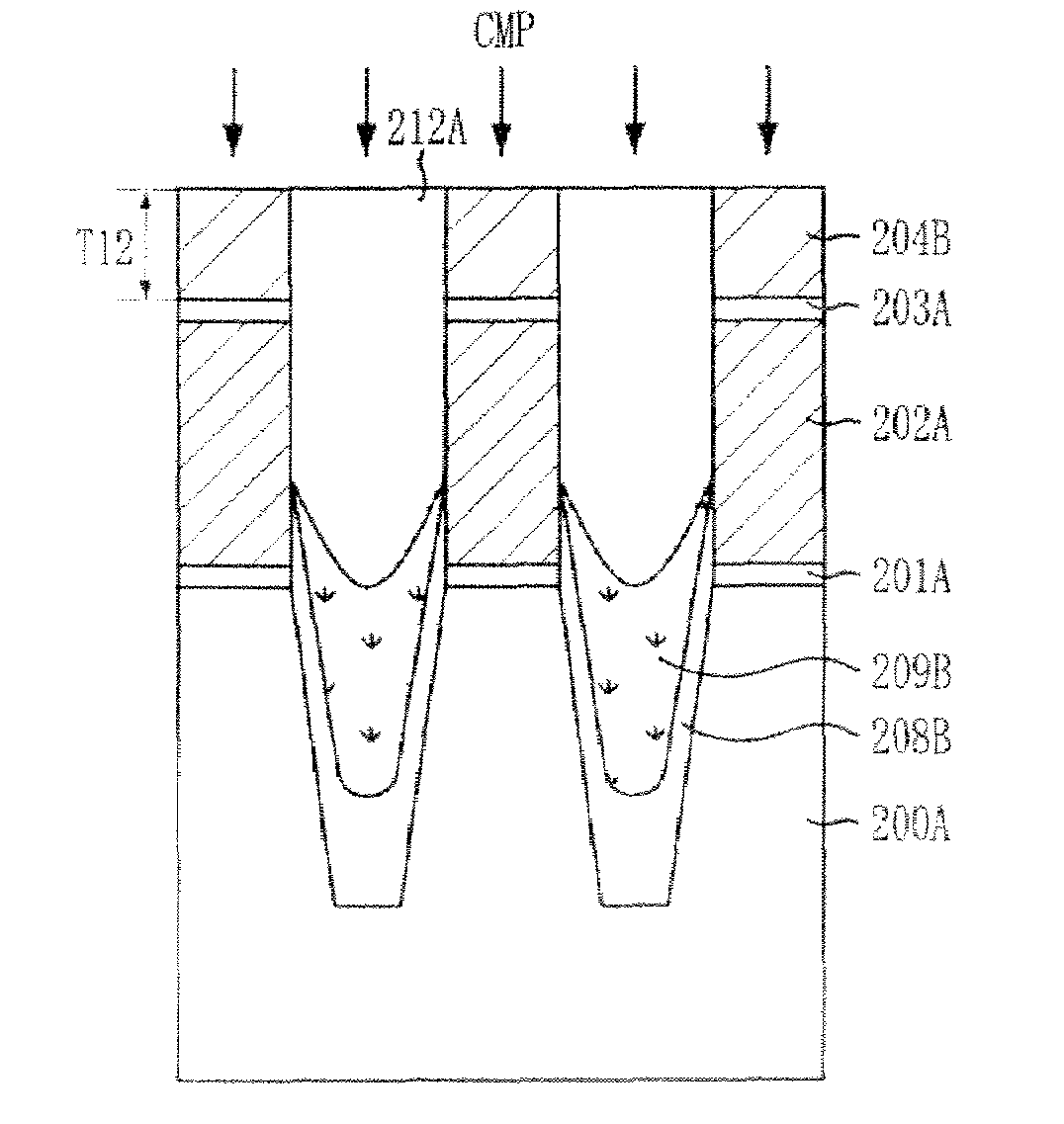

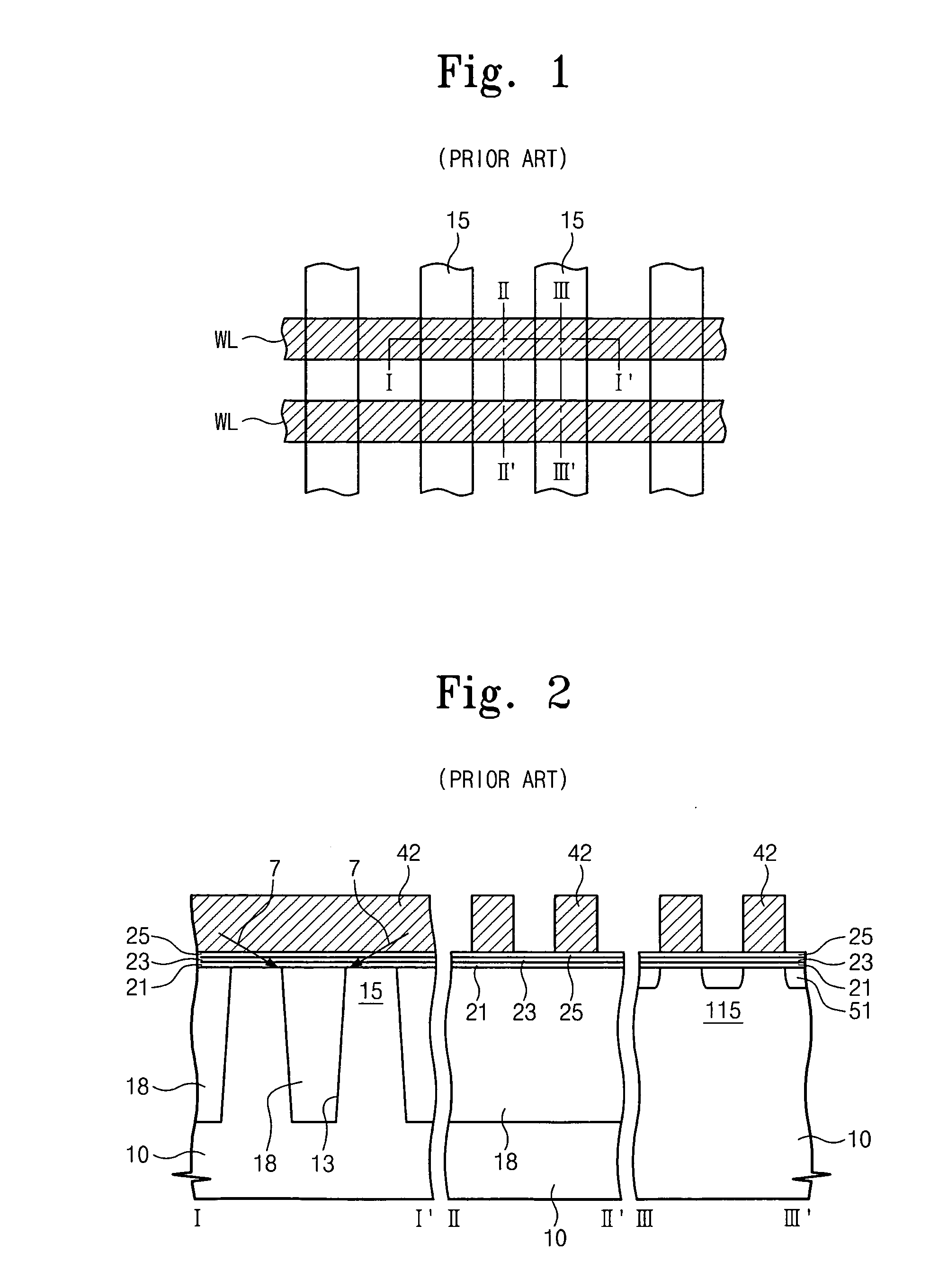

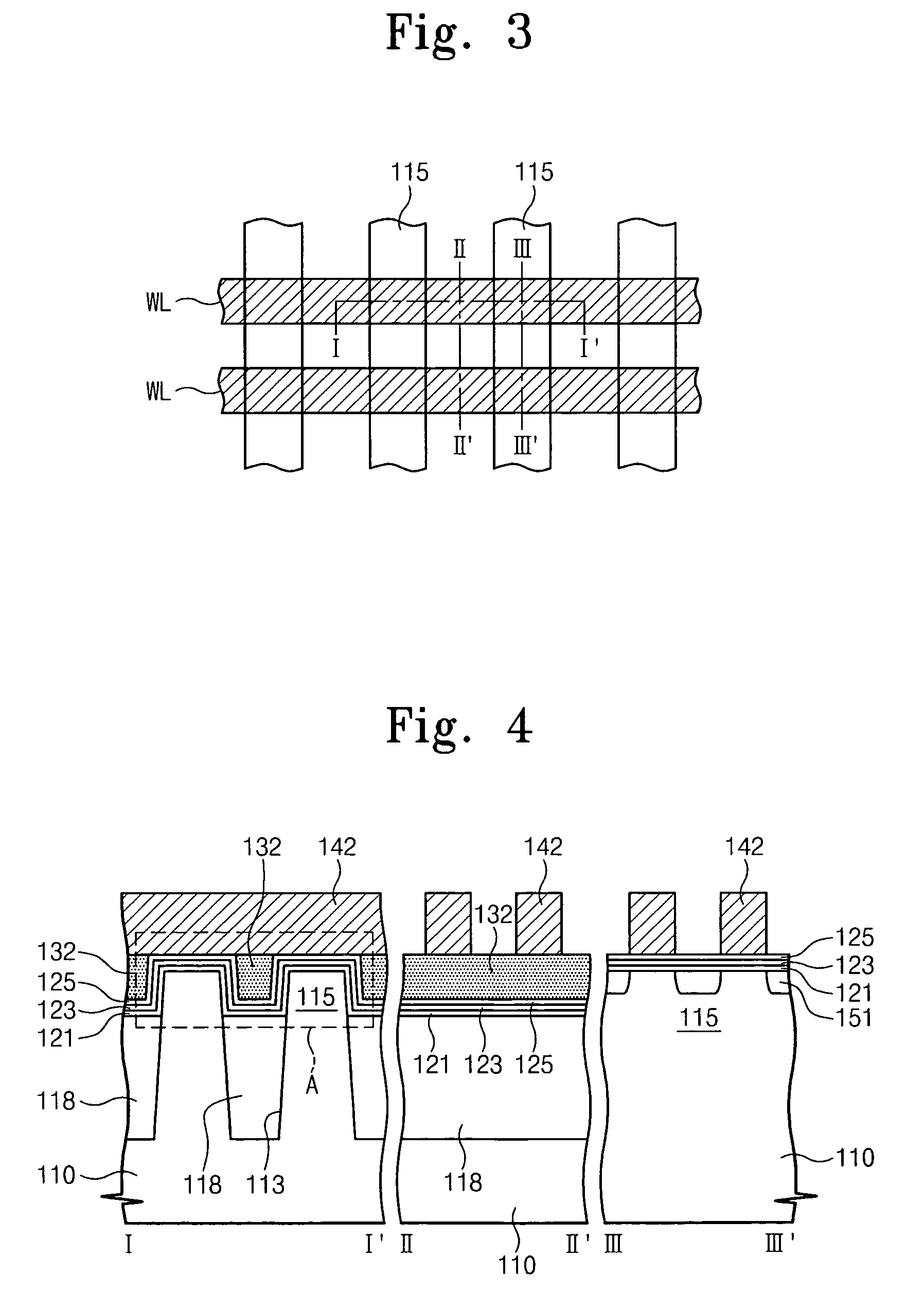

Method for fabricating nonvolatile memory device

InactiveUS7563689B2Minimizing non-uniformityThreshold voltage uniformSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A method for fabricating a nonvolatile memory device includes forming a gate insulation layer, a first gate conductive layer, a first sacrificial layer, and a second sacrificial layer over a substrate, etching the first and second sacrificial layers, the first gate conductive layer, the gate insulation layer, and the substrate to form trenches, forming a first insulation layer to fill the trenches, polishing the first insulation layer using the etched second sacrificial layer as a polish stop layer, removing the second sacrificial layer, recessing the first insulation layer inside the trenches, forming a second insulation layer to fill a space produced inside the trenches by the recessing of the first insulation layer, and polishing the second insulation layer using the etched first sacrificial layer as a polish stop layer.

Owner:SK HYNIX INC

Work function adjustment in high-k gate stacks including gate dielectrics of different thickness

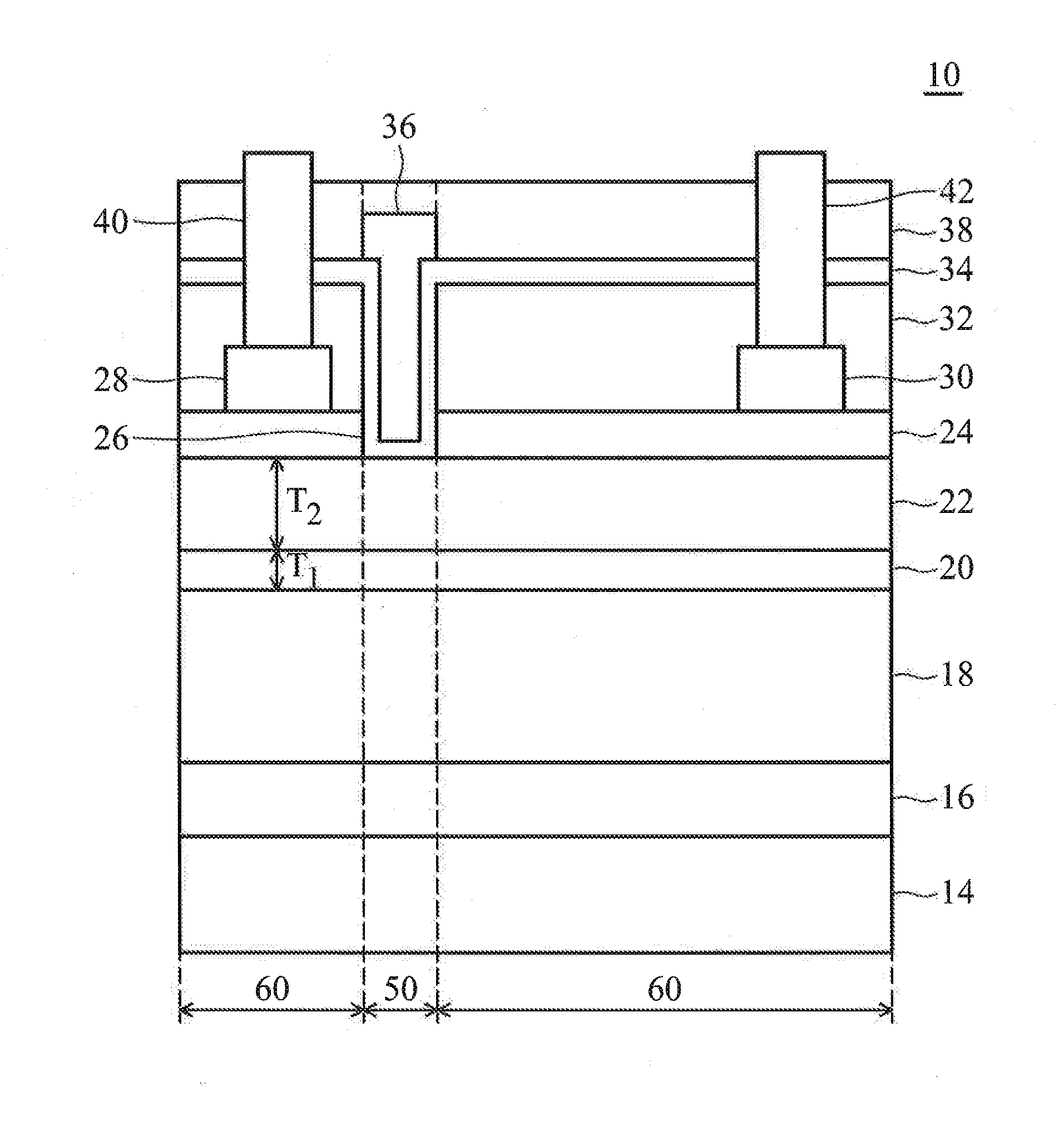

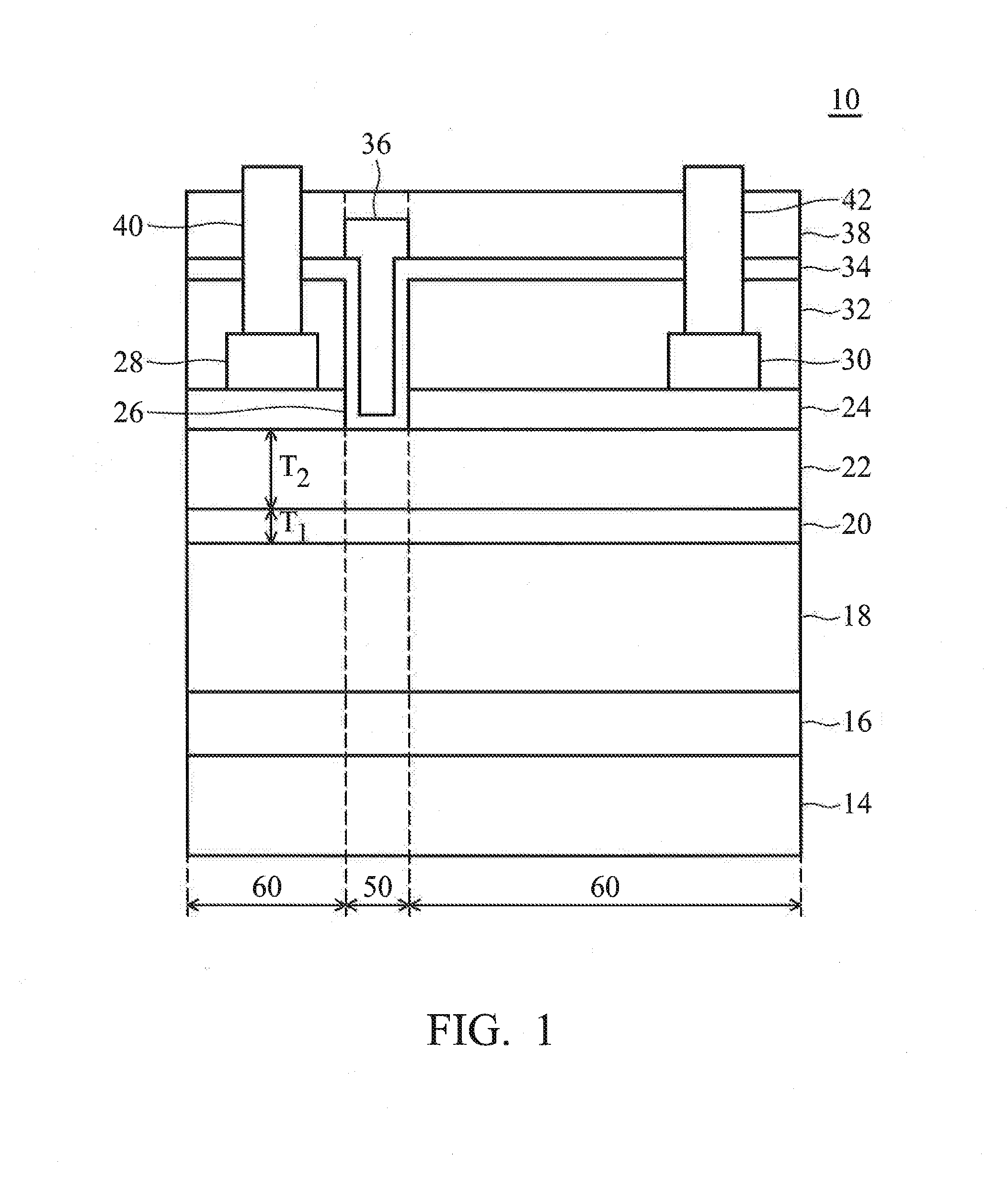

ActiveUS8349695B2Improve evenlyReduce thicknessTransistorSolid-state devicesGate dielectricWork function

In sophisticated manufacturing techniques, the work function and thus the threshold voltage of transistor elements may be adjusted in an early manufacturing stage by providing a work function adjusting species within the high-k dielectric material with substantially the same spatial distribution in the gate dielectric materials of different thickness. After the incorporation of the work function adjusting species, the final thickness of the gate dielectric materials may be adjusted by selectively forming an additional dielectric layer so that the further patterning of the gate electrode structures may be accomplished with a high degree of compatibility to conventional manufacturing techniques. Consequently, extremely complicated processes for re-adjusting the threshold voltages of transistors having a different thickness gate dielectric material may be avoided.

Owner:GLOBALFOUNDRIES U S INC

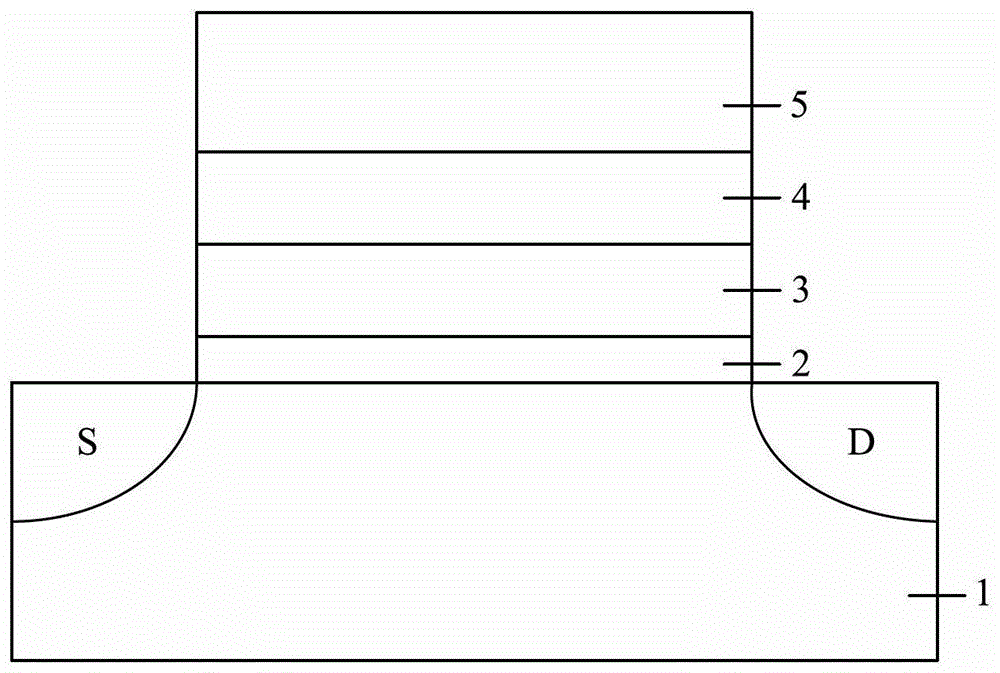

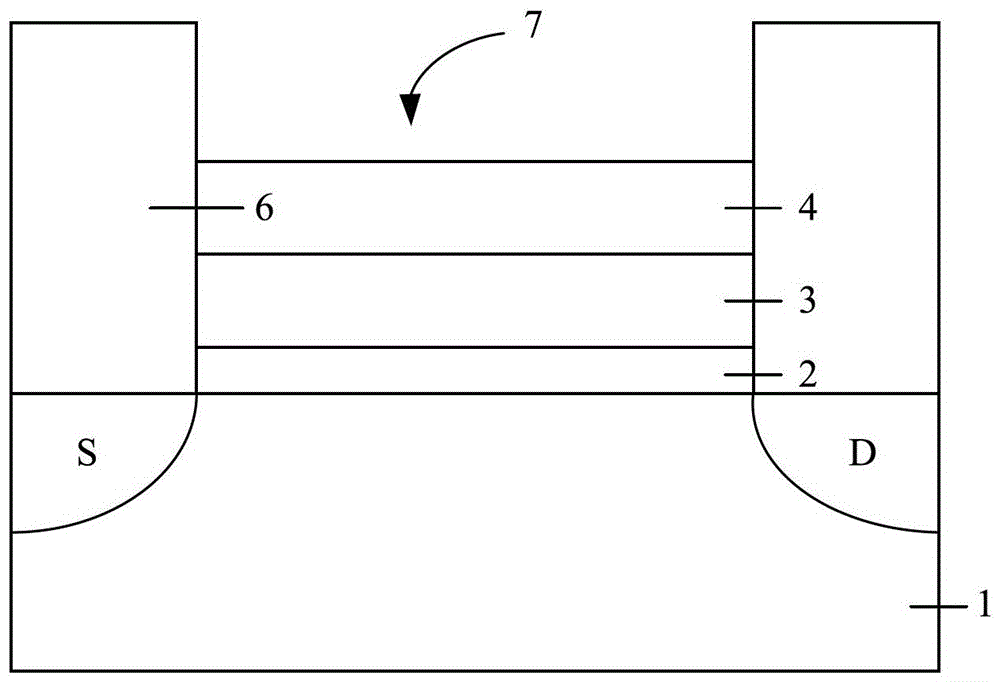

Field effect transistor device

ActiveUS20140042455A1Improve reliabilityThreshold voltage uniformSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

A field effect transistor device is provided by the invention. The field effect transistor device includes: a substrate; a buffer layer, a channel layer, and a first barrier layer sequentially disposed on the substrate; a two-dimensional electron gas controlling layer disposed on the first barrier layer; a second barrier layer disposed on the two-dimensional electron gas controlling layer, wherein the second barrier layer has a recess passing through the second barrier layer; and a gate electrode filled into the recess and separated from the second barrier layer and the two-dimensional electron gas controlling layer by an insulating layer.

Owner:NAT CENT UNIV +2

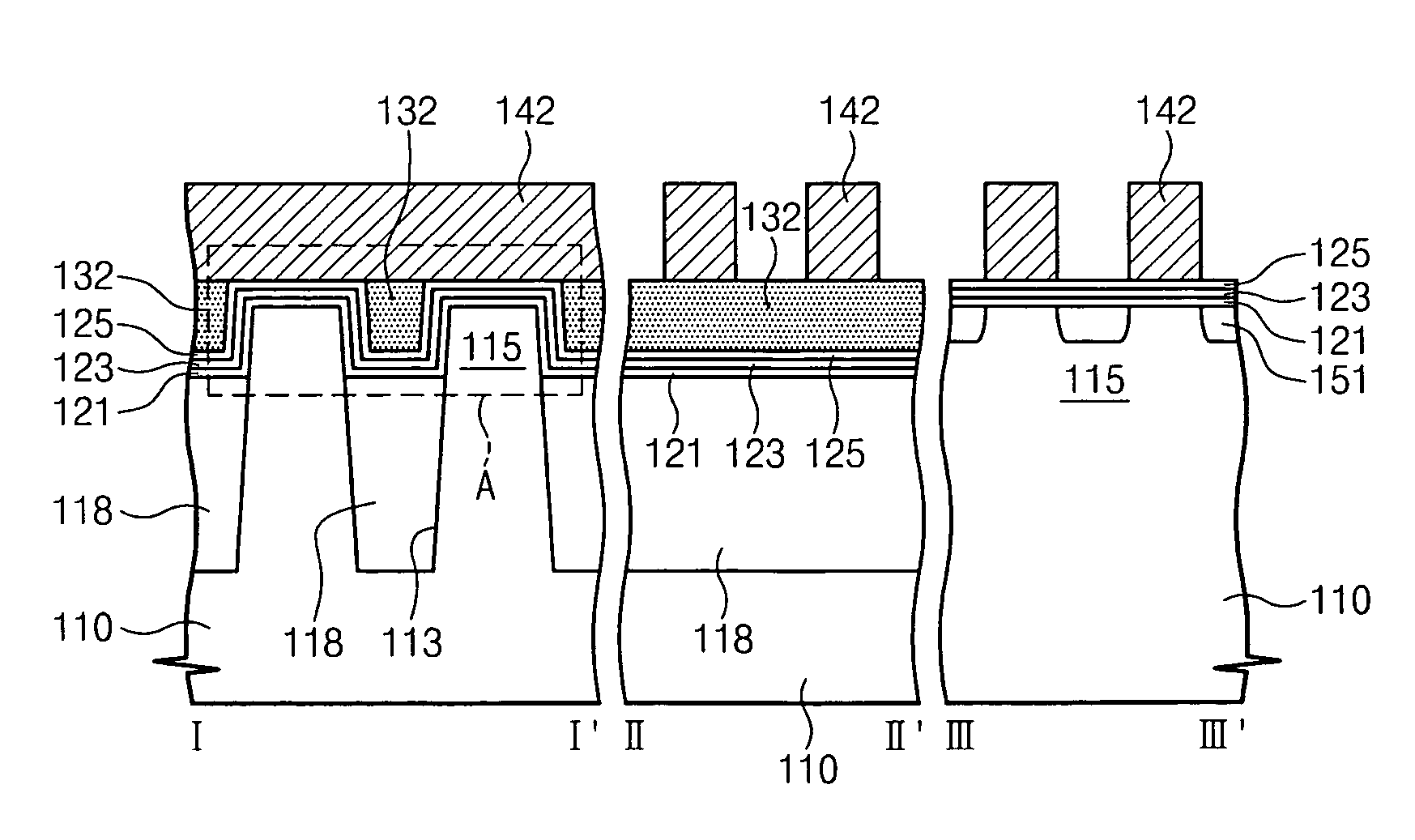

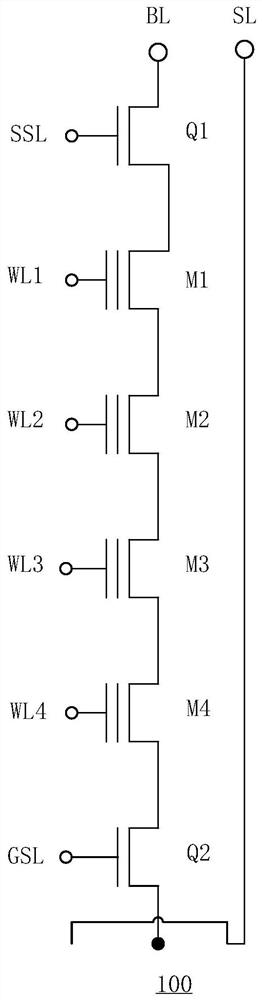

Nonvolatile semiconductor memory device and method of fabricating the same

InactiveUS20090159959A1Improve equipment reliabilityThreshold voltage uniformSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceEdge effects

A charge trap flash (CTF) memory cell and manufacturing method include a semiconductor substrate and an isolation region and an active region being formed in the substrate. A tunneling layer, a charge trapping layer and a blocking layer are formed on the isolation region and the active region. A resistance layer is formed on the blocking layer over the isolation region. The resistance layer prevents or substantially reduces trapping of electrons at the edges of the active region, i.e., the edge effect. As a result, after programming of the devices, the threshold voltages of the programmed cells are substantially uniform throughout the cells. This results in improved reliability of the devices.

Owner:SAMSUNG ELECTRONICS CO LTD

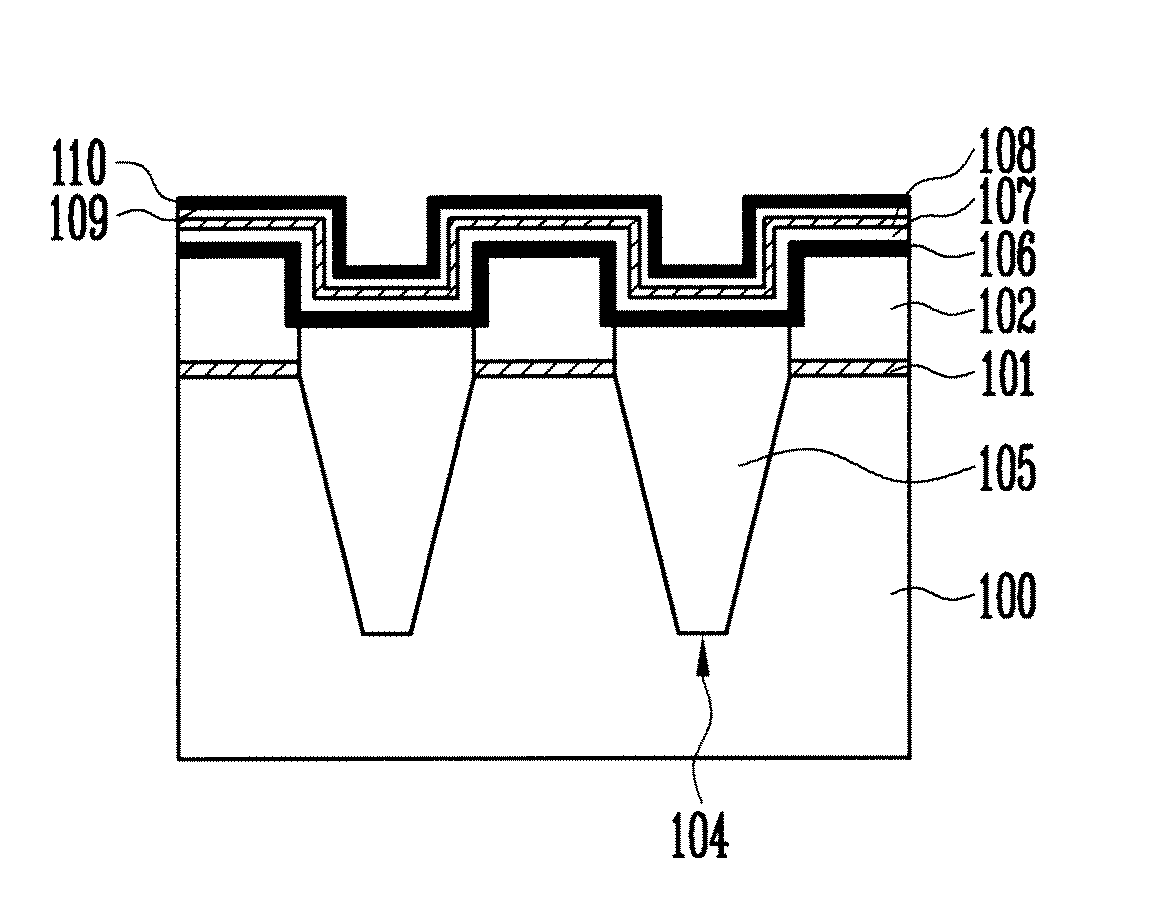

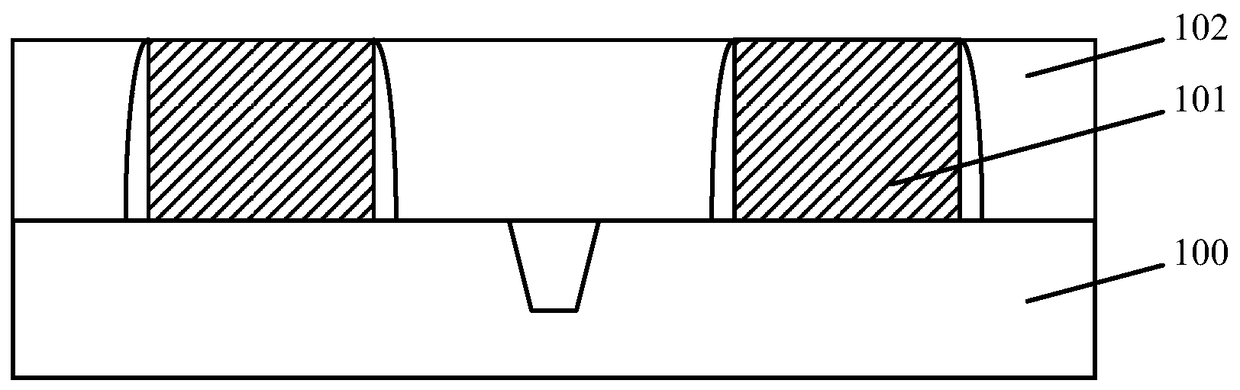

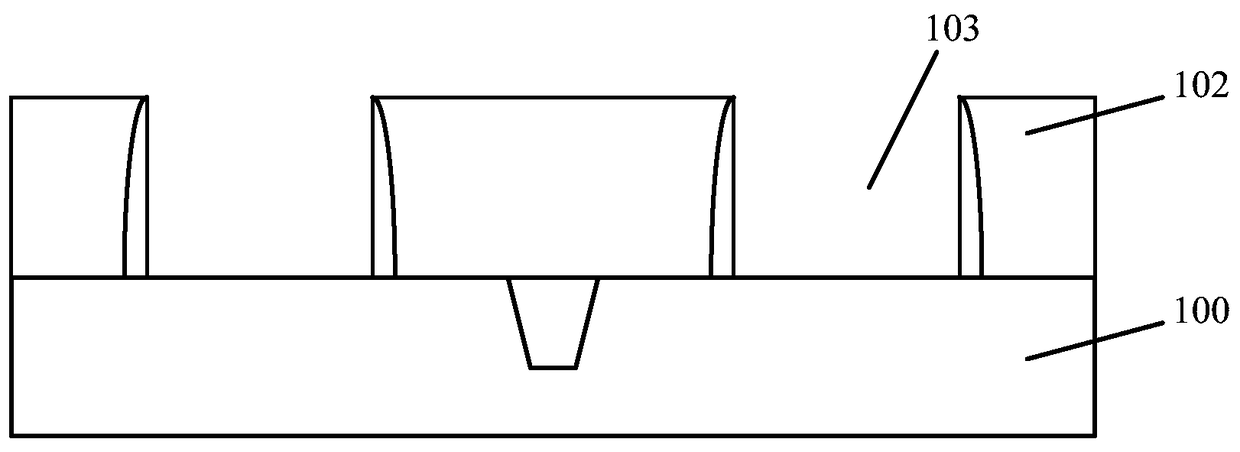

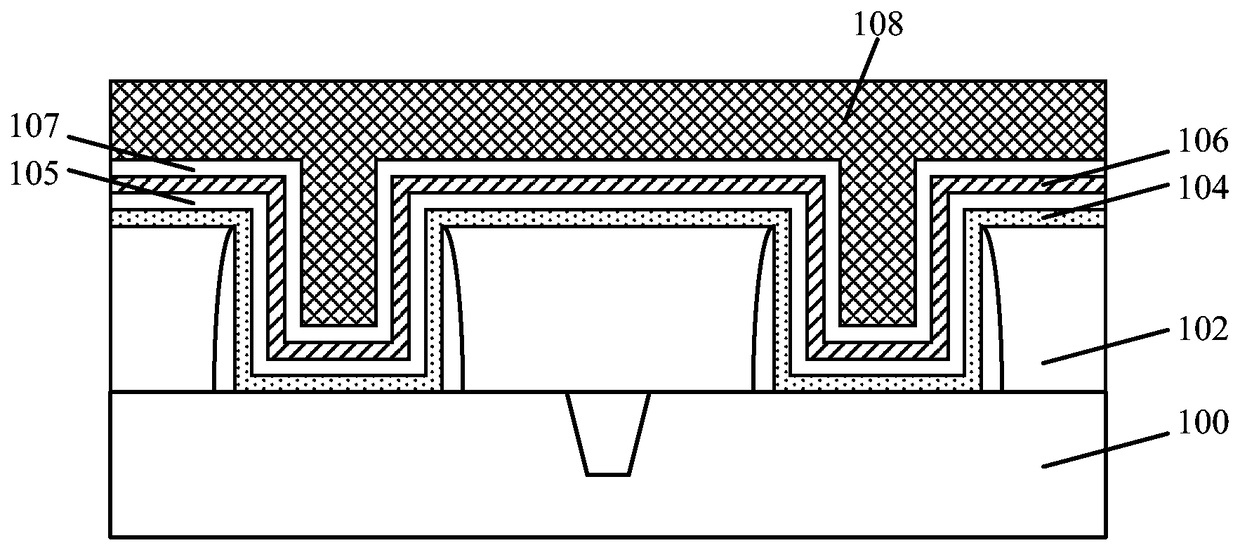

Method for manufacturing transistor

ActiveCN103915323AThreshold voltage uniformAvoid Irregular DamageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricOptoelectronics

The invention provides a method for manufacturing a transistor. The method comprises the steps of providing a substrate, wherein a false gate structure is formed on the substrate, the false gate structure comprises a gate dielectric layer, a protective layer located on the gate dielectric layer, an oxide layer located on the protective layer and a false gate located on the oxide layer, the gate dielectric layer is made of oxygen containing materials, and oxygen diffuses to the upper surface of the protective layer, so that an oxidation layer is formed; forming the source electrode and the drain electrode of the transistor after the false gate structure is formed; forming an interlayer dielectric layer on the substrate after the source electrode and the drain electrode are formed, wherein the upper surface of the false gate structure is exposed through the interlayer dielectric layer; eliminating the false gate, wherein a false gate trench is formed in the interlayer dielectric layer; eliminating the oxide layer and the oxidation layer after the false gate trench is formed; forming a gate electrode in the false gate trench after the oxide layer and the oxidation layer are eliminated. By the adoption of the method for manufacturing the transistor, the transistor can obtain an even threshold voltage, and therefore the performance of the transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

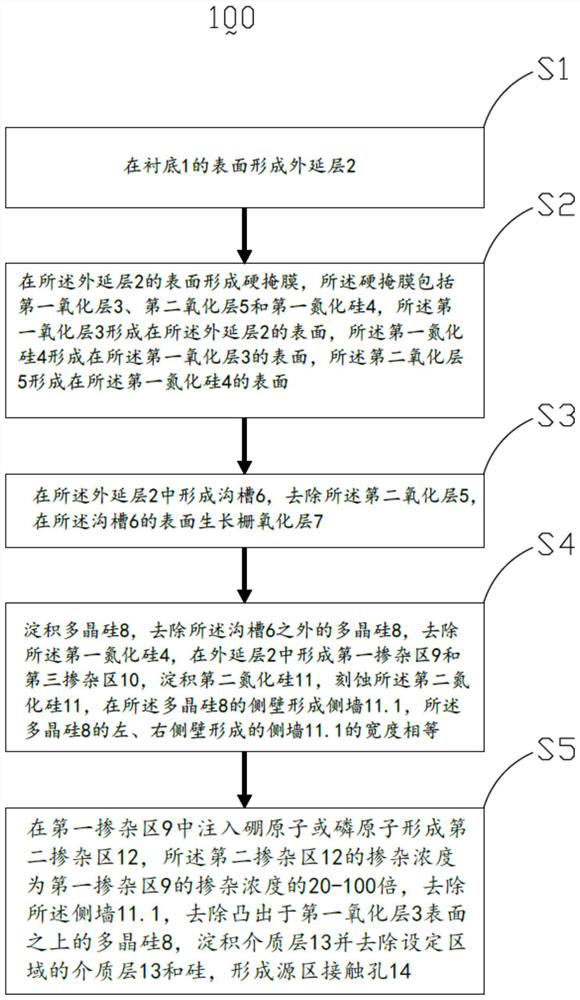

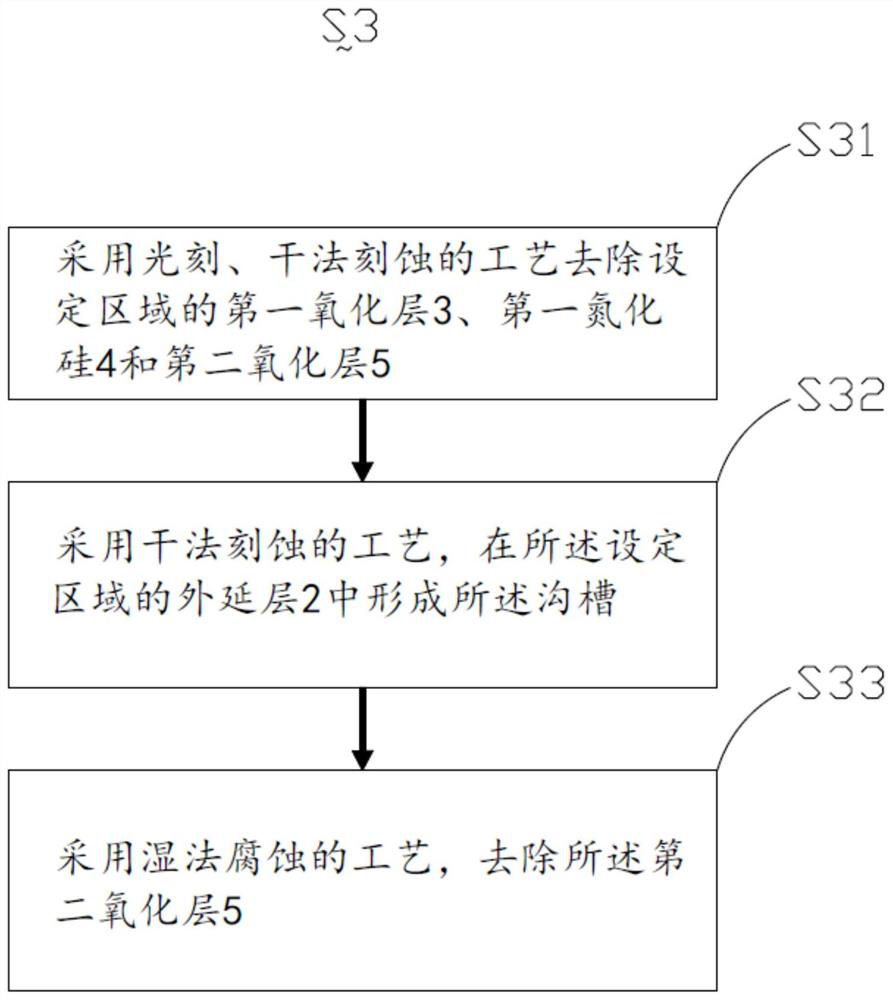

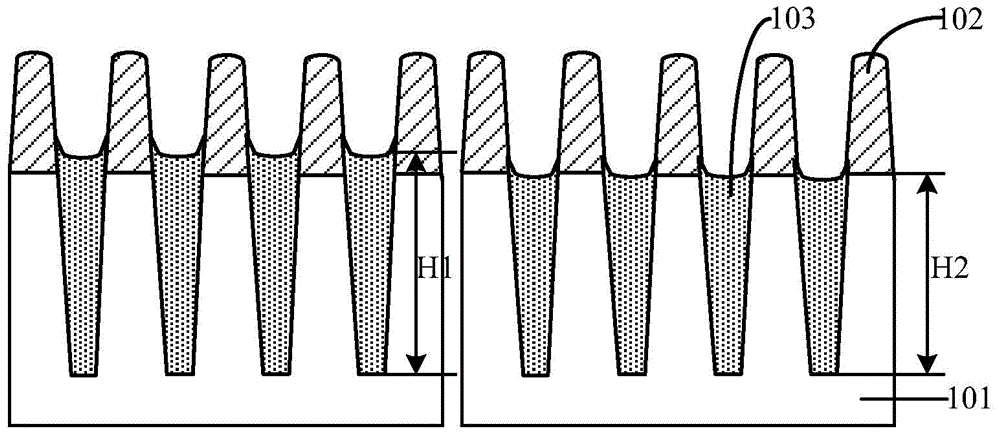

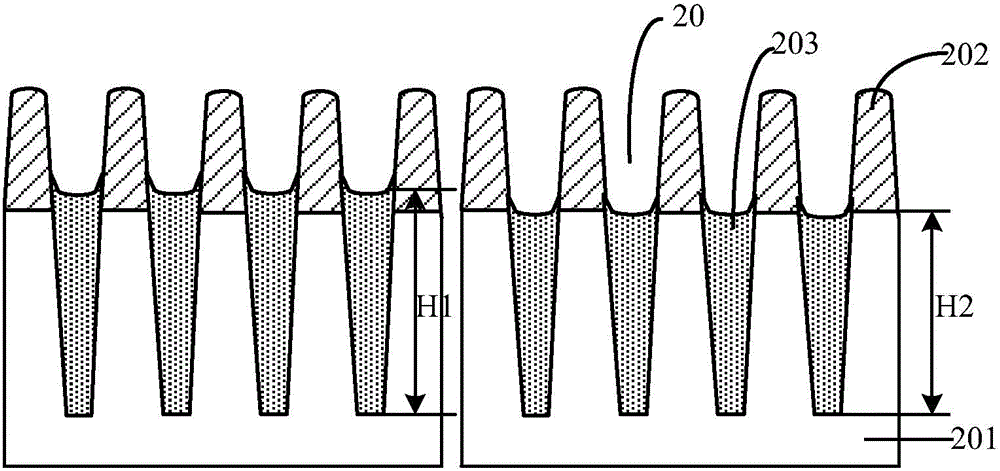

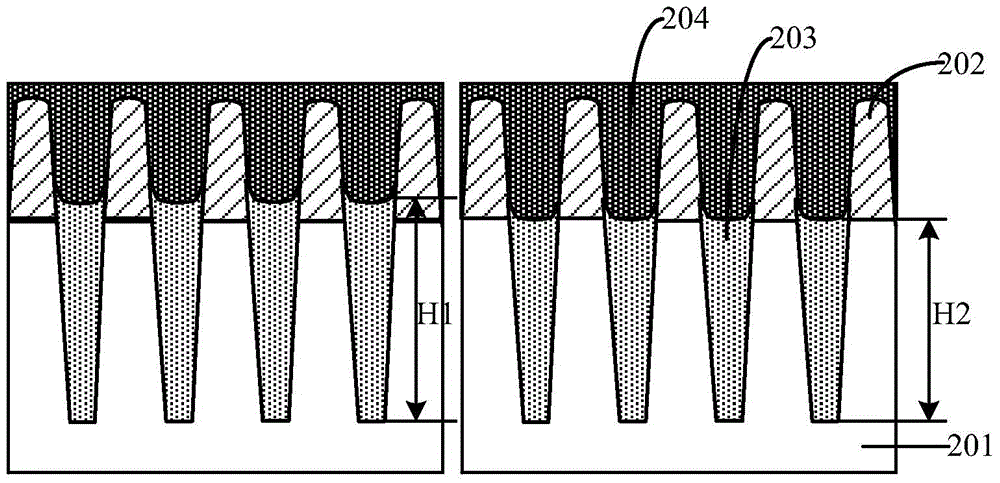

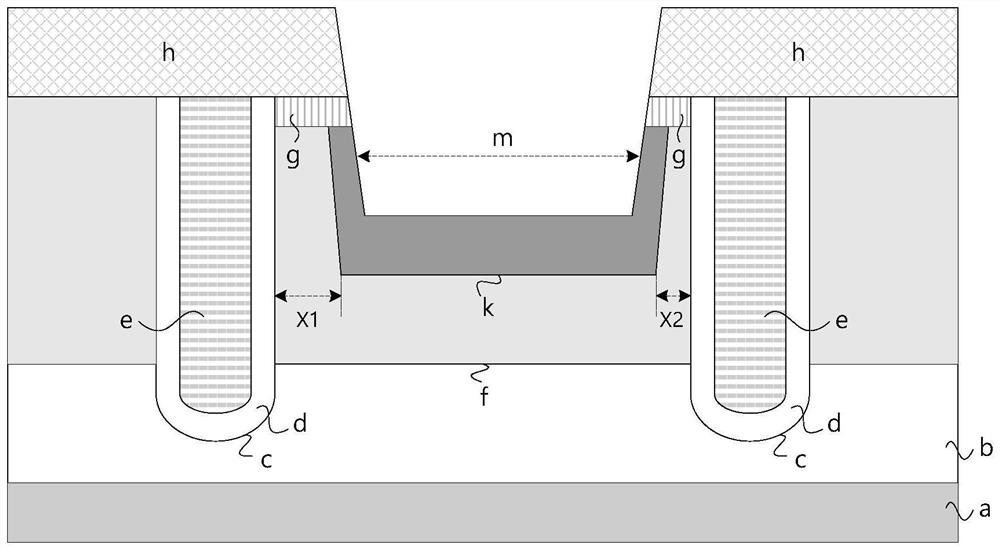

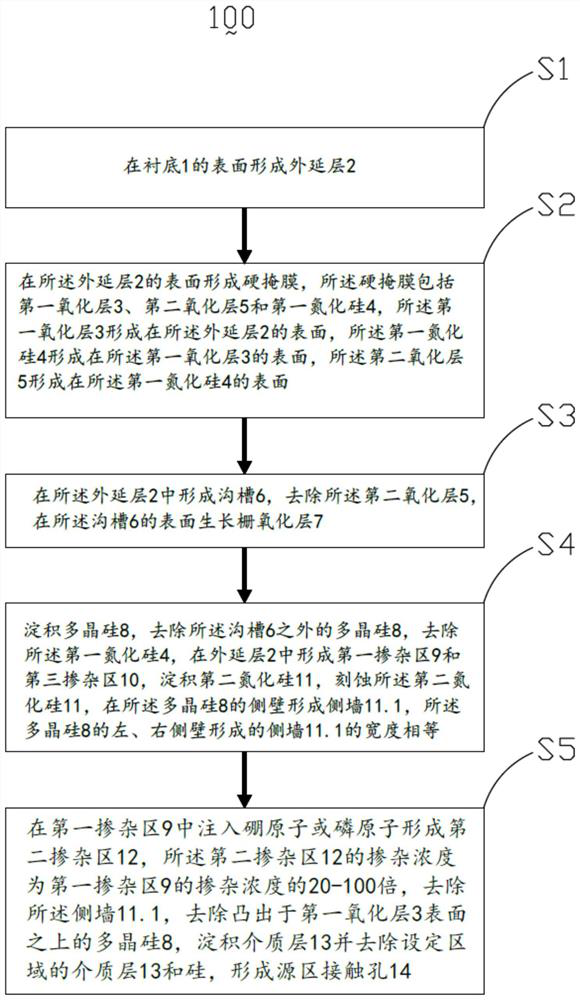

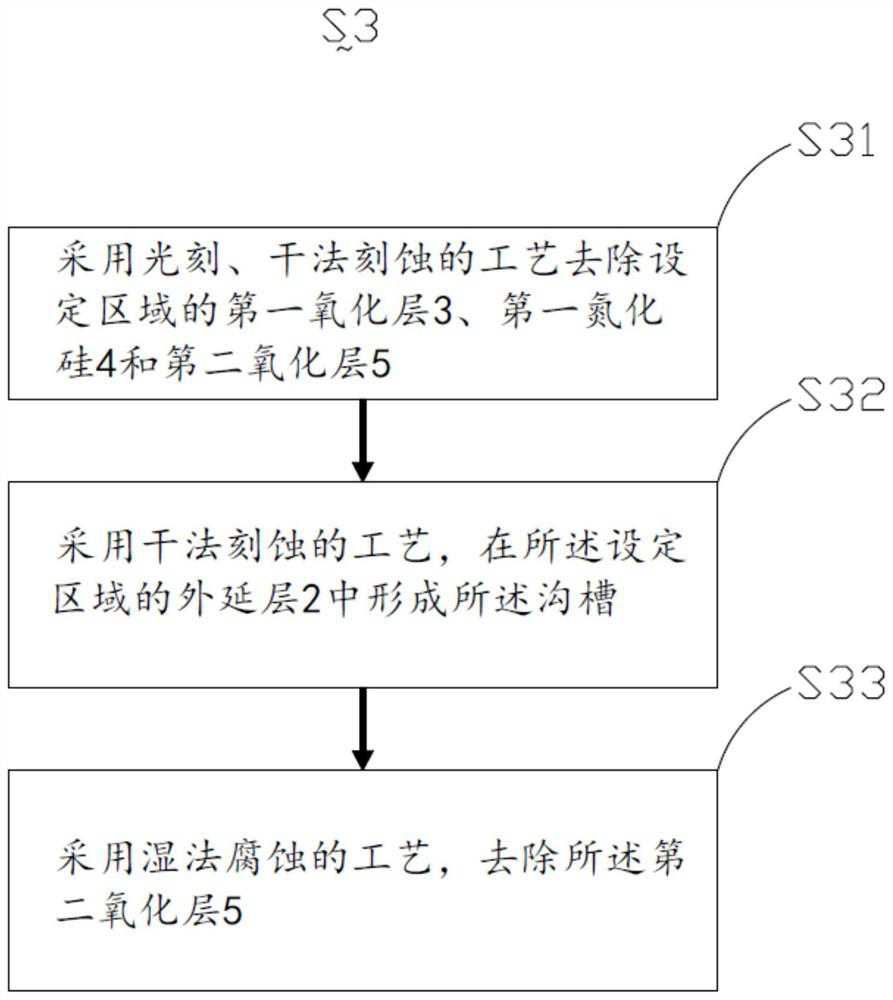

Process method for improving cell density of trench MOSFET and trench MOSFET structure

ActiveCN112103186ABest Avalanche Current CharacteristicsThreshold voltage uniformTransistorSemiconductor/solid-state device detailsTrench mosfetEngineering

The invention discloses a process method for improving the cell density of a trench MOSFET and a trench MOSFET structure. The method comprises the following steps: depositing polycrystalline silicon,removing the polycrystalline silicon outside a trench, removing first silicon nitride, forming a first doped region and a third doped region in an epitaxial layer, depositing second silicon nitride, etching the second silicon nitride, and forming side walls on the side walls of the polycrystalline silicon, wherein the widths of the side walls formed by the left side wall and the right side wall ofthe polycrystalline silicon are equal; injecting boron atoms or phosphorus atoms into the first doped region to form a second doped region, wherein the doping concentration of the second doped regionis 20-100 times that of the first doped region, removing the side walls, removing polycrystalline silicon protruding out of the surface of the first oxide layer, depositing a dielectric layer, removing the dielectric layer and silicon in a set region, and forming source region contact holes. The process method for improving the cell density of the trench MOSFET and the trench MOSFET structure provided by the invention have the advantages of being capable of realizing more uniform threshold voltage and conduction resistance and the like.

Owner:深圳市芯电元科技有限公司

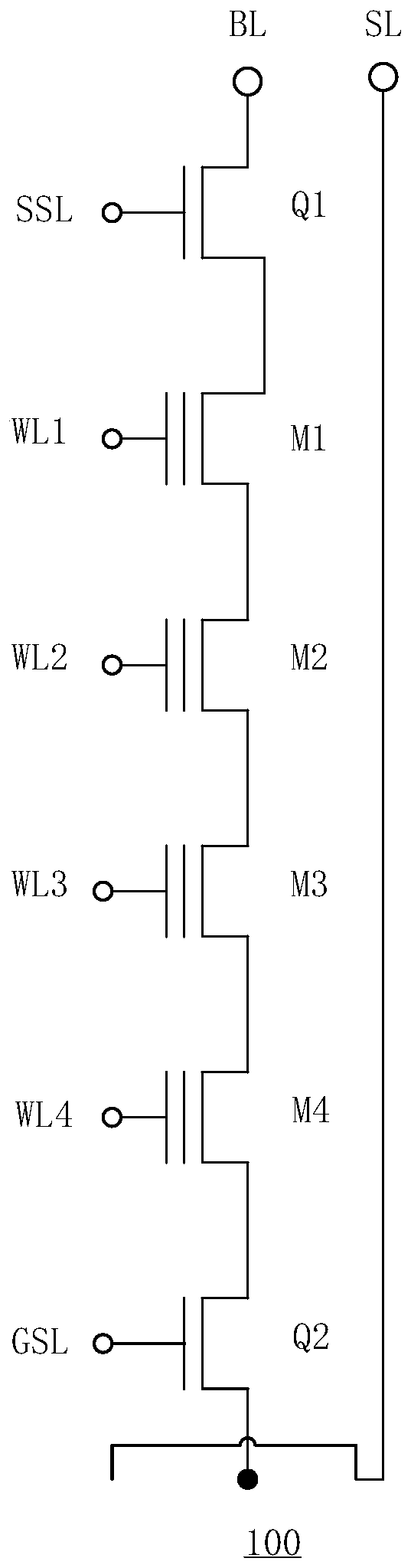

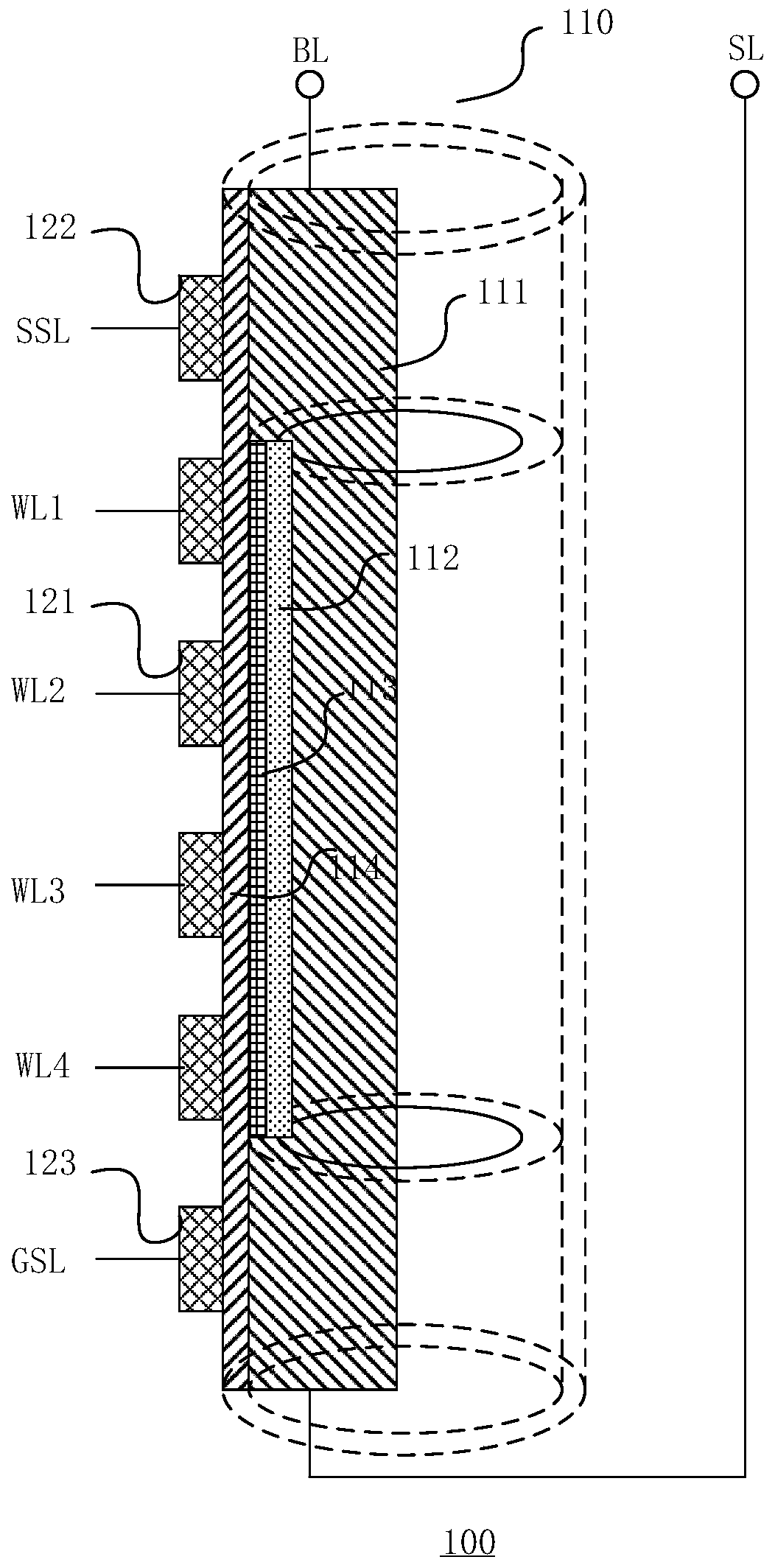

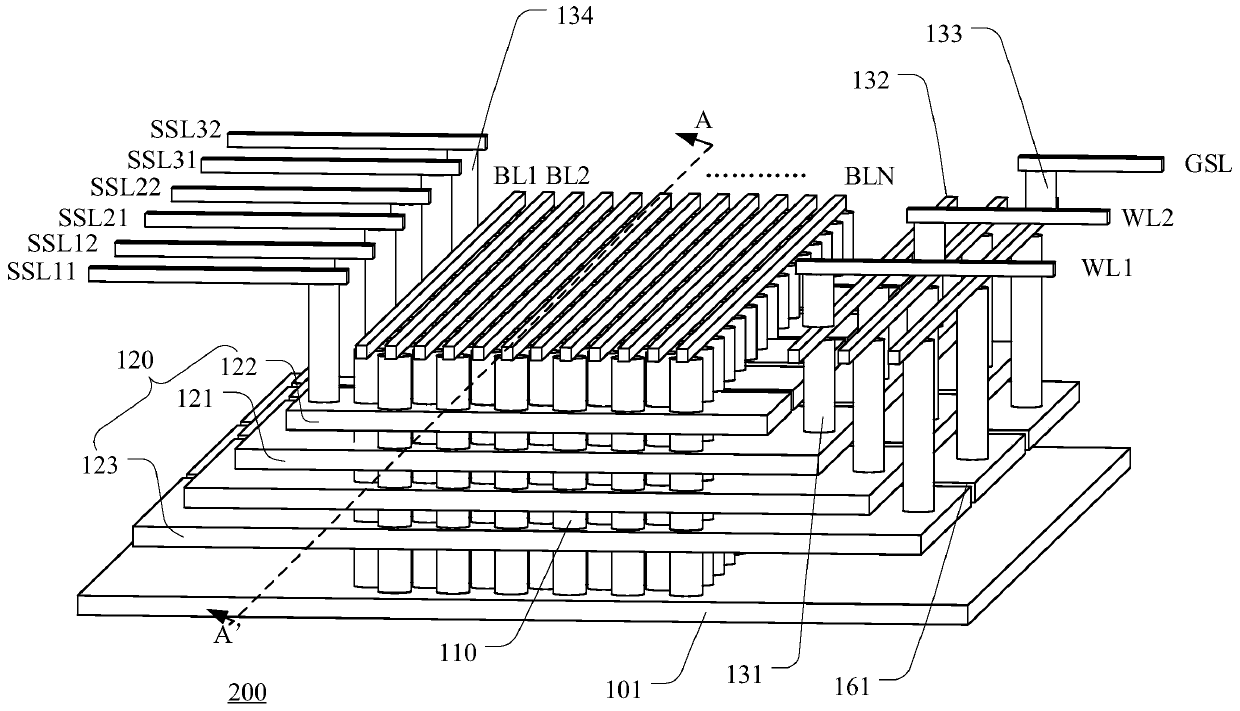

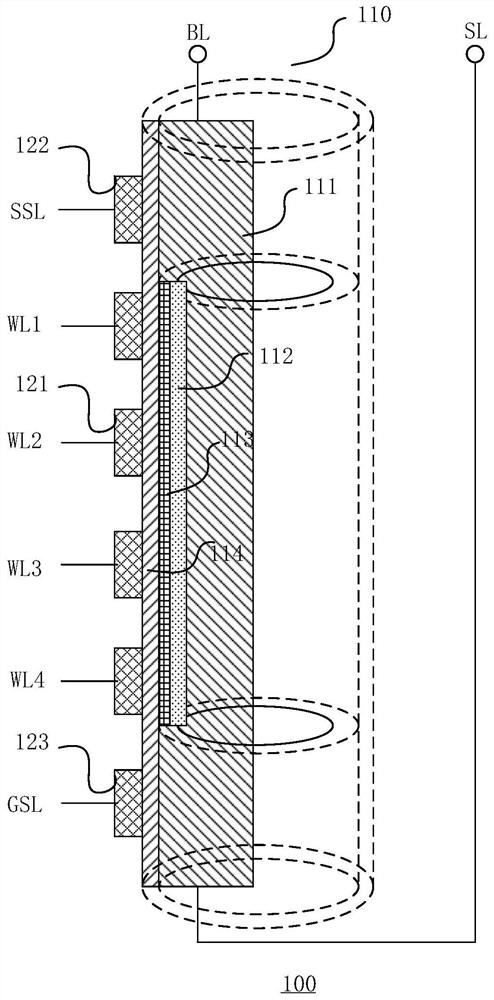

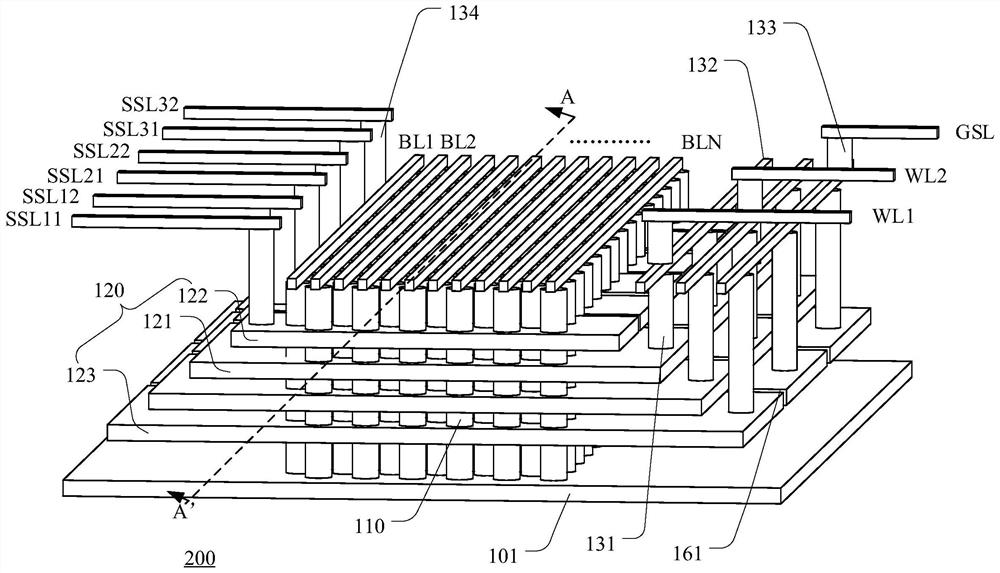

3D memory device and method for fabricating same

ActiveCN109712983AConsistent lossSame distanceSolid-state devicesSemiconductor devicesGate stackEngineering

Disclosed is a 3D memory device comprising a substrate; a stacked structure on the substrate and including a plurality of conductor layers and a plurality of insulating layers alternately stacked; a plurality of memory strings extending through the stacked structure; a plurality of conductive channels extending through the stacked structure; wherein the plurality of memory strings are configured as a honeycomb structure; each of the conductive channels is located at the center of the honeycomb structure and is configured to supply power to a plurality of memory strings around the substrate through the substrate. The present invention also provides a method for fabricating a 3D memory device provided by the present invention. The method, by using a common-source hole as a deposition channel to replace a sacrificial layer in the stacked structure with a conductor layer and using the common-source hole to form a common-source conductive channel, avoids voids between the conductor layersand the common-source conductive channel in the gate stacked structure.

Owner:YANGTZE MEMORY TECH CO LTD

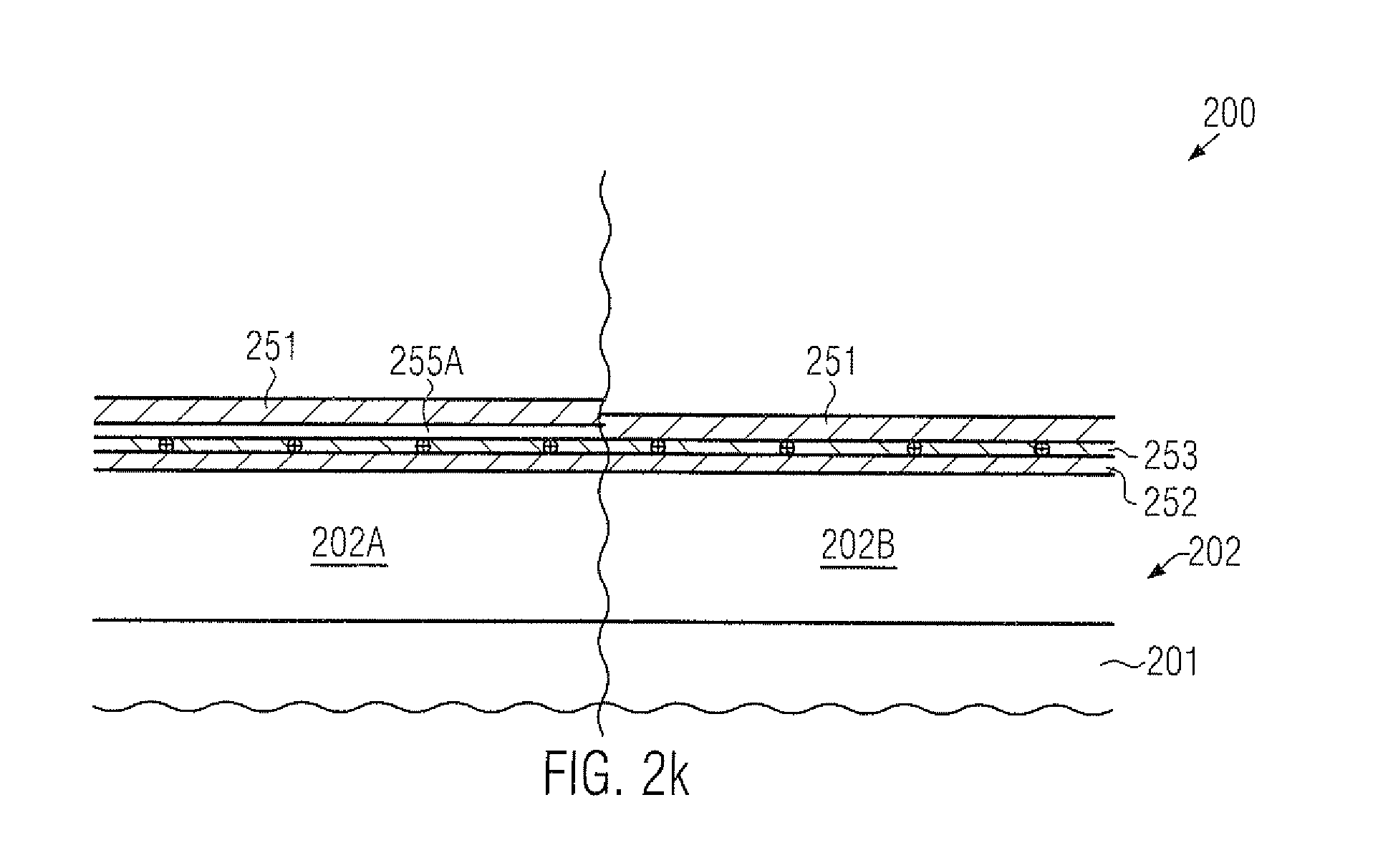

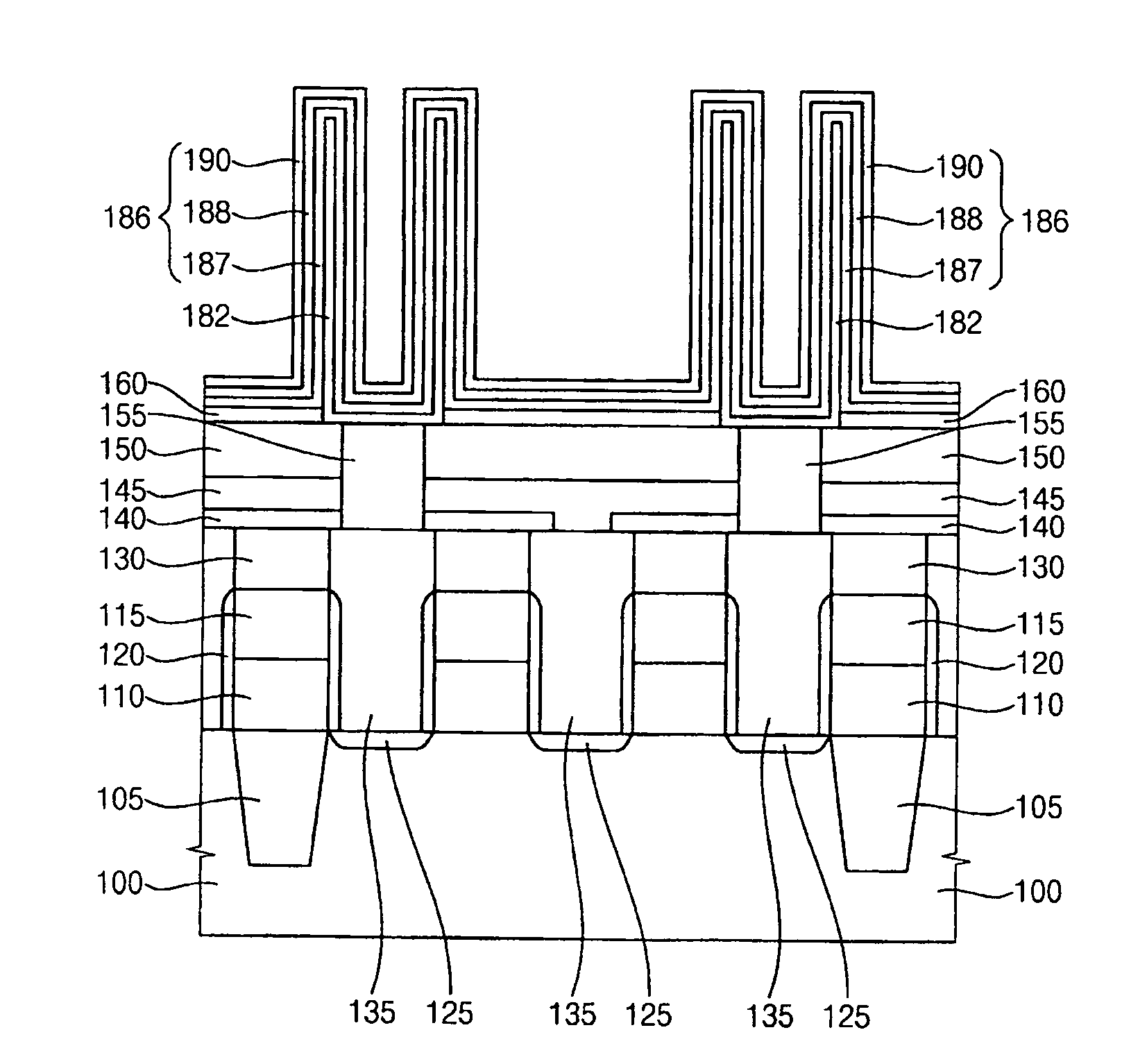

Methods of manufacturing semiconductor devices

ActiveUS20090246949A1Reduce leakageHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingEquivalent oxide thicknessDevice material

In a semiconductor device and a method of manufacturing a semiconductor device, a lower electrode is formed on a semiconductor substrate. A first zirconium oxide layer is formed on the lower electrode by performing a first deposition process using a first zirconium source and a first oxidizing gas. A zirconium carbo-oxynitride layer is formed on the first zirconium oxide layer by performing a second deposition process using a second zirconium source, a second oxidizing gas and a nitriding gas, and an upper electrode is formed on the zirconium carbo-oxynitride layer. A zirconium oxide-based composite layer having a high dielectric constant and a thin equivalent oxide thickness can be obtained.

Owner:SAMSUNG ELECTRONICS CO LTD

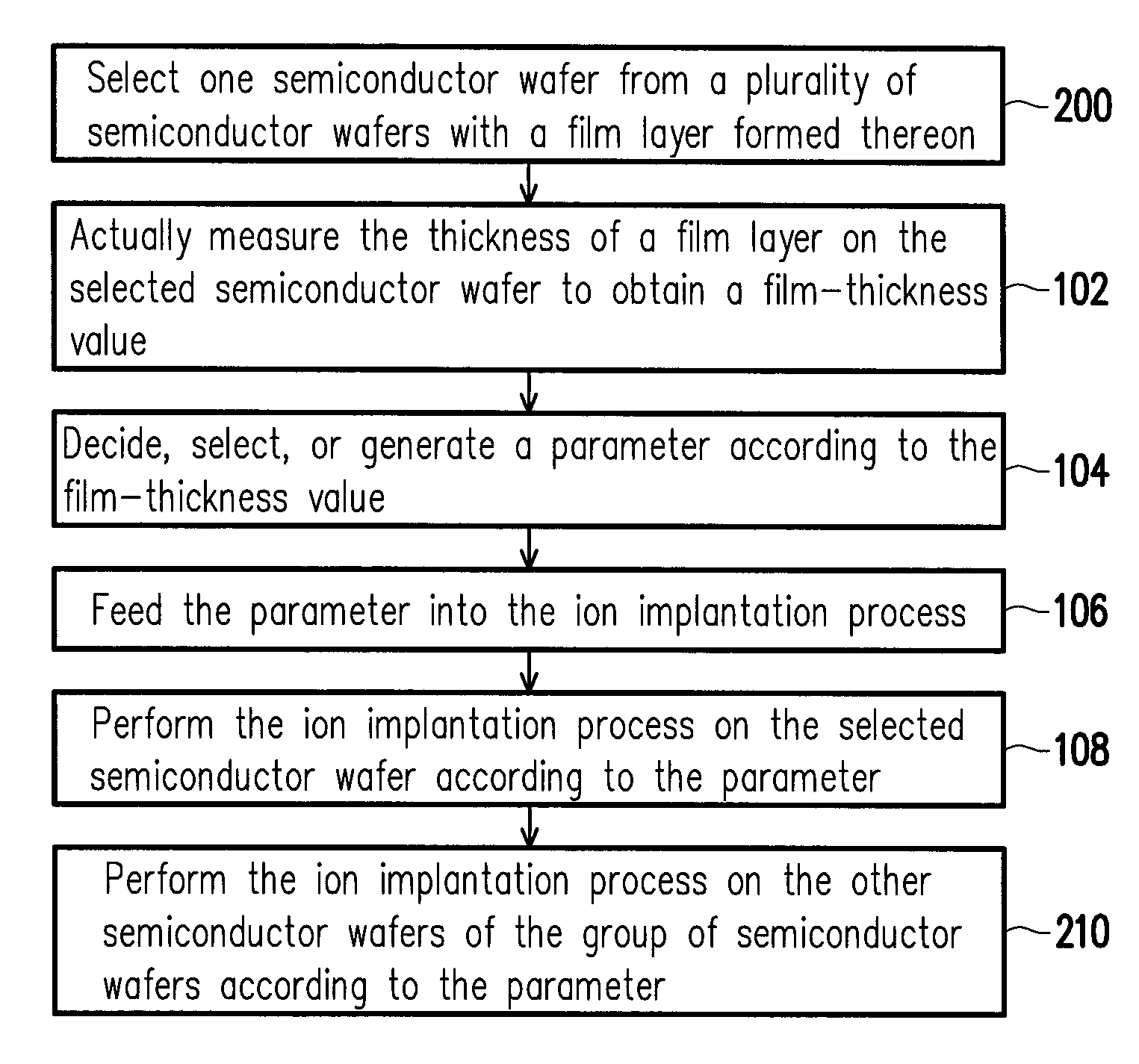

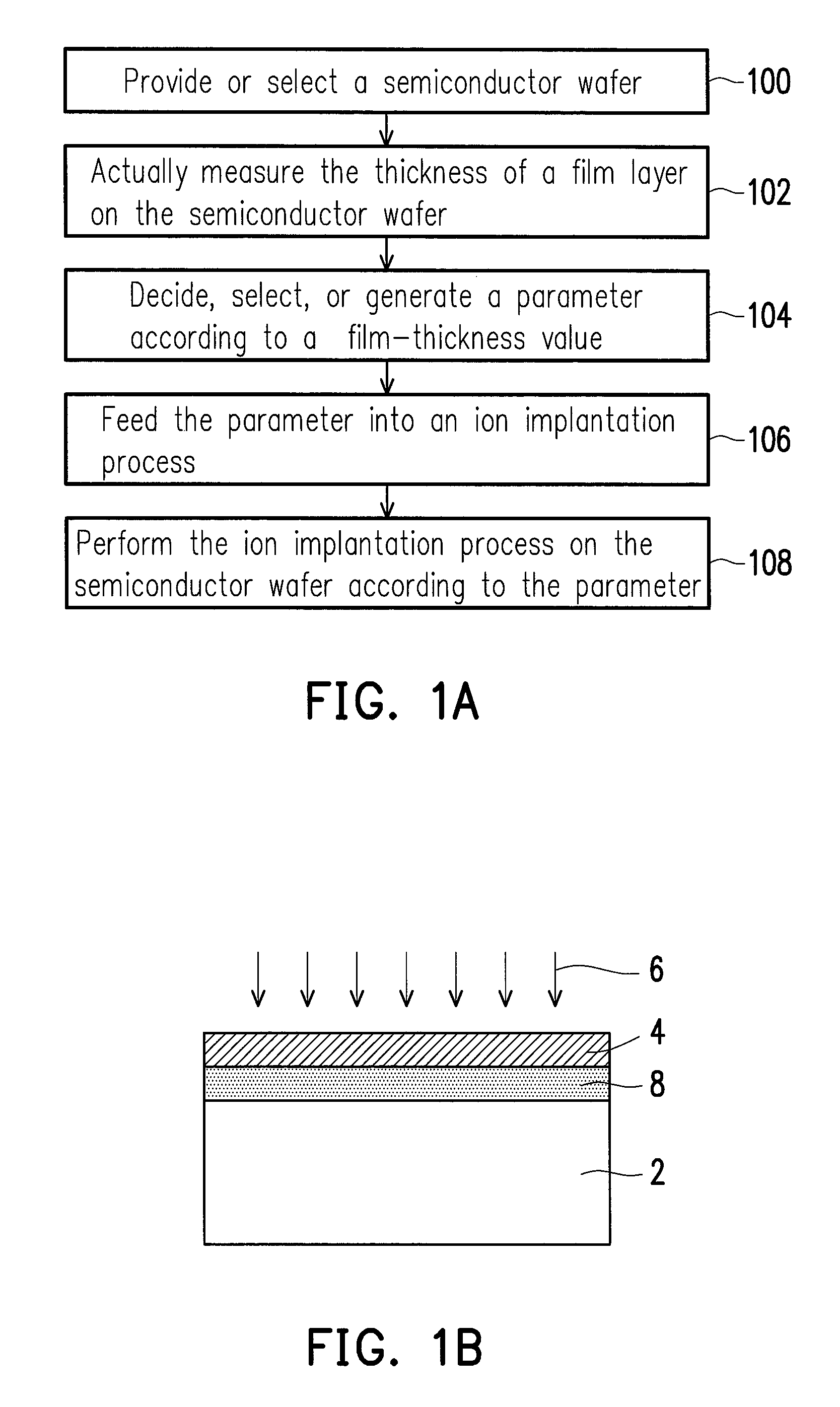

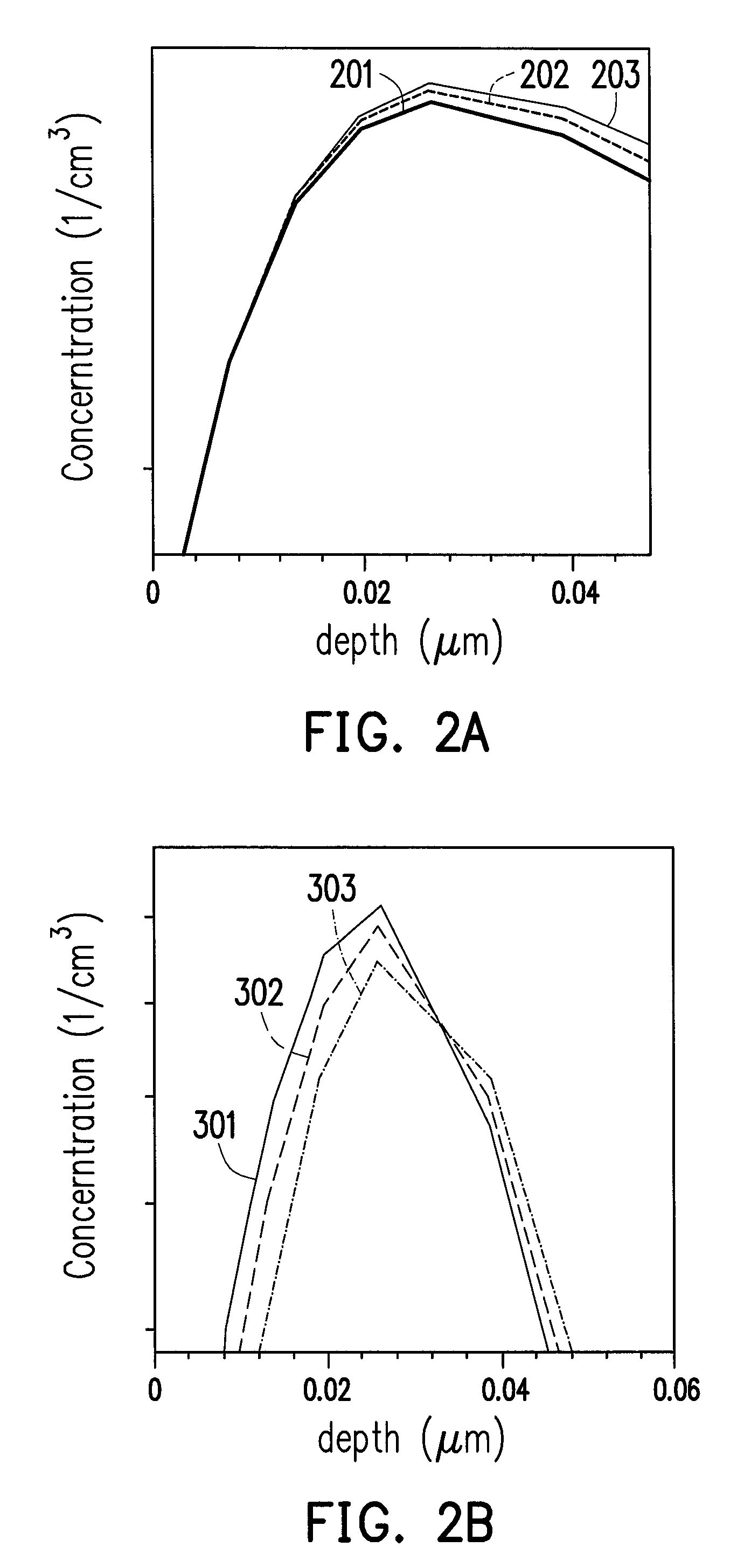

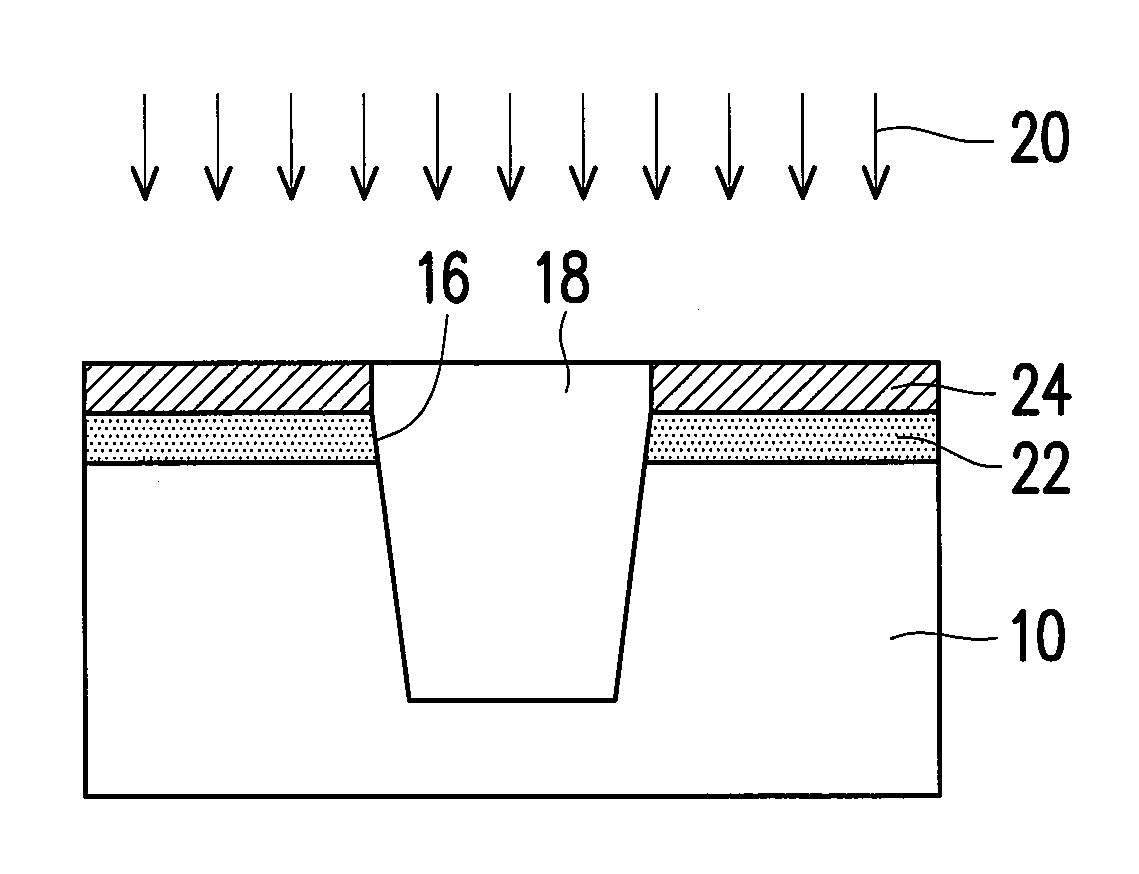

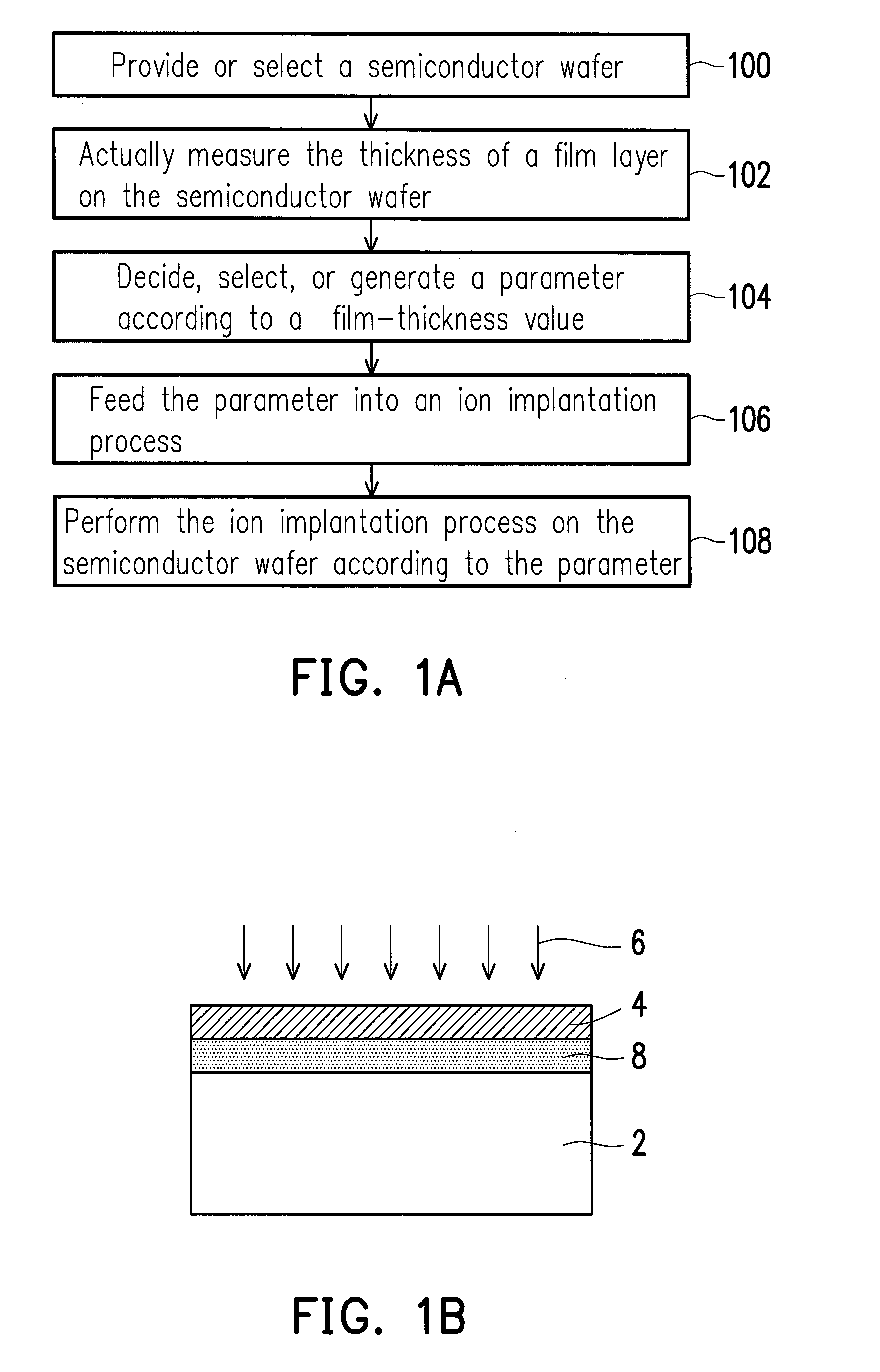

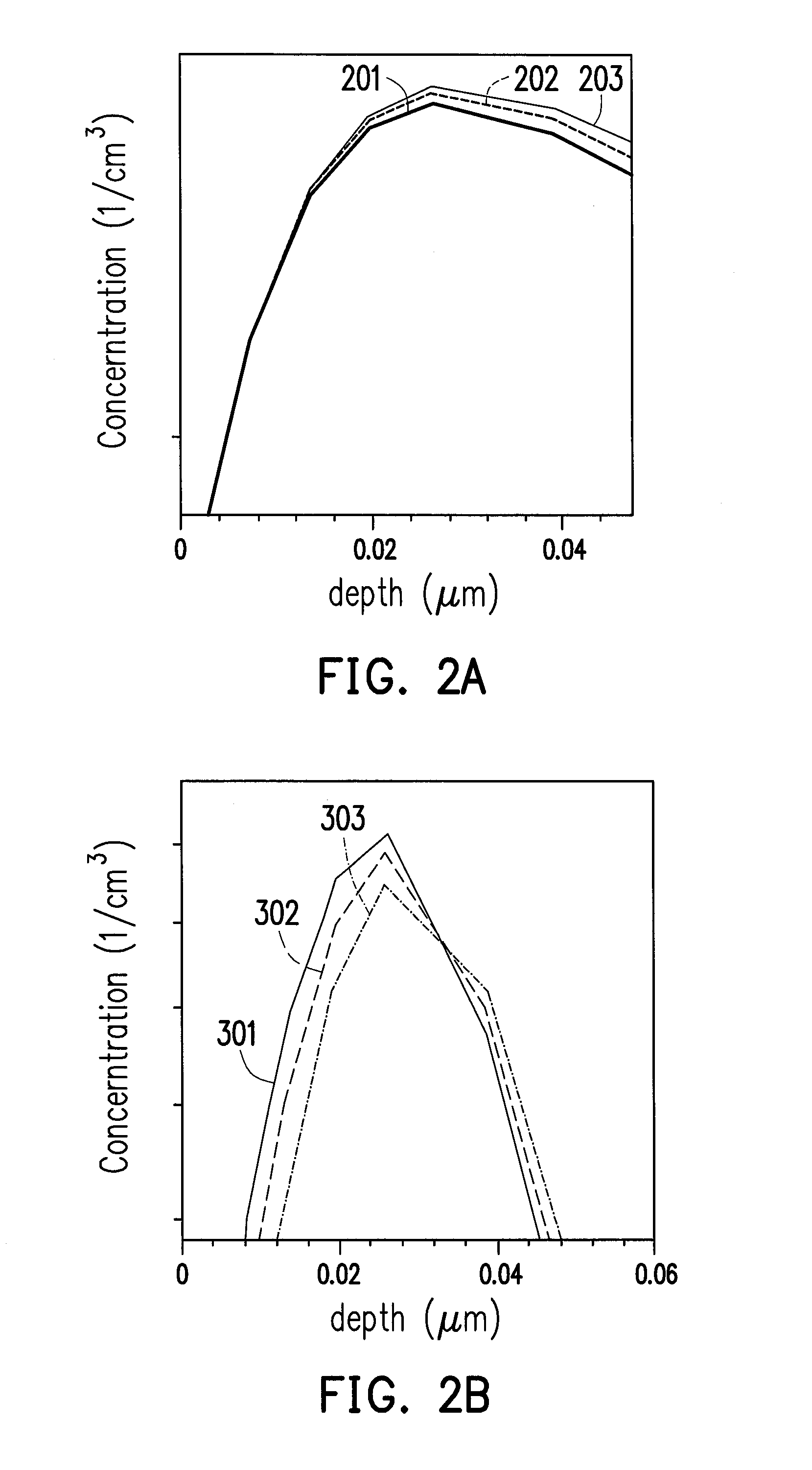

Method of controlling threshold voltage and method of fabricating semiconductor device

ActiveUS9082660B2Easy to controlThreshold voltage uniformSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

A method of controlling a threshold voltage is provided. The method of controlling a threshold voltage includes performing a film-thickness measuring step to measure the thickness of a film layer on a wafer to obtain a film-thickness value. Then, at least one parameter is decided, selected, or generated according to the film-thickness value. Next, an ion implantation process is performed on the wafer, wherein the ion implantation process is executed according to the parameter to form a threshold voltage adjustment region in the wafer below the film layer.

Owner:UNITED MICROELECTRONICS CORP

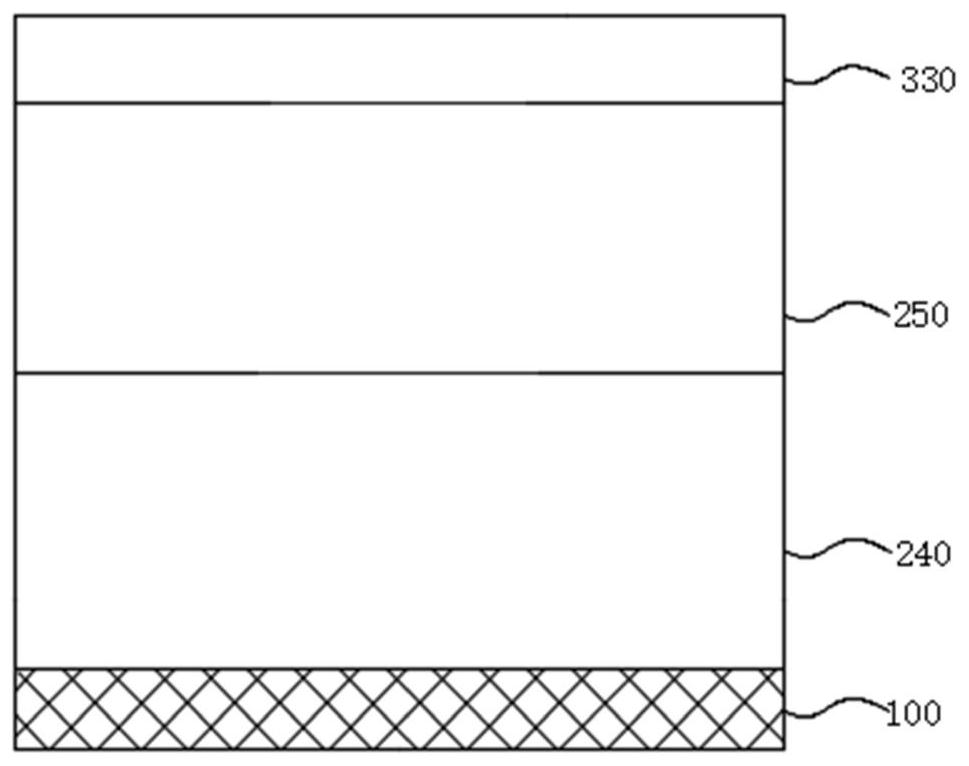

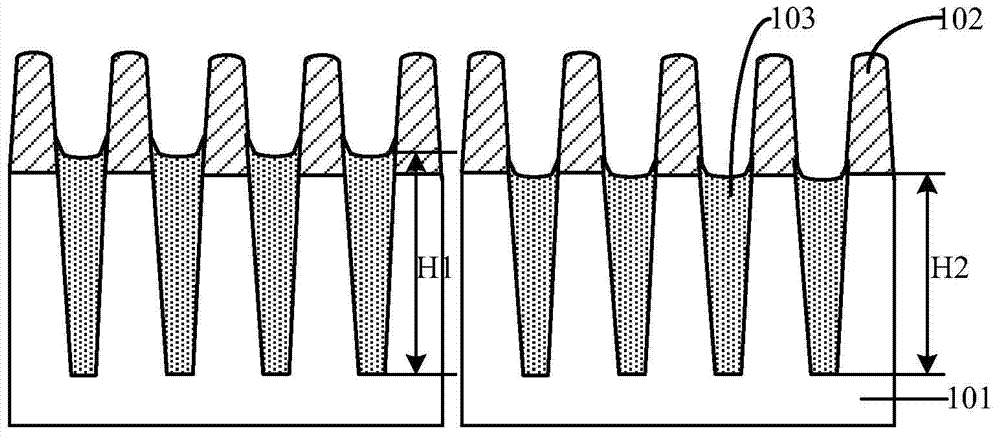

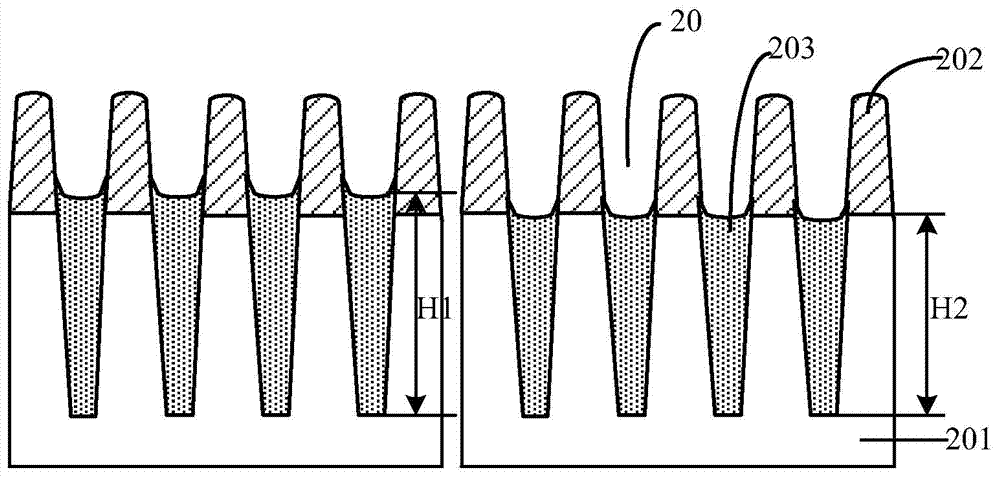

Semiconductor device, preparation method thereof, and electronic device

ActiveCN105097705AThreshold voltage uniformImprove performanceSemiconductor/solid-state device manufacturingPower semiconductor deviceEtching

The invention relates to a semiconductor device, a preparation method thereof, and an electronic device. The preparation method comprises: providing a semiconductor substrate including a central region and an edge region, wherein a plurality of floating gate structures are formed in the semiconductor substrate and shallow trench isolation structures are formed between the adjacent floating gate structures and downwardly extend to the semiconductor substrate; removing a part of oxide in the shallow trench isolation structures by using etching back in order to form a groove and expose a part of the sidewalls of the floating gate structures; depositing a covering layer in order to fill the groove and cover the floating gate structures; and removing a part of the covering layer by using wet etching in order to expose a part of the sidewalls of the floating gate structures again. The method further deposits the covering layer after a COPEN processing step, then removes the covering layer by using wet etching, and leaves a part of the covering layer at the edge region in order to compensate the thickness of the oxide in the edge area, thereby improving device performance and yield.

Owner:SEMICON MFG INT (SHANGHAI) CORP

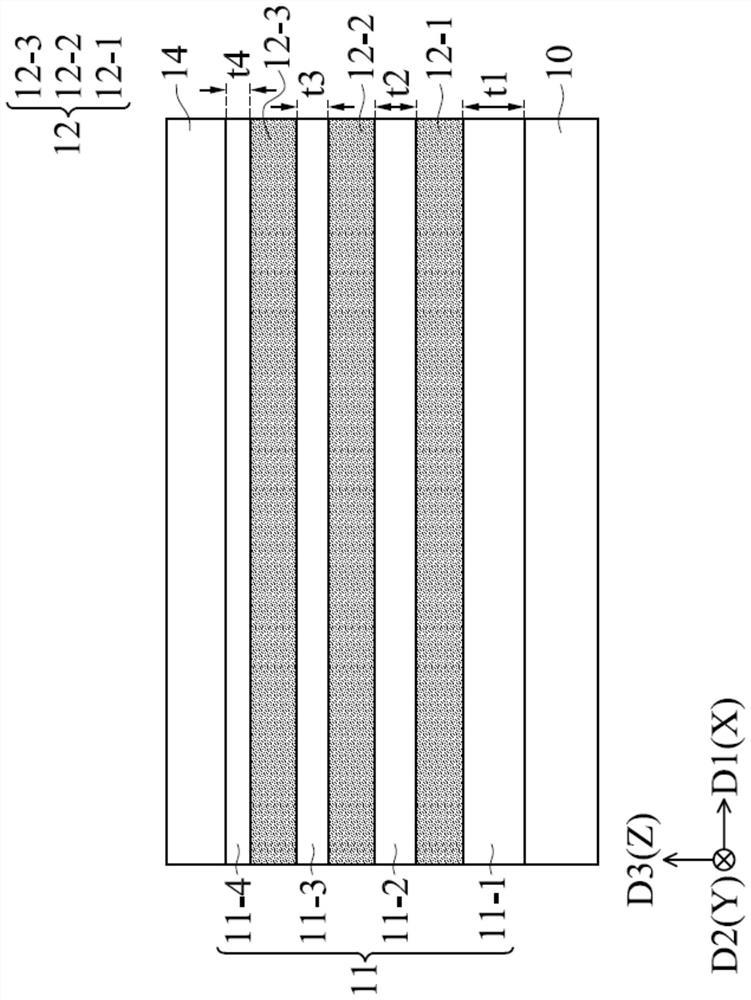

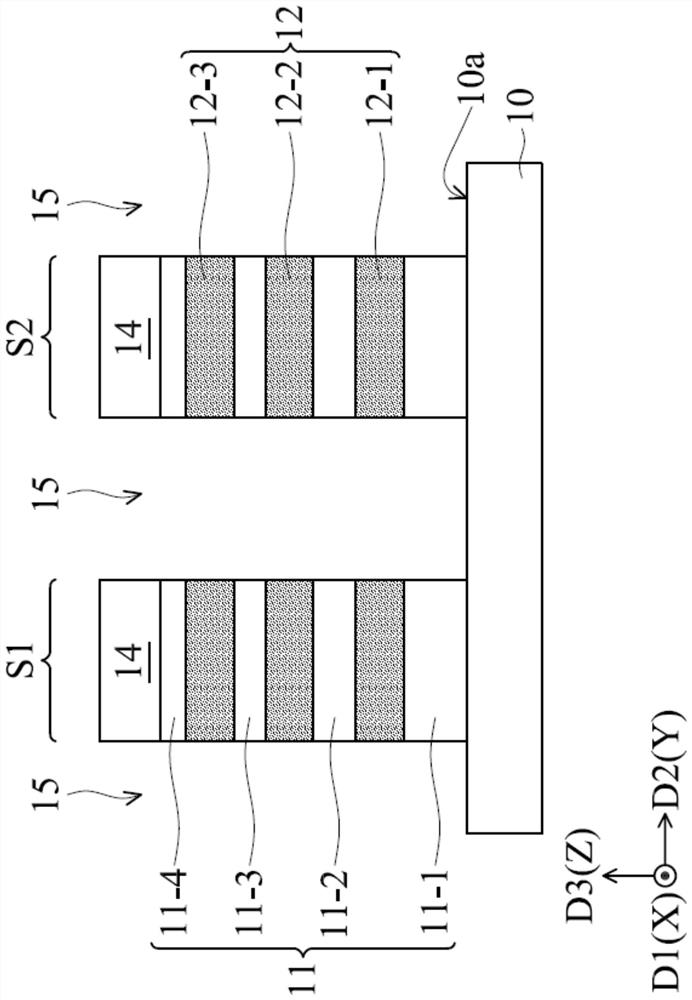

Semiconductor structure

PendingCN112750907AMinimize the difference in electrical propertiesThreshold voltage uniformNanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

The invention discloses a semiconductor structure. The semiconductor structure includes several semiconductor stacks over a substrate, and each of the semiconductor stacks extends in a first direction, wherein adjacent semiconductor stacks are spaced apart from each other in a second direction, which is different from the first direction. Each of the semiconductor stacks includes channel layers above the substrate and a gate structure across the channel layers. The channel layers are spaced apart from each other in the third direction which is perpendicular to the first direction and the second direction. The gate structure includes gate dielectric layers around the respective channel layers, and a gate electrode along sidewalls of the gate dielectric layers and a top surface of the uppermost gate dielectric layer. The space in the third direction between the two lowermost channel layers of the channel layers is greater than the space in the third direction between the two uppermost channel layers of the channel layers in the same semiconductor stack. This makes it possible to obtain a more uniform threshold voltage of a nanosheet transistor comprising channel layers in each semiconductor stack.

Owner:MEDIATEK INC

Methods of manufacturing semiconductor devices

ActiveUS7977257B2Reduce leakageHigh dielectric constantTransistorSolid-state devicesEquivalent oxide thicknessNitrogen oxide

In a semiconductor device and a method of manufacturing a semiconductor device, a lower electrode is formed on a semiconductor substrate. A first zirconium oxide layer is formed on the lower electrode by performing a first deposition process using a first zirconium source and a first oxidizing gas. A zirconium carbo-oxynitride layer is formed on the first zirconium oxide layer by performing a second deposition process using a second zirconium source, a second oxidizing gas and a nitriding gas, and an upper electrode is formed on the zirconium carbo-oxynitride layer. A zirconium oxide-based composite layer having a high dielectric constant and a thin equivalent oxide thickness can be obtained.

Owner:SAMSUNG ELECTRONICS CO LTD

Field effect transistor device

ActiveUS9093510B2Improve reliabilityThreshold voltage uniformSemiconductor devicesField-effect transistorElectron

A field effect transistor device is provided by the invention. The field effect transistor device includes: a substrate; a buffer layer, a channel layer, and a first barrier layer sequentially disposed on the substrate; a two-dimensional electron gas controlling layer disposed on the first barrier layer; a second barrier layer disposed on the two-dimensional electron gas controlling layer, wherein the second barrier layer has a recess passing through the second barrier layer; and a gate electrode filled into the recess and separated from the second barrier layer and the two-dimensional electron gas controlling layer by an insulating layer.

Owner:NAT CENT UNIV +2

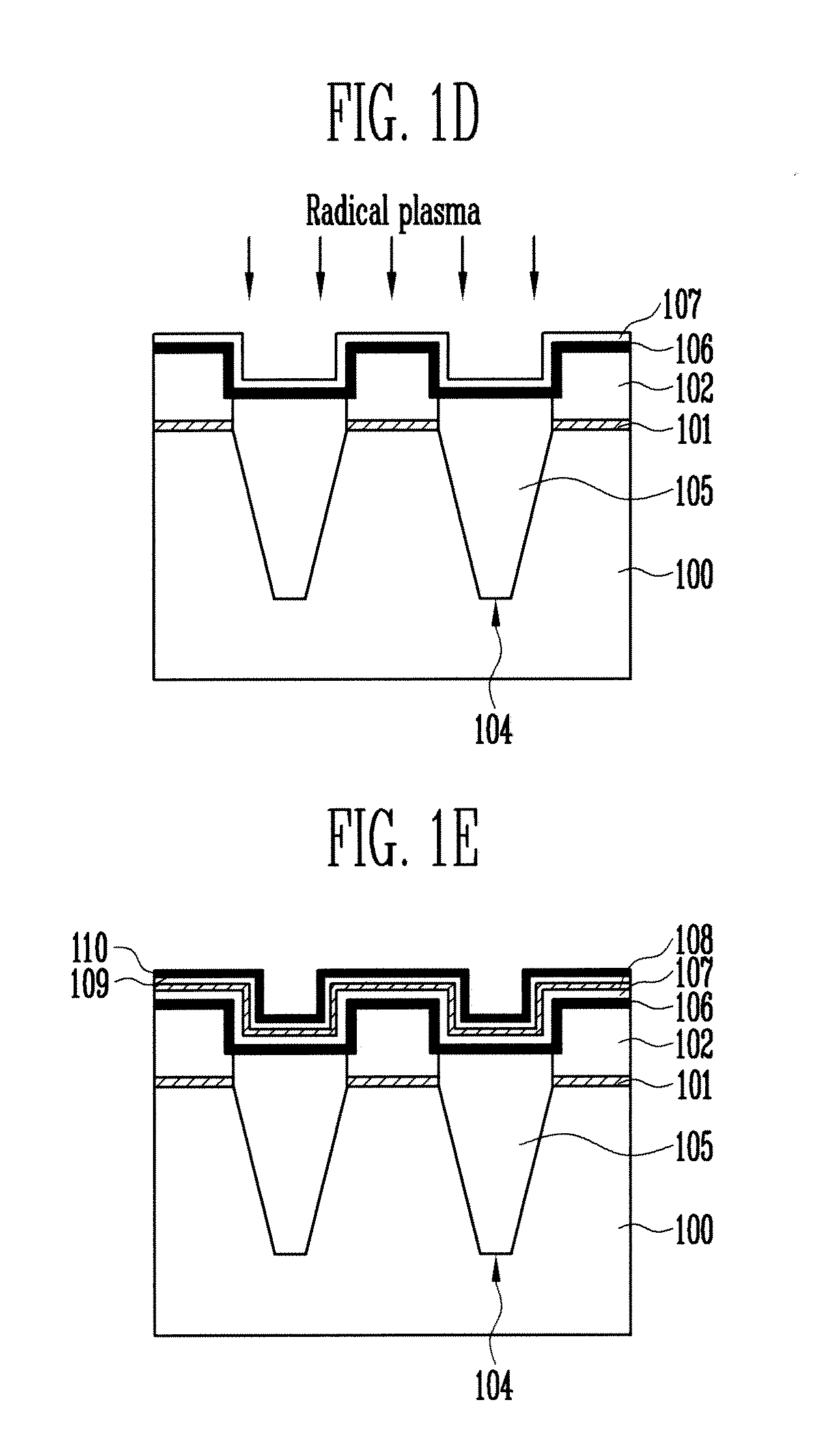

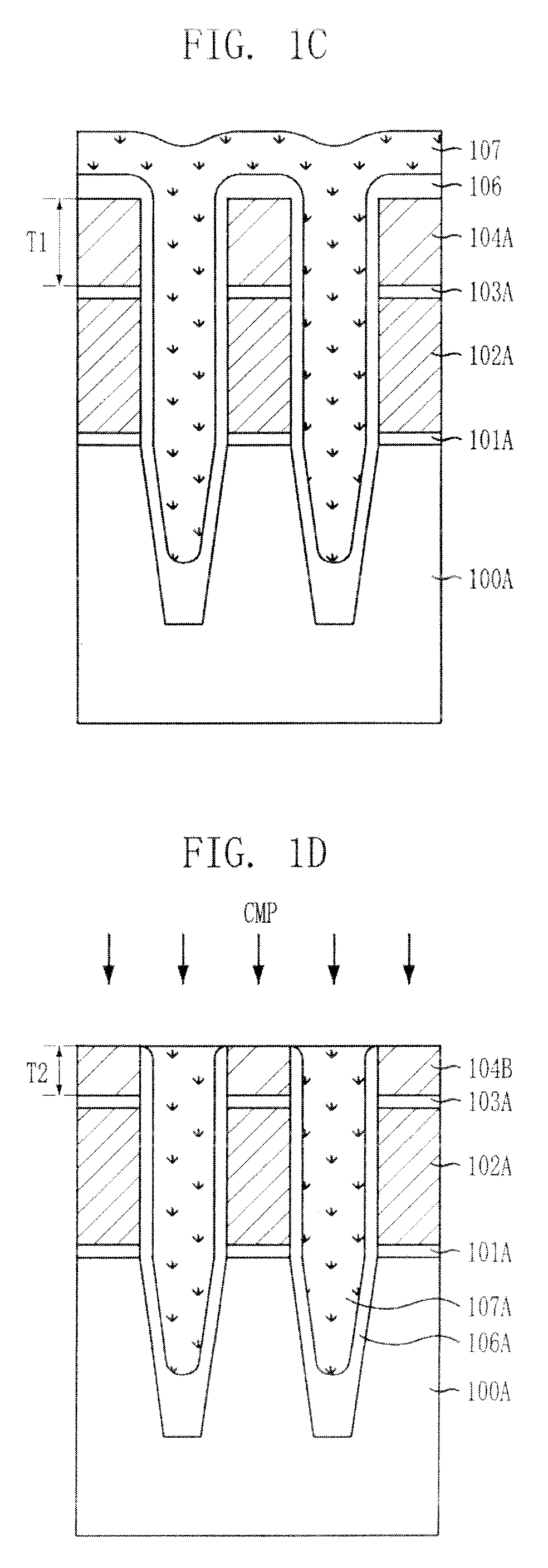

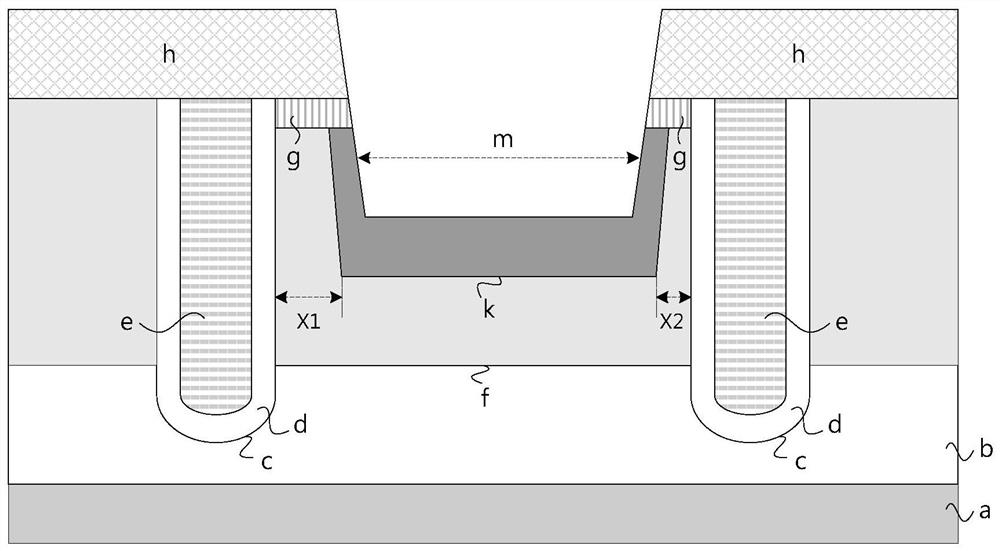

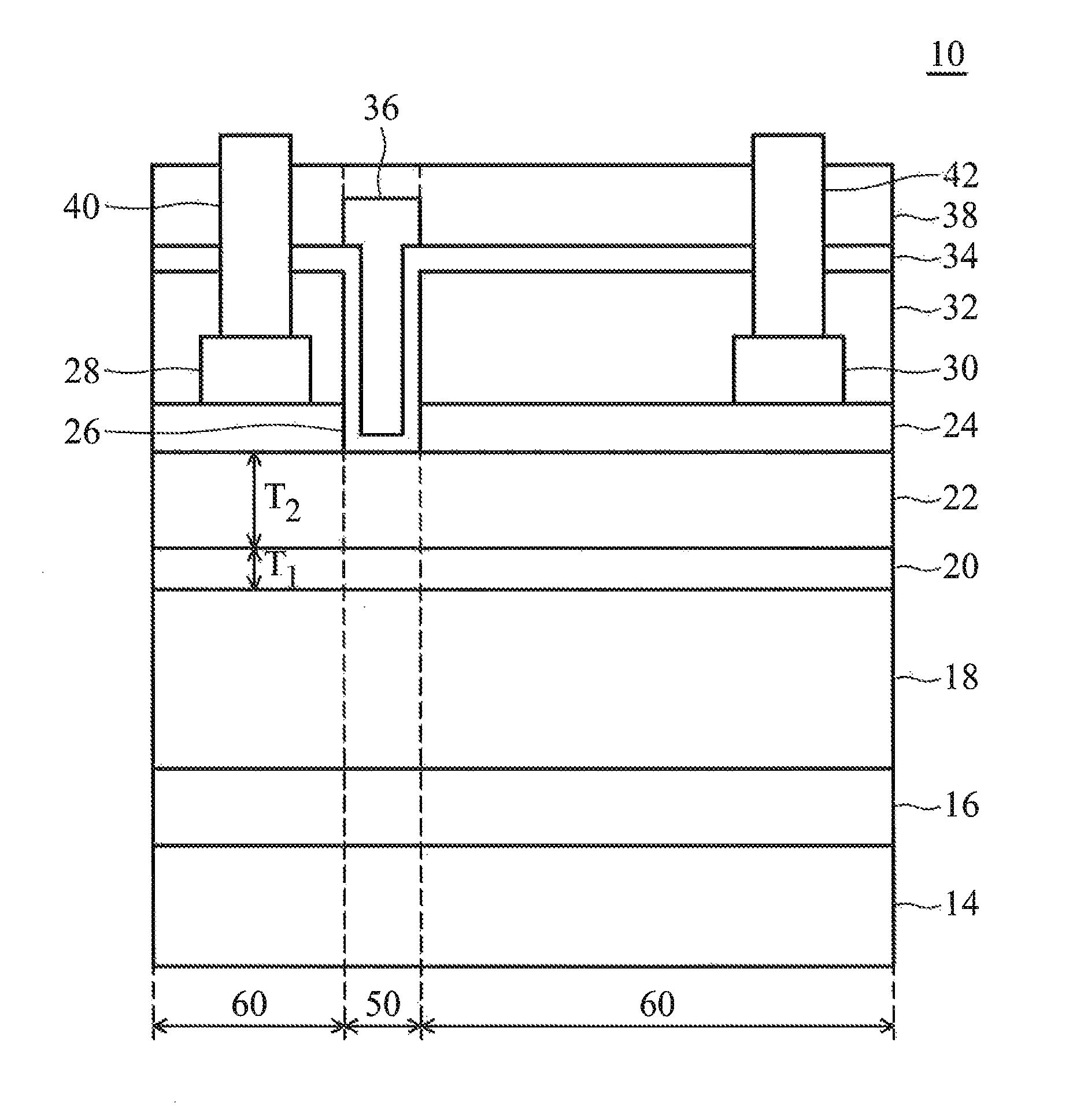

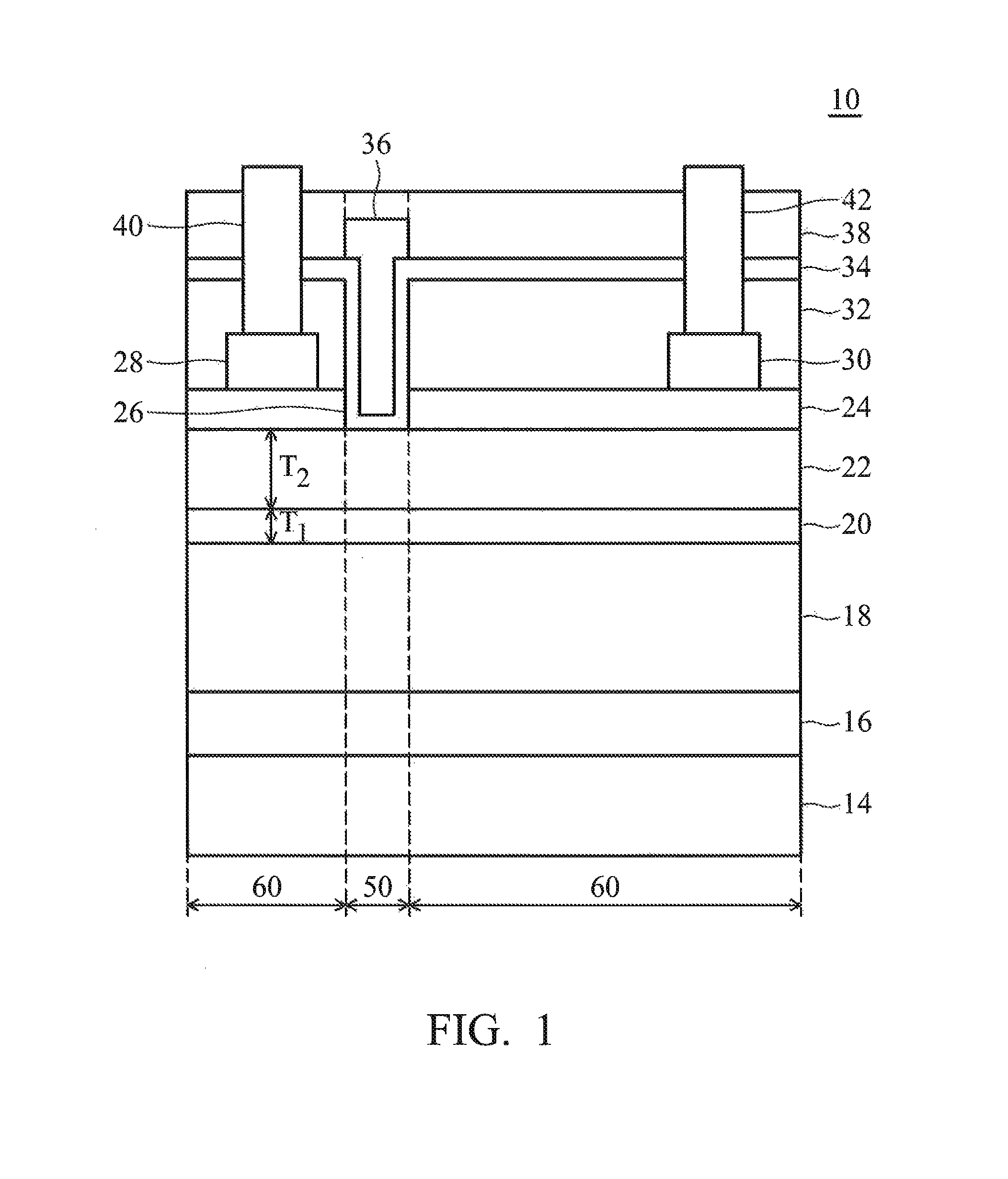

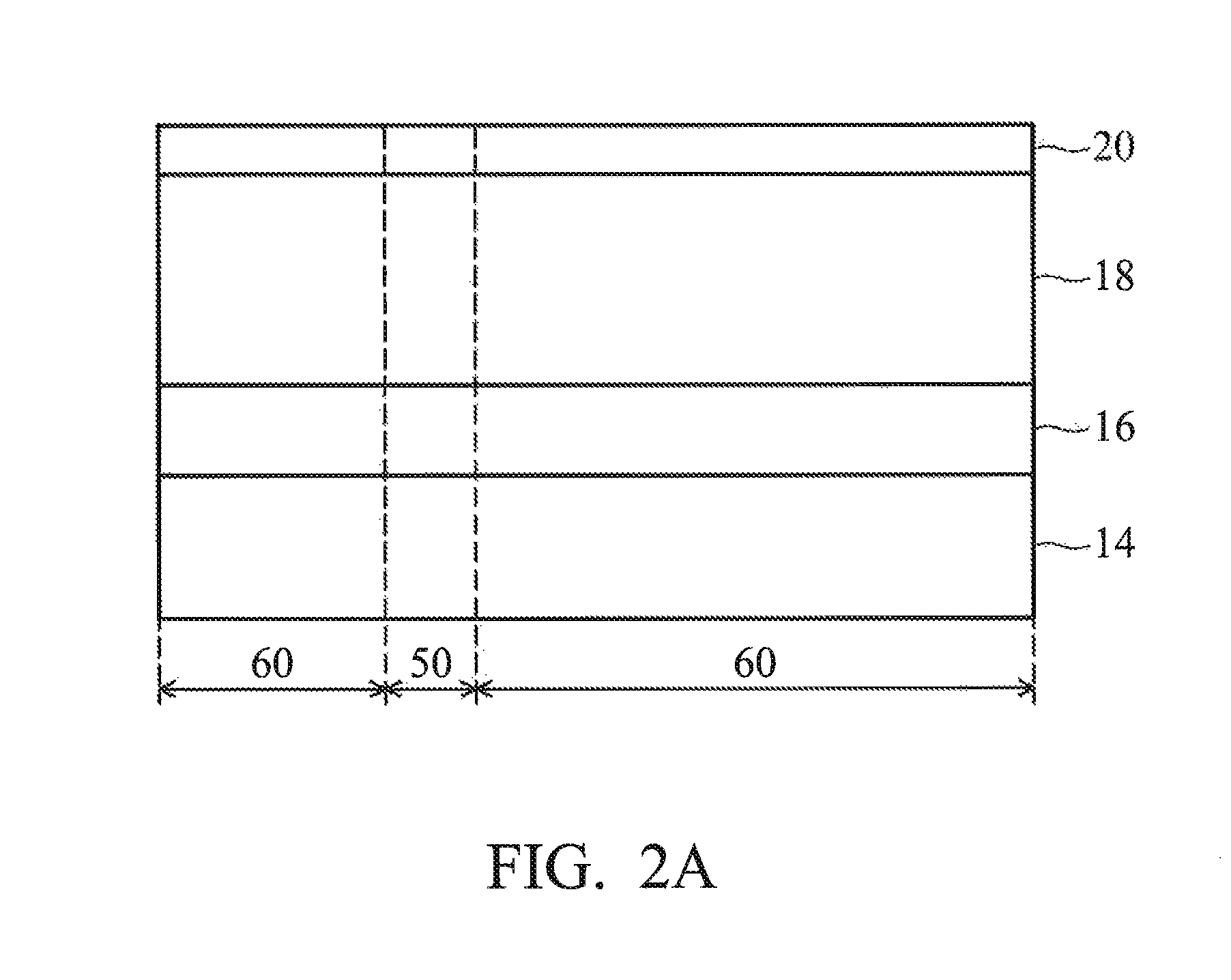

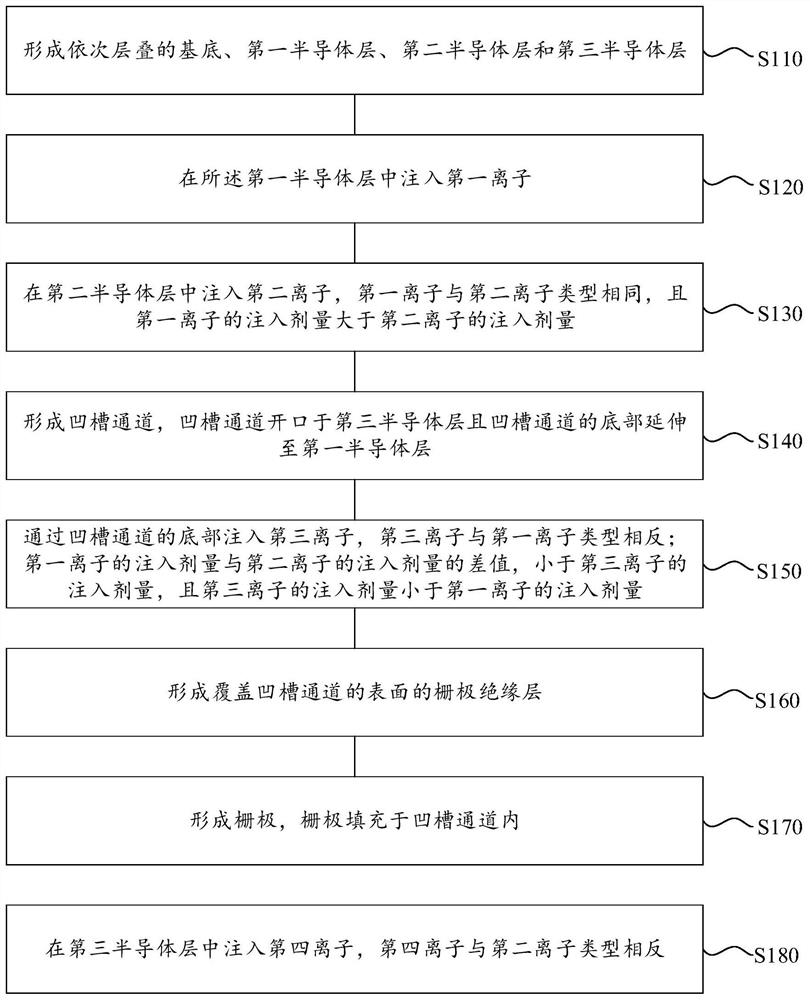

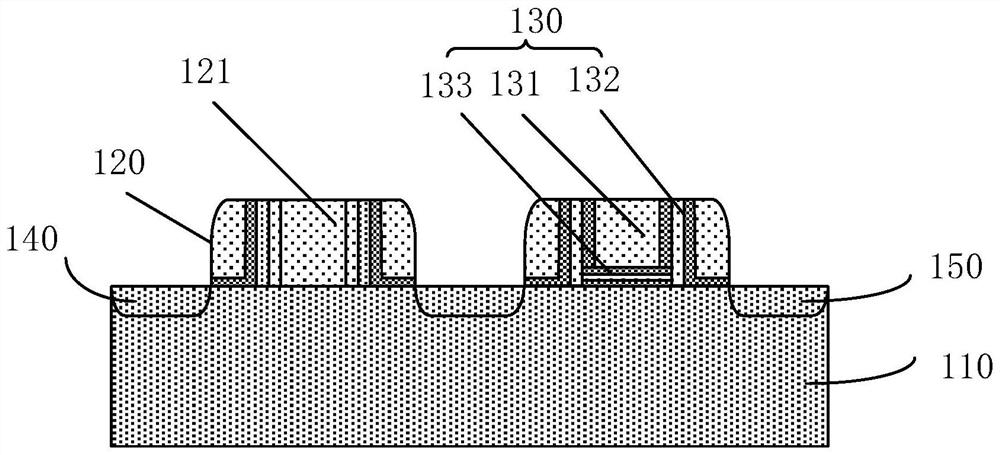

Memory device, recessed channel array transistor and manufacturing method thereof

ActiveCN112186035BThreshold voltage uniformSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Owner:CHANGXIN MEMORY TECH INC

Method of manufacturing nonvolatile memory device

InactiveUS7985647B2Suppress smile phenomenonImprove film qualitySolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerEngineering

Owner:SK HYNIX INC

3D memory device and manufacturing method thereof

ActiveCN109712983BConsistent lossSame distanceSolid-state devicesSemiconductor devicesGate stackHoneycomb structure

Disclosed is a 3D memory device, comprising: a substrate; a stacked structure on the substrate, the stacked structure including a plurality of conductor layers and a plurality of insulating layers stacked alternately; a plurality of memory strings running through the The stacked structure; a plurality of conductive channels running through the stacked structure; wherein, the plurality of storage strings are in a honeycomb structure, and each of the conductive channels is located at the center of the honeycomb structure and is used to pass through the substrate and supplying power to the plurality of storage strings around it. The present invention also provides a manufacturing method of the 3D memory device provided by the present invention, using the common source hole as a deposition channel to replace the sacrificial layer in the laminated structure with a conductor layer, and using the common source hole to form a common source conductive channel, avoiding the formation of gaps between the conductor layer in the gate stack structure and the common-source conductive channel.

Owner:YANGTZE MEMORY TECH CO LTD

Method of controlling threshold voltage and method of fabricating semiconductor device

ActiveUS20150050751A1Easy to controlThreshold voltage uniformSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of controlling a threshold voltage is provided. The method of controlling a threshold voltage includes performing a film-thickness measuring step to measure the thickness of a film layer on a wafer to obtain a film-thickness value. Then, at least one parameter is decided, selected, or generated according to the film-thickness value. Next, an ion implantation process is performed on the wafer, wherein the ion implantation process is executed according to the parameter to form a threshold voltage adjustment region in the wafer below the film layer.

Owner:UNITED MICROELECTRONICS CORP

How transistors are made

ActiveCN103915323BThreshold voltage uniformAvoid Irregular DamageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricOptoelectronics

The invention provides a method for manufacturing a transistor. The method comprises the steps of providing a substrate, wherein a false gate structure is formed on the substrate, the false gate structure comprises a gate dielectric layer, a protective layer located on the gate dielectric layer, an oxide layer located on the protective layer and a false gate located on the oxide layer, the gate dielectric layer is made of oxygen containing materials, and oxygen diffuses to the upper surface of the protective layer, so that an oxidation layer is formed; forming the source electrode and the drain electrode of the transistor after the false gate structure is formed; forming an interlayer dielectric layer on the substrate after the source electrode and the drain electrode are formed, wherein the upper surface of the false gate structure is exposed through the interlayer dielectric layer; eliminating the false gate, wherein a false gate trench is formed in the interlayer dielectric layer; eliminating the oxide layer and the oxidation layer after the false gate trench is formed; forming a gate electrode in the false gate trench after the oxide layer and the oxidation layer are eliminated. By the adoption of the method for manufacturing the transistor, the transistor can obtain an even threshold voltage, and therefore the performance of the transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

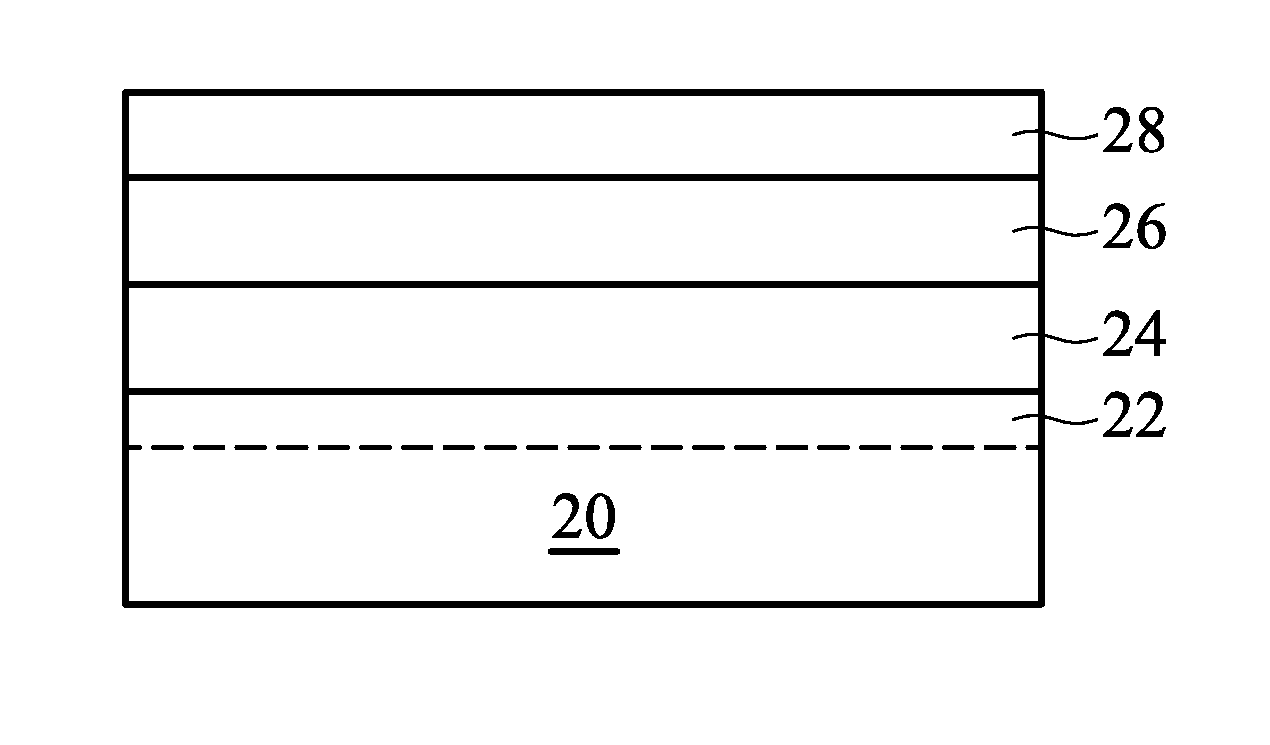

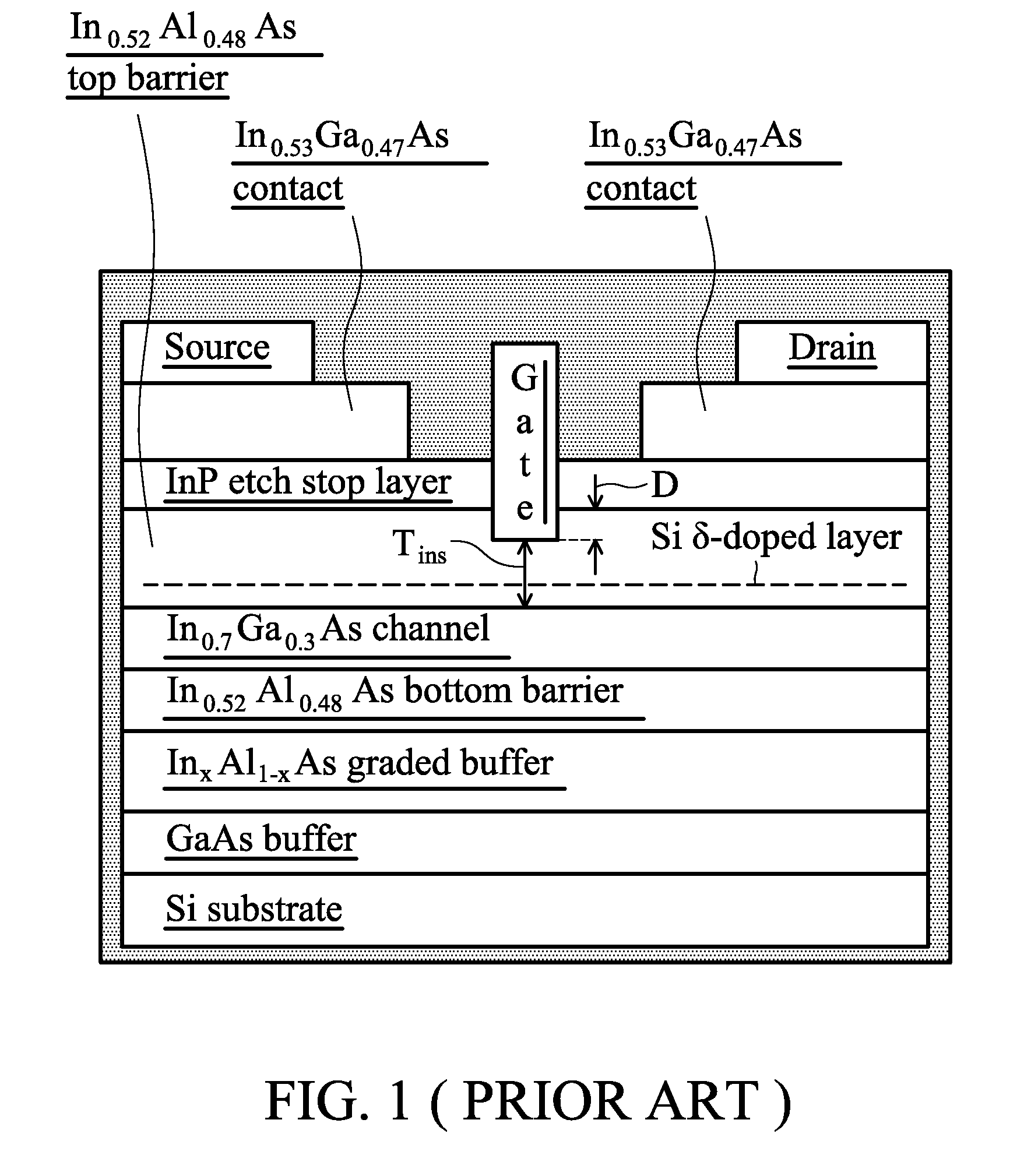

Source/drain re-growth for manufacturing III-V based transistors

ActiveUS8617976B2Improved short channel control of III-VThreshold voltage uniformSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorEngineering

A method of forming an integrated circuit structure includes providing a substrate, and epitaxially growing a first semiconductor layer over the substrate. The first semiconductor layer includes a first III-V compound semiconductor material formed of group III and group V elements. The method further includes forming a gate structure on the first semiconductor layer, and forming a gate spacer on at least one sidewall of the gate structure. After the step of forming the gate structure, a second semiconductor layer including a second III-V compound semiconductor material is epitaxially grown on the first semiconductor layer.

Owner:TAIWAN SEMICON MFG CO LTD

A kind of semiconductor device and its preparation method, electronic device

ActiveCN105097705BThreshold voltage uniformImprove performanceSolid-state devicesSemiconductor devicesPower semiconductor deviceEtching

Owner:SEMICON MFG INT (SHANGHAI) CORP

A process method for increasing the cell density of trench mosfet and the structure of trench mosfet

ActiveCN112103186BBest Avalanche Current CharacteristicsThreshold voltage uniformTransistorSemiconductor/solid-state device detailsEngineeringBoron atom

The invention discloses a process method for increasing the cell density of a trench MOSFET and a trench MOSFET structure, comprising the following steps: step S4: deposit polysilicon, remove polysilicon outside the trench, and remove the first nitride Silicon, forming a first doped region and a third doped region in the epitaxial layer, depositing second silicon nitride, etching the second silicon nitride, forming sidewalls on the sidewalls of the polysilicon, the The widths of the sidewalls formed by the left and right side walls of the polysilicon are equal; step S5: implant boron atoms or phosphorus atoms into the first doped region to form a second doped region, and the doping concentration of the second doped region is 20-100 times the doping concentration of the first doping region, removing the sidewall, removing the polysilicon protruding from the surface of the first oxide layer, depositing a dielectric layer and removing the dielectric layer and silicon in the set area, A source contact hole is formed. The process method for increasing the cell density of the trench MOSFET and the structure of the trench MOSFET provided by the invention have the advantages of realizing more uniform threshold voltage and on-resistance.

Owner:深圳市芯电元科技有限公司

Method of Manufacturing Nonvolatile Memory Device

InactiveUS20110244648A1Suppress smile phenomenonImprove film qualitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringNitride

Owner:SK HYNIX INC

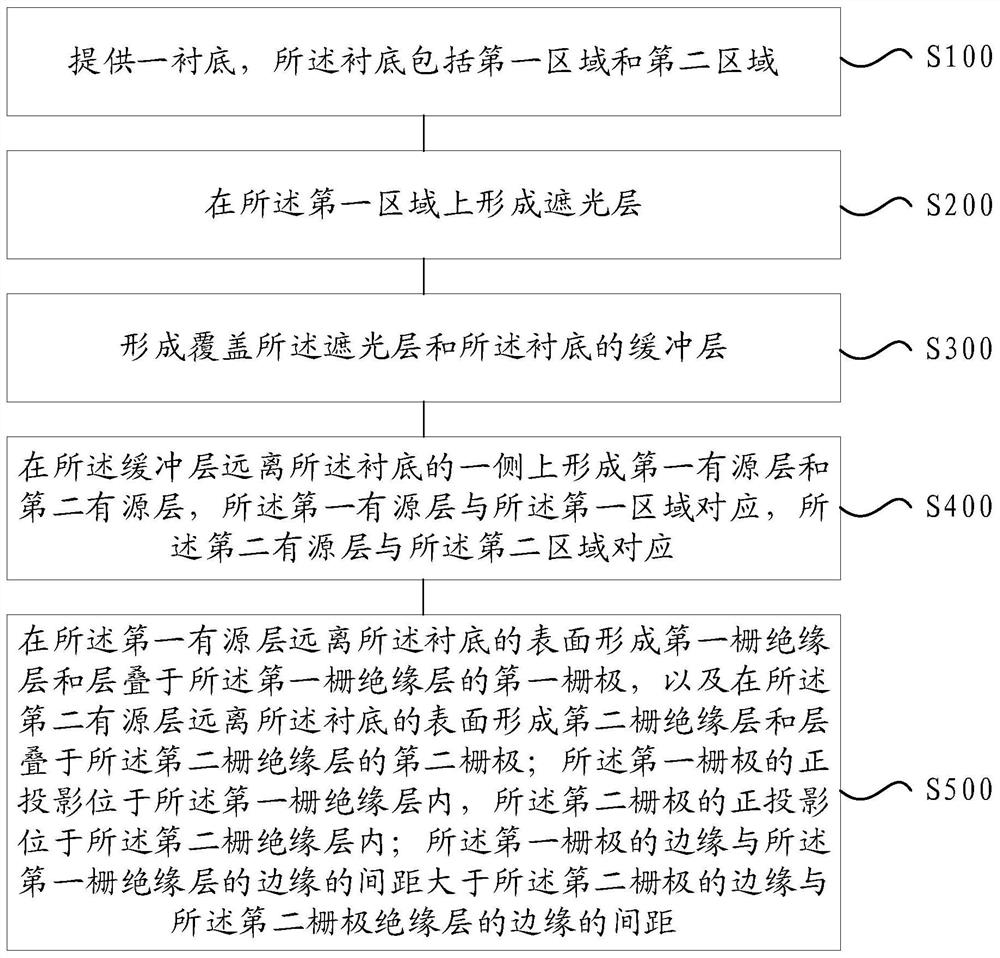

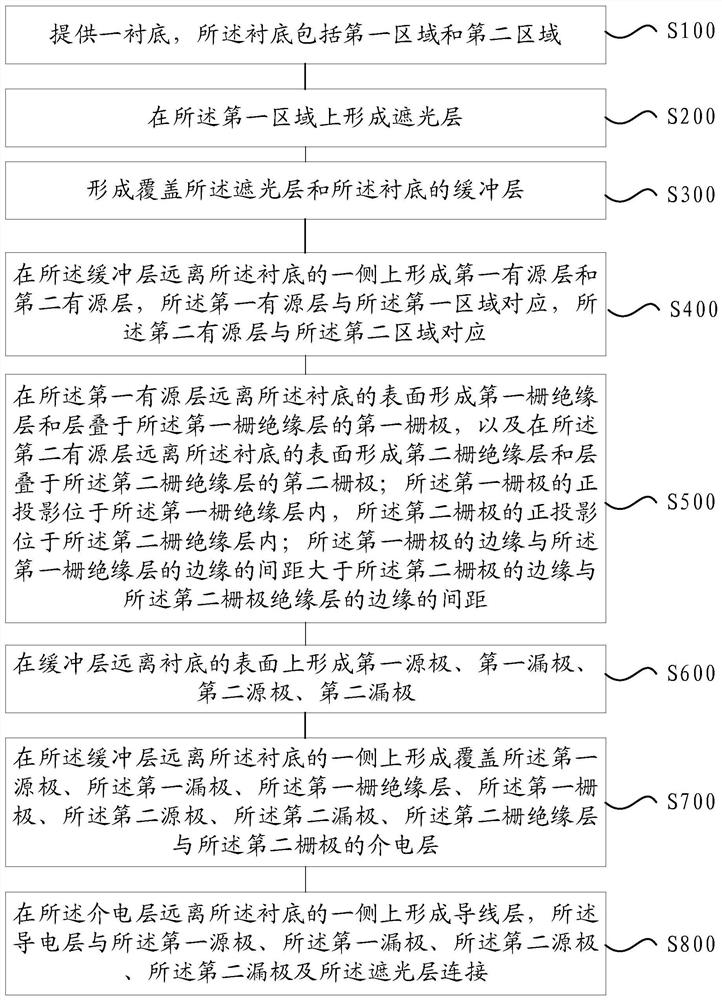

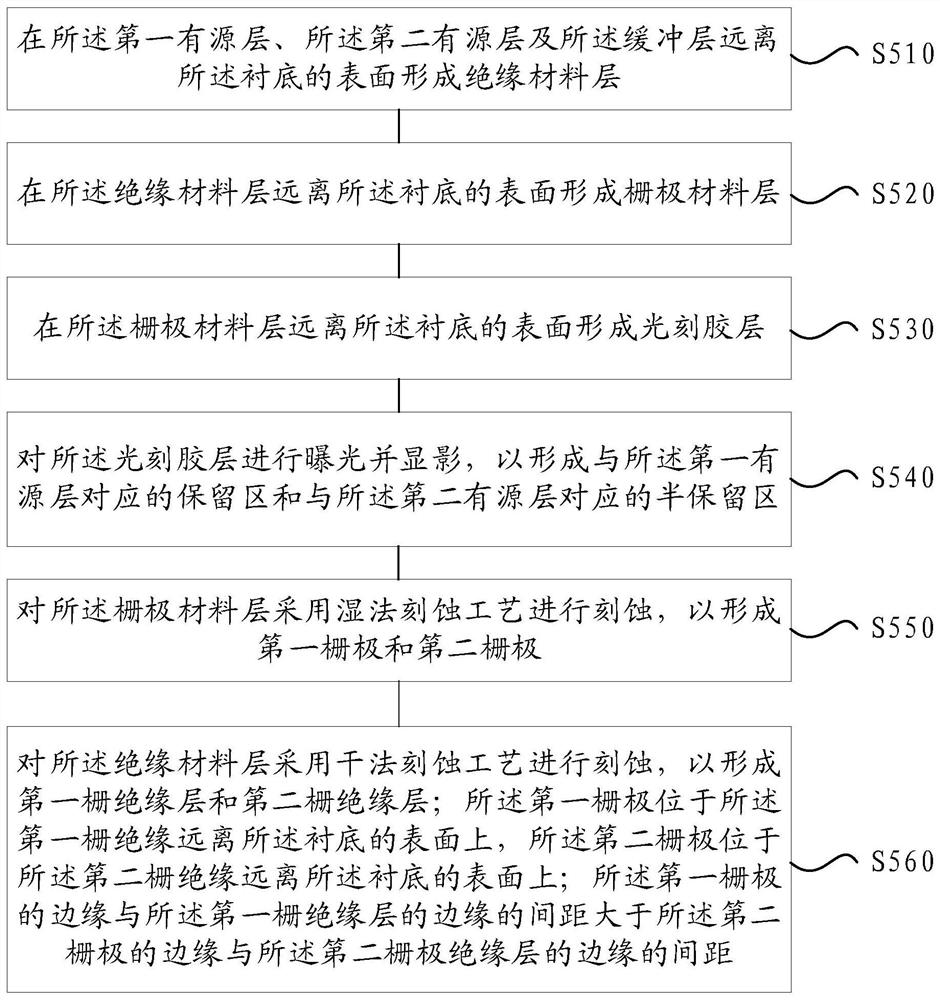

Display device, display panel, array substrate and manufacturing method thereof

ActiveCN109585367BImprove performanceImprove display qualitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceGate stack

The disclosure relates to a method for manufacturing an array substrate, the array substrate, a display panel and a display device. The manufacturing method includes: providing a substrate, the substrate includes a first region and a second region; forming a light-shielding layer on the first region; forming a buffer layer covering the light-shielding layer and the substrate; The first active layer and the second active layer, the first active layer corresponds to the first region, and the second active layer corresponds to the second region; the first gate insulation is formed on the surface of the first active layer away from the substrate layer and the first gate stacked on the first gate insulating layer, and a second gate insulating layer and a second gate stacked on the second gate insulating layer are formed on the surface of the second active layer away from the substrate; the first gate The orthographic projection of the pole is located in the first gate insulating layer, and the orthographic projection of the second gate is located in the second gate insulating layer; the distance between the edge of the first gate and the edge of the first gate insulating layer is greater than the edge of the second gate The spacing from the edge of the second gate insulating layer.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

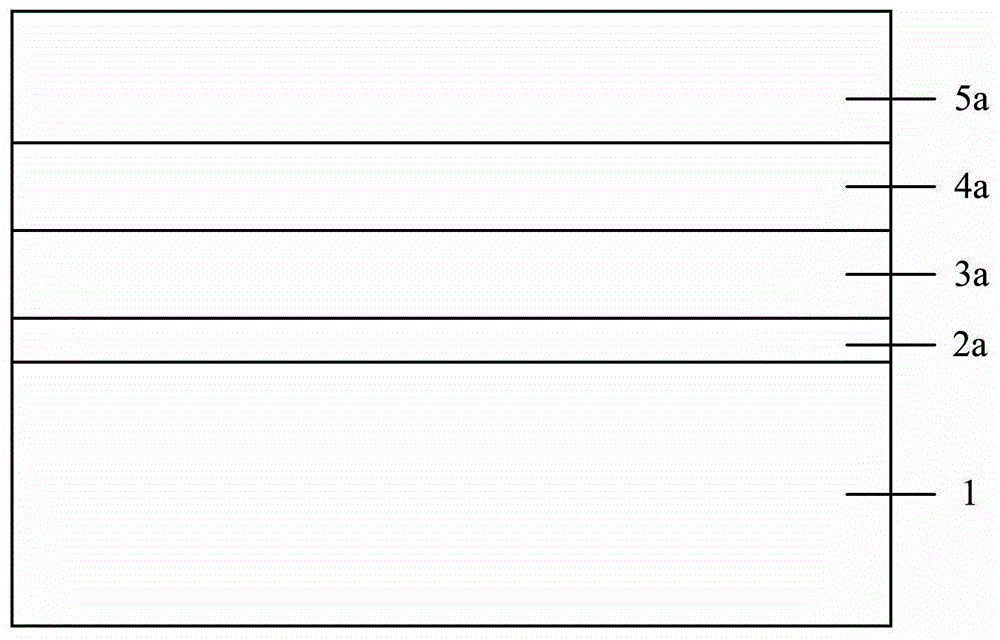

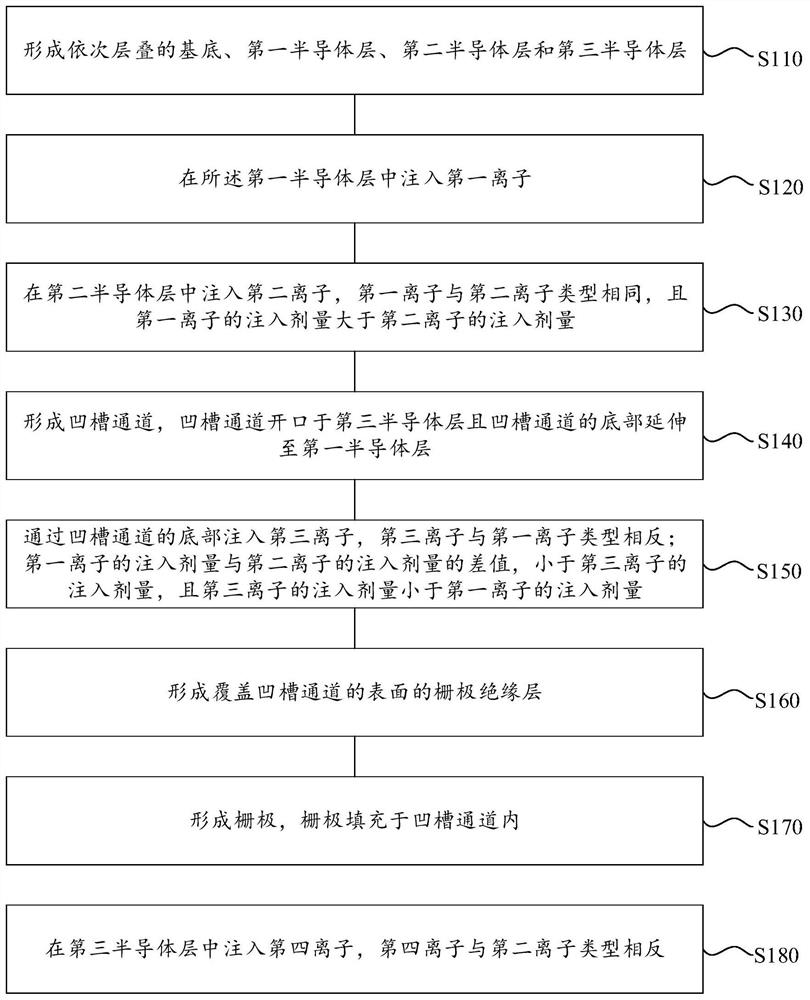

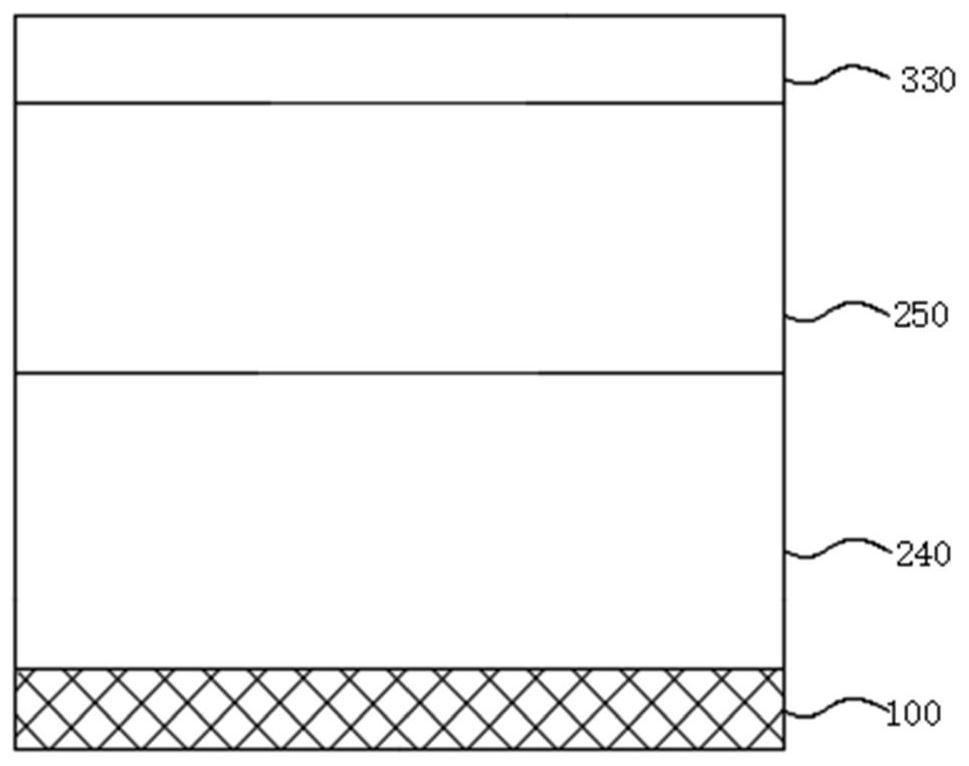

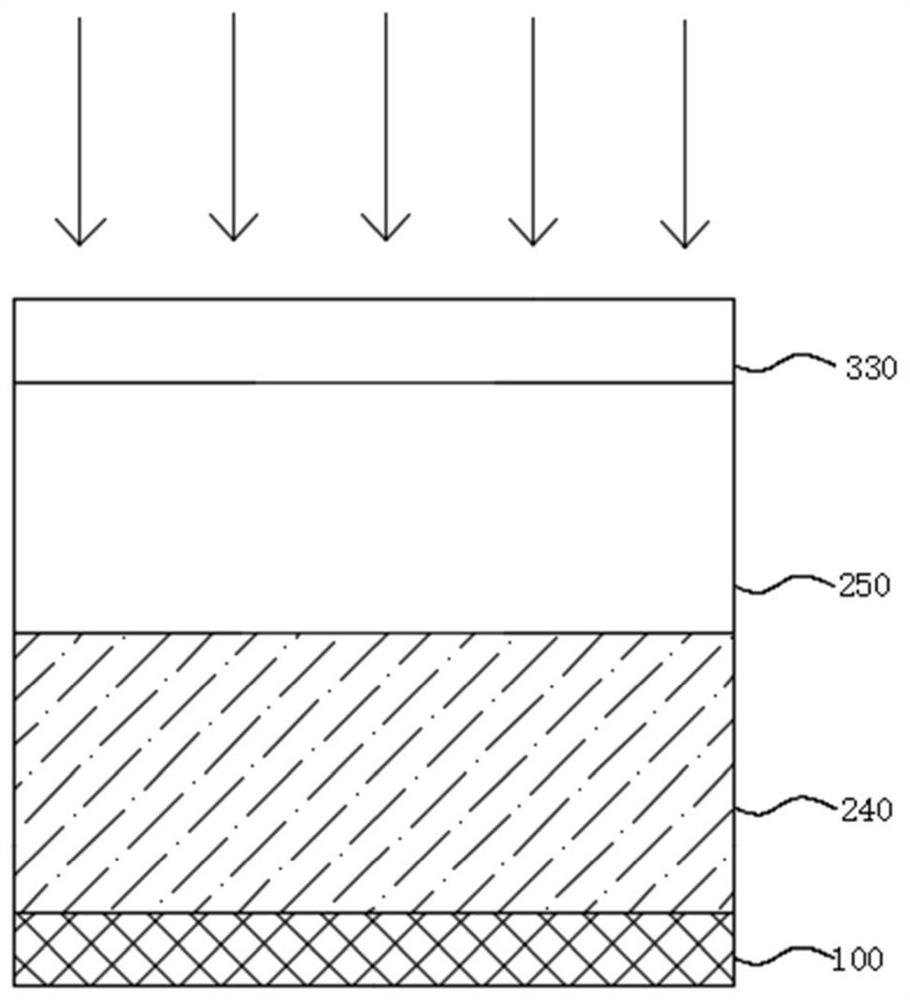

Memory device, recessed channel array transistor and preparation method thereof

ActiveCN112186035AThreshold voltage uniformSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention provides a storage device, a recessed channel array transistor and a preparation method thereof, and belongs to the technical field of storage. The preparation method of the recessed channel array transistor comprises the steps of forming a substrate, a first semiconductor layer, a second semiconductor layer and a third semiconductor layer which are stacked in sequence; implanting first ions into the first semiconductor layer; implanting second ions of the same type as the first ions into the second semiconductor layer, wherein the implantation dose is greater than that of the second ions; forming a groove channel with an opening in the third semiconductor layer and extending to the first semiconductor layer; injecting third ions opposite to the first ions in type through thebottom of the groove channel, wherein the difference between the implantation dose of the first ions and the implantation dose of the second ions is smaller than the implantation dose of the third ions; forming a gate insulating layer and a gate; and injecting fourth ions opposite to the second ions in type into the third semiconductor layer. According to the preparation method of the recessed channel array transistor, the uniformity of the threshold voltage of the recessed channel array transistor can be improved.

Owner:CHANGXIN MEMORY TECH INC

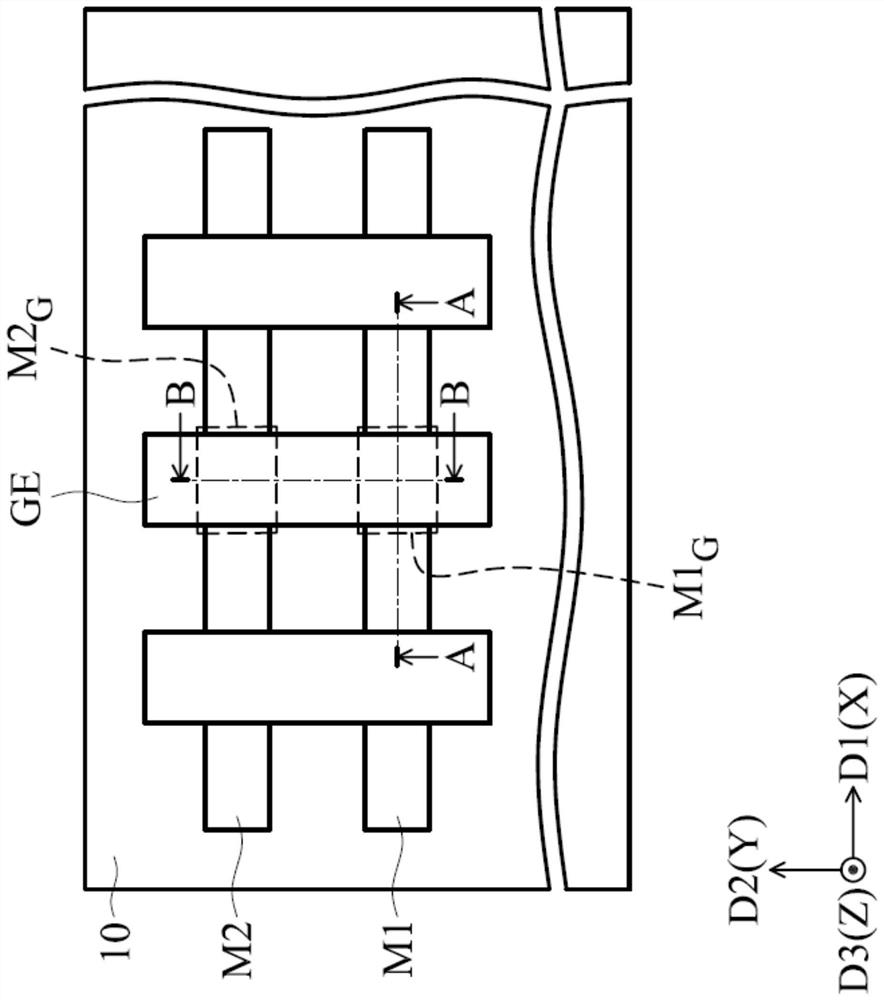

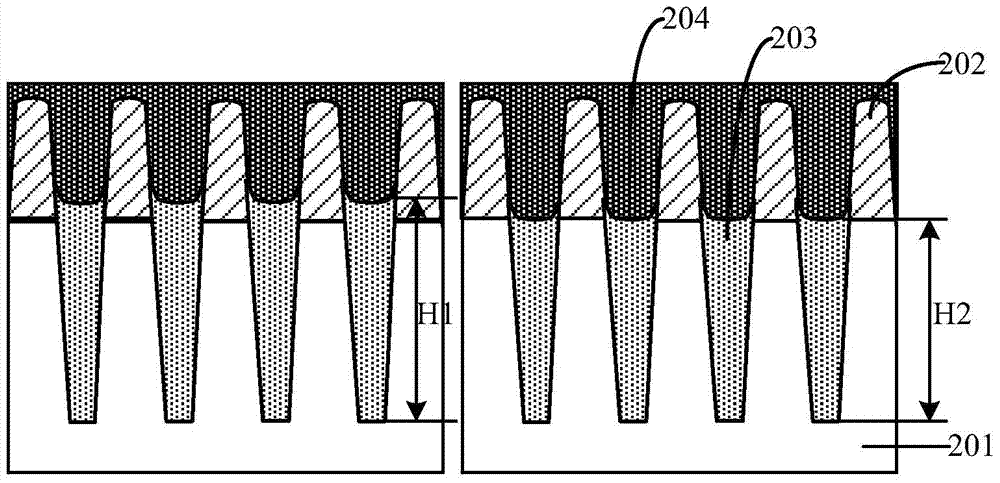

Transistors and methods of forming them

ActiveCN105990113BThe overall thickness is thinThreshold voltage uniformSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A transistor and a forming method thereof are disclosed. The forming method of the transistor comprises the following steps: providing a substrate with a pseudo gate film on the surface; etching part of the pseudo gate film in the thickness direction; after etching part of the pseudo gate film in the thickness direction, forming a second initial pseudo gate layer and a plurality of first initial pseudo gate layers on the surface of the second initial pseudo gate layer, wherein a first opening is formed between every two adjacent second initial pseudo gate layers; oxidizing the sidewalls of the first initial pseudo gate layers and the second initial pseudo gate layer on the bottoms of the first openings, forming a first oxide layer on the sidewall surfaces of the first initial pseudo gate layers, and making the second initial pseudo gate layer on the bottoms of the first openings form a second oxide layer and the remaining second initial pseudo gate layer and first initial pseudo gate layers form pseudo gates, wherein the bottom size of the pseudo gates is greater than the top size; forming a dielectric layer on the surface of substrate, wherein the dielectric layer exposes the top surfaces of the pseudo gates; removing the pseudo gates, and forming second openings in the dielectric layer; and forming gate structures in the second openings. The performance of the formed transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

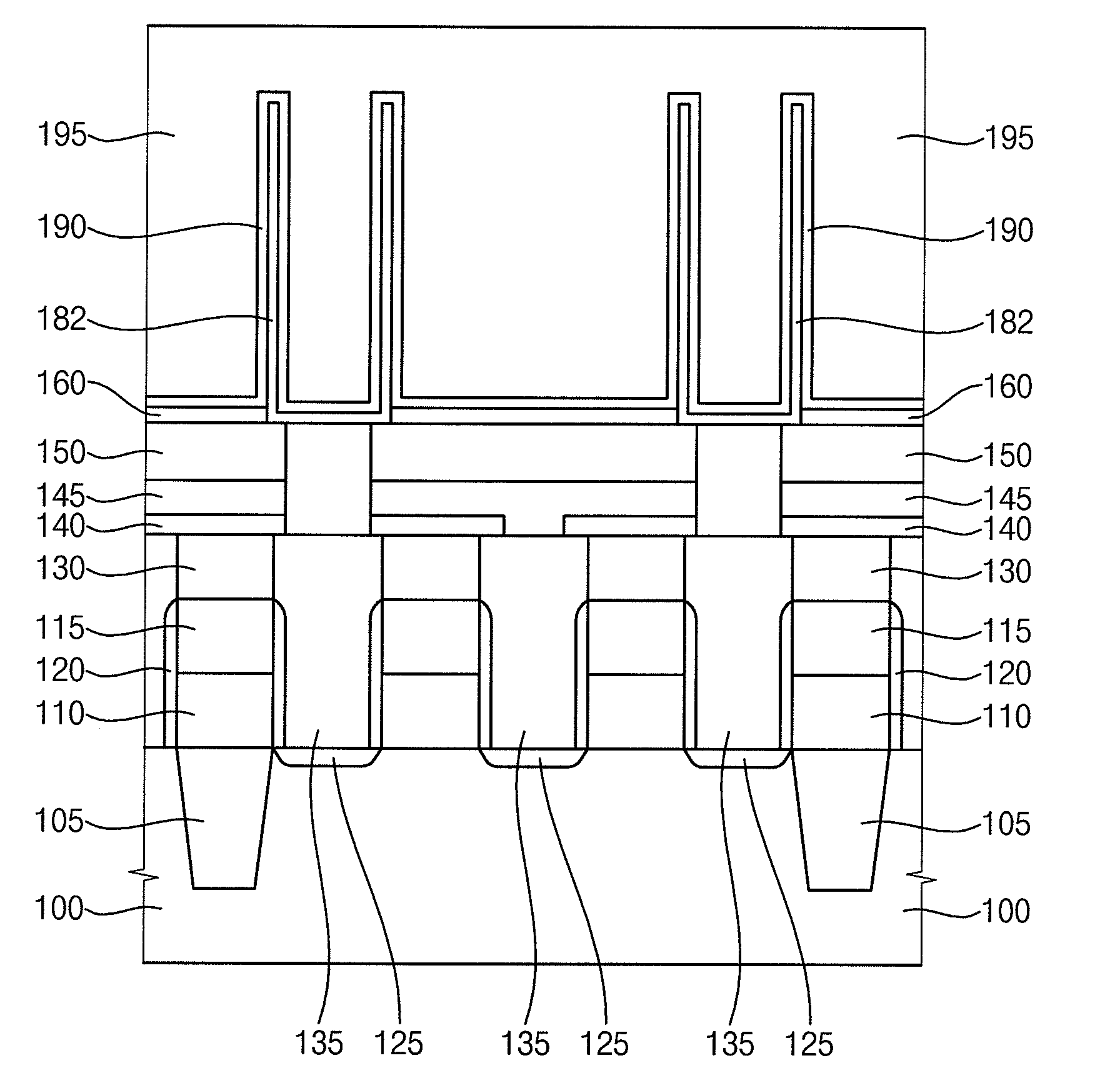

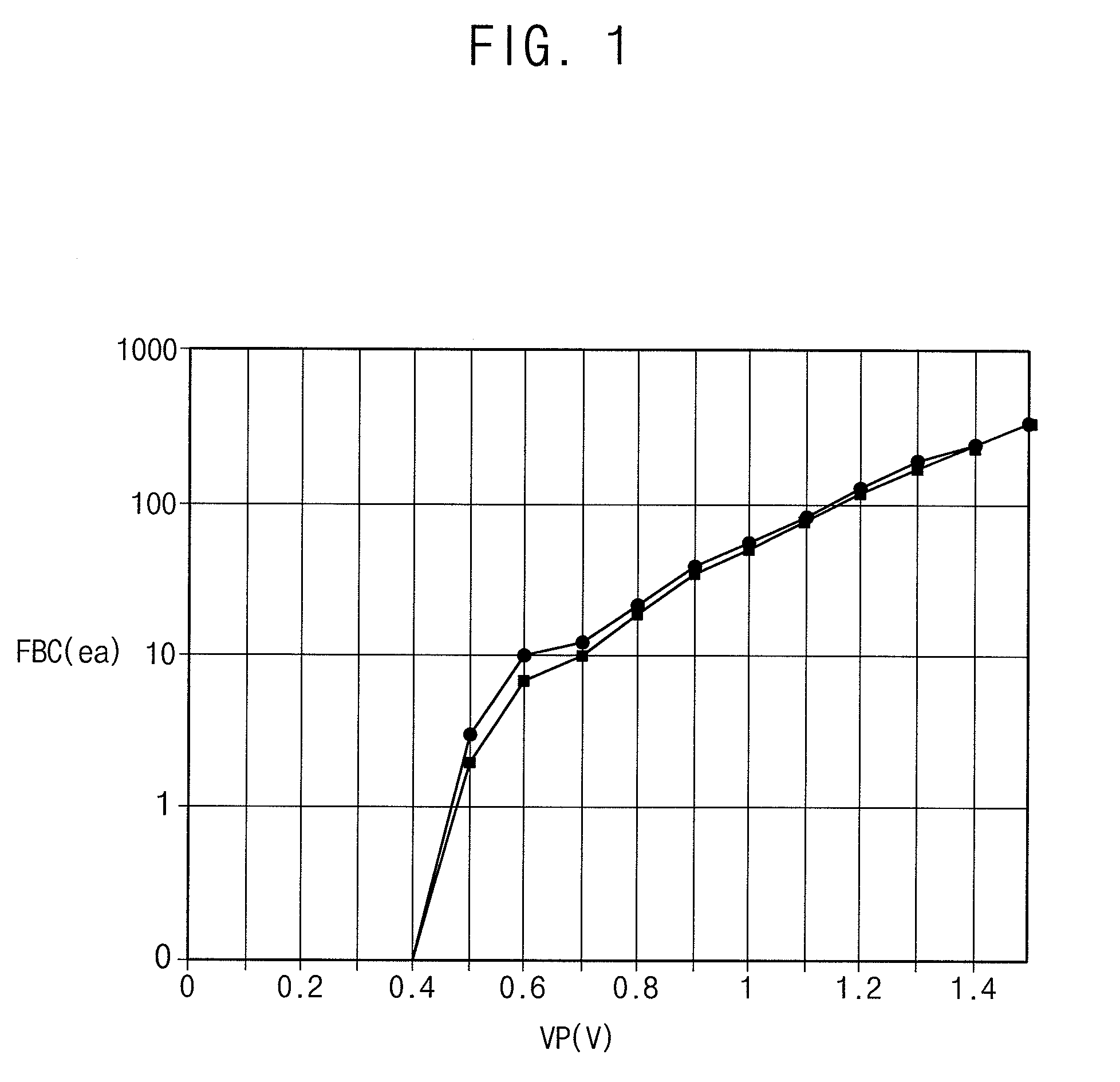

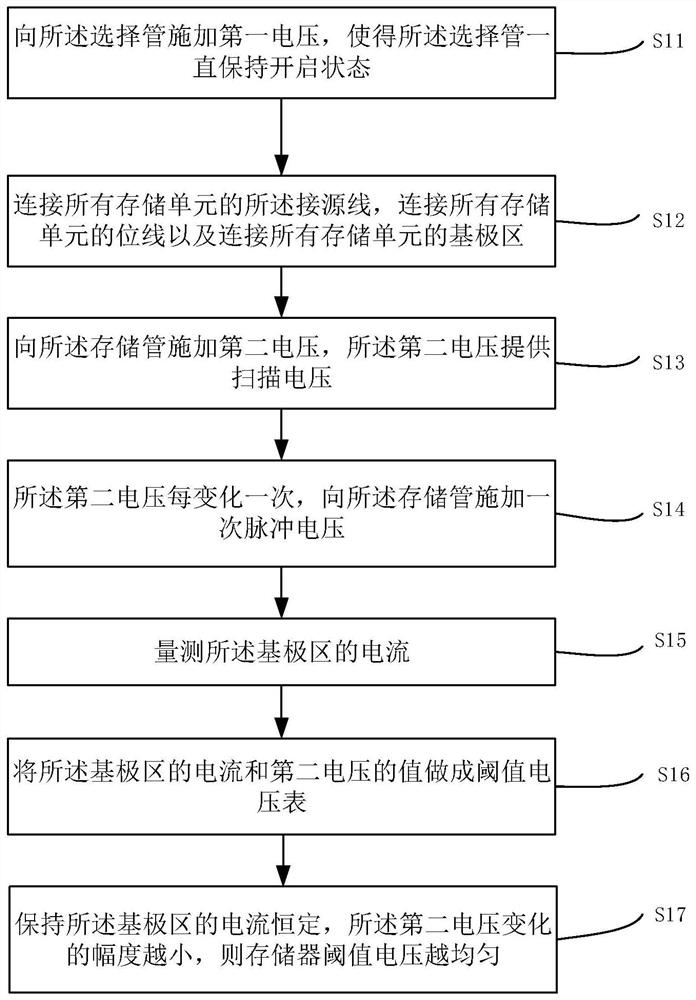

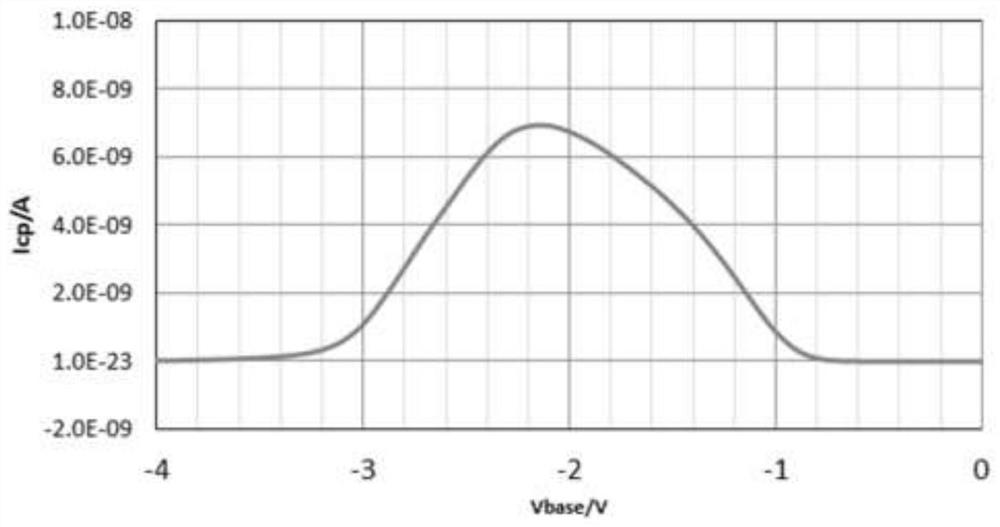

Electrical testing method for threshold voltage uniformity of memory

PendingCN112489716AThreshold voltage uniformShorten the timeSemiconductor/solid-state device testing/measurementStatic storageVoltmeterControl theory

The invention provides an electrical property test method for threshold voltage uniformity of a memory, which comprises the following steps of: applying a first voltage to a selection tube to enable the selection tube to be always opened; connecting the source connecting lines of all the storage units; connecting the bit lines of all the storage units; connecting the base regions of all the storage units; applying a second voltage to the memory tube, wherein the second voltage is a scanning voltage; applying a pulse voltage to the storage tube once when the second voltage changes once; measuring the current of the base region; making the values of the current and the second voltage of the base region into a threshold voltmeter; keeping current of the base region is kept constant, wherein the smaller the change amplitude of the second voltage is, the more uniform the threshold voltage of the memory is. According to the invention, the threshold voltages of all the memory cells can be simultaneously tested without using an additional test structure so as to judge whether the threshold voltages of the memory are uniform or not, the test is simple, a test program does not need to be written, the test time is short, and the memory development time is reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP