Multi-node memory interconnection device and large-scale computer cluster

A multi-node, computer technology, applied in the direction of computers, multi-program devices, digital computer components, etc., can solve problems affecting computer performance, large resources, unfavorable maintenance and upgrade of memory devices, etc., to avoid excessive consumption of processor resources , Improving migration efficiency and shortening the data migration path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

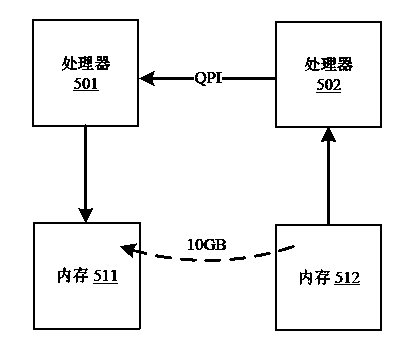

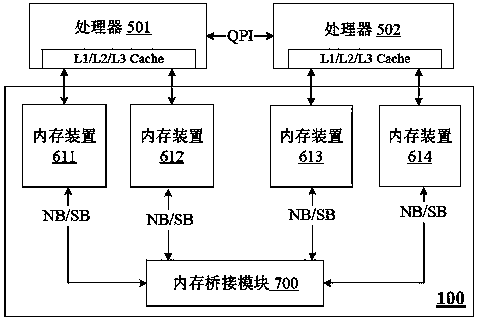

[0043] Please refer to figure 2 , image 3 , Figure 6 , Figure 9 with Figure 10 A specific implementation manner of a multi-node memory interconnection device of the present invention is shown.

[0044] In this embodiment, the multi-node memory interconnection device 100 includes four memory devices 611 , 612 , 613 , 614 connected to the designated processors 501 , 502 . It should be noted that this embodiment is only an illustration, and the number of processors and memory devices is not limited during actual application.

[0045] Meanwhile, for ease of illustration, in this embodiment, the processor 501 is connected to the memory devices 611 and 612 in series, and the processor 502 is connected to the memory devices 613 and 614 in series.

[0046] In this embodiment, the memory devices 611 , 612 , 613 , and 614 are preferably non-volatile memory devices. It should be noted that, part or all of the memory devices 611, 612, 613, 614 can also be selected as common vol...

Embodiment 2

[0066] Please refer to Figure 4 Another specific implementation manner of a multi-node memory interconnection device of the present invention is shown. The main difference between this embodiment and Embodiment 1 is that in this embodiment, the multi-node memory interconnection device 100 also includes an external data sending port 7111 and an external data receiving port 7211 connected to the media access control module 704, and through the Data migration between the protocol analysis module 705 and the communication port 706 and the external computer.

[0067]Specifically, in this embodiment, the protocol analysis module 705 is selected from a WiFi analysis module. Meanwhile, the system bus 7031 is a PCI-e protocol bus. PCI-e is a high-speed serial point-to-point dual-channel high-speed broadband transmission bus form, including PCI-e X1\X2\X4\X8\X16; it can choose a specific PCI according to the storage scale of the entire multi-node memory interconnection device 100 -e...

Embodiment 3

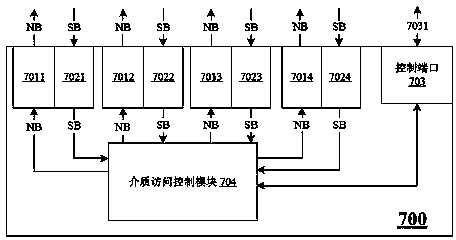

[0070] Please refer to figure 2 , Figure 5 , Figure 7 with Figure 8 The third specific implementation manner of a multi-node memory interconnection device of the present invention is shown.

[0071] When the computer is turned on, the firmware will perform memory detection to obtain the physical address range (including the start address and end address) and port information of each memory device 611, 612, 613, 614, and generate such as Figure 5 The shown port mapping table is then sent to the memory bridge module 700 through the control port 703 . For example: when a memory device 611 with a memory capacity of 64 GB is plugged into the first SMI slot on the motherboard, the physical address range of the memory device 611 is 0x0000000000000000~0x0000000FFFFFFFF, and the port number is 0; the physical address of the memory device 612 The range is 0x0000001000000000~0x0000001FFFFFFFF, the port number is 1; the physical address range of the memory device 613 is 0x0000002...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More