Sige body region vertical 1t-dram device and its manufacturing method

A 1T-DRAM, device manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as incompatibility, body area potential limitation, difficult heat dissipation, etc., to improve integration, reduce Cell area, effect of increasing signal margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Hereinafter, the present invention is described by means of specific embodiments shown in the drawings. It should be understood, however, that these descriptions are exemplary only and are not intended to limit the scope of the present invention. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concept of the present invention.

[0026] First of all, the present invention provides a method for manufacturing a semiconductor device, the manufacturing process of which is shown in the appended Figure 1-20 .

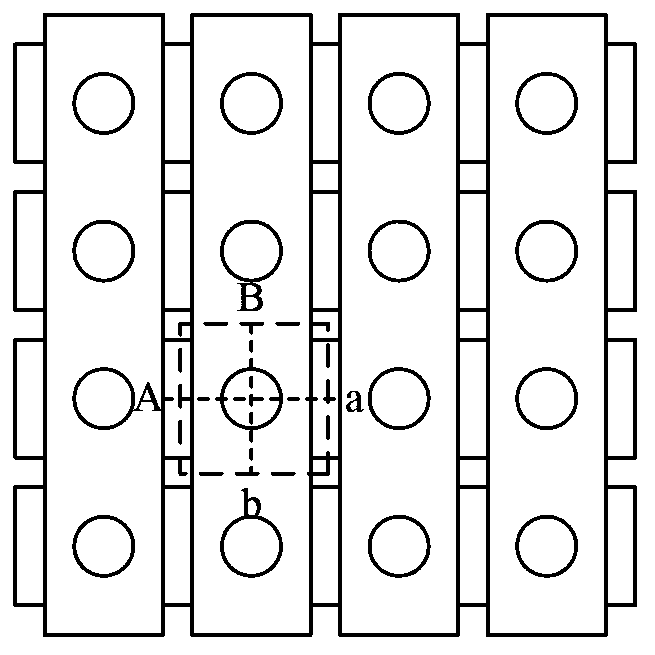

[0027] First, see attached figure 1 , is a layout of the 1T-DRAM device structure and array in the embodiment of the present invention, including three layers. figure 1 A 1T-DRAM unit is inside the dotted box. The horizontal dotted line Aa indicates the direction along which the bit line extends, and the vertical dotted line Bb indicates the direction along which the word lin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More