Integrated passive capacitor fan-out wafer-level packaging structure and manufacturing method

A technology of wafer-level packaging and integrated passives, applied in circuits, electrical components, electrical solid-state devices, etc., can solve problems such as factors that cannot improve the quality of circuits, properties of controlled semiconductor materials, etc., to shorten the length of electrical connections and improve electrical quality , Improve the effect of quality factor Q value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with specific drawings.

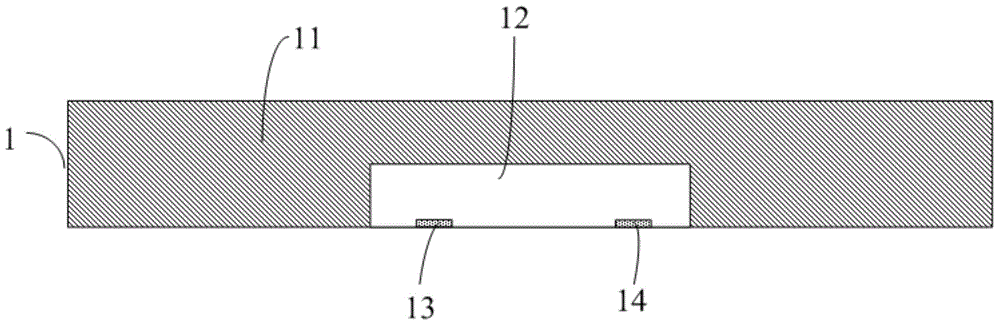

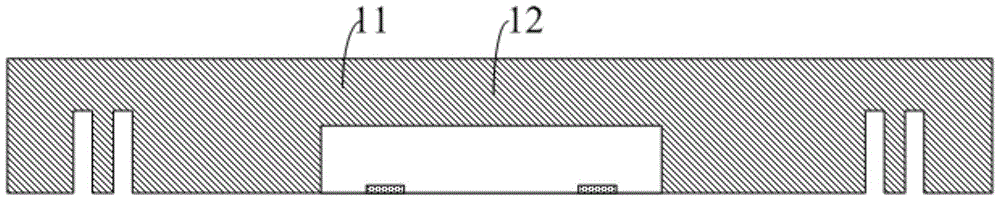

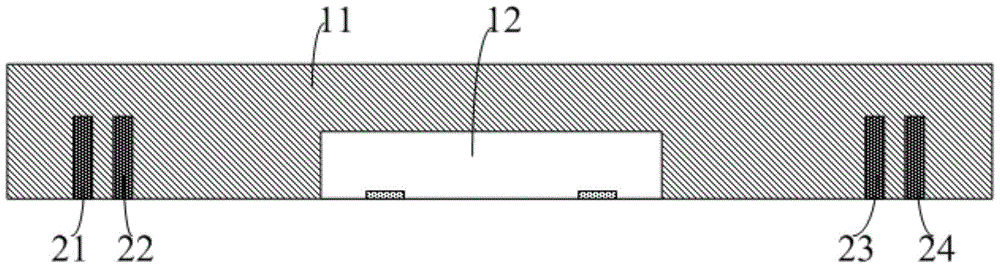

[0031] Such as Figure 10 As shown: the integrated passive capacitance fan-out wafer level packaging structure includes a fan-out package body 1, and the fan-out type package body 1 includes a plastic package body 11 and a chip 12 plastically sealed in the plastic package body 11, and the front side of the chip 12 With the first electrode 13 and the second electrode 14, the front of the chip 12 is flush with the front of the plastic package 11; two sets of capacitors are arranged in the plastic package 11, respectively the first metal post 21, the second metal post 22, The third metal post 23 and the fourth metal post 24, the first metal post 21 and the second metal post 22 are located on one side of the chip 12, and the third metal post 23 and the fourth metal post 24 are located on the other side of the chip 12; The front side of the plastic package 11 is provided with an i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More