A multi-channel data cache implementation method based on fpga/cpld

An implementation method and data caching technology, which is applied in the direction of electrical digital data processing, memory systems, instruments, etc., can solve problems such as waste of storage space, complex control logic, and data packet loss, and achieve the effect of simplifying the difficulty of programming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

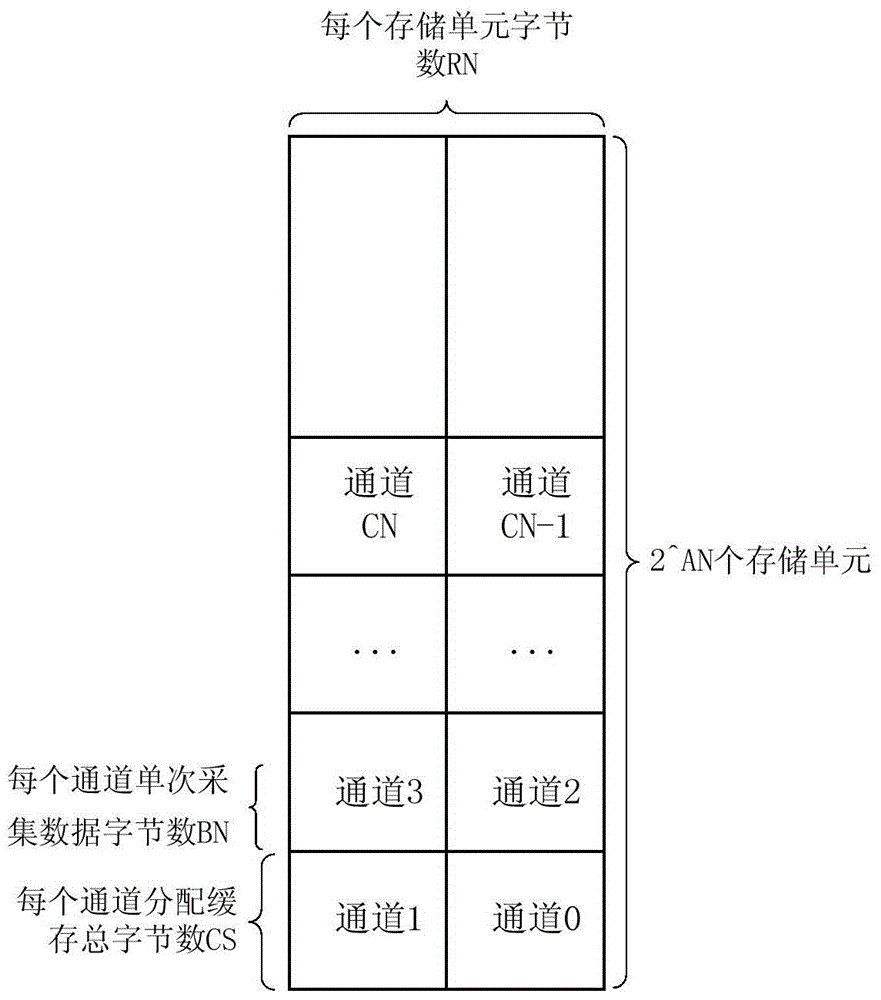

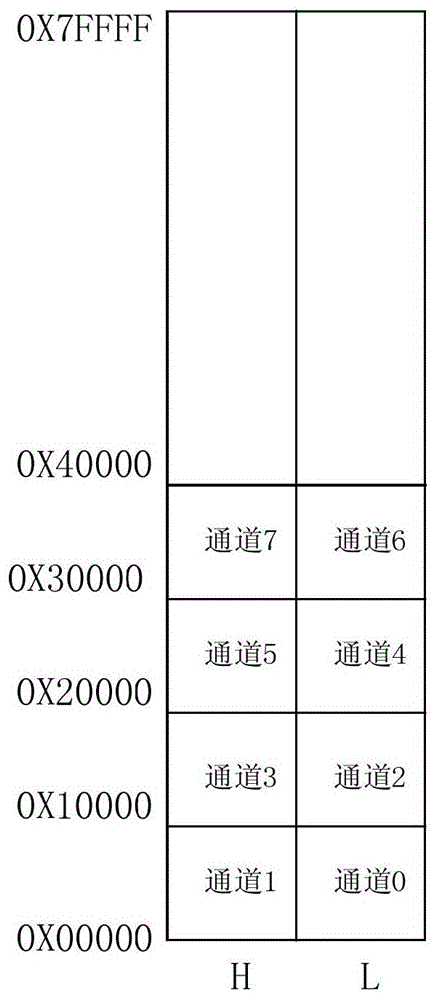

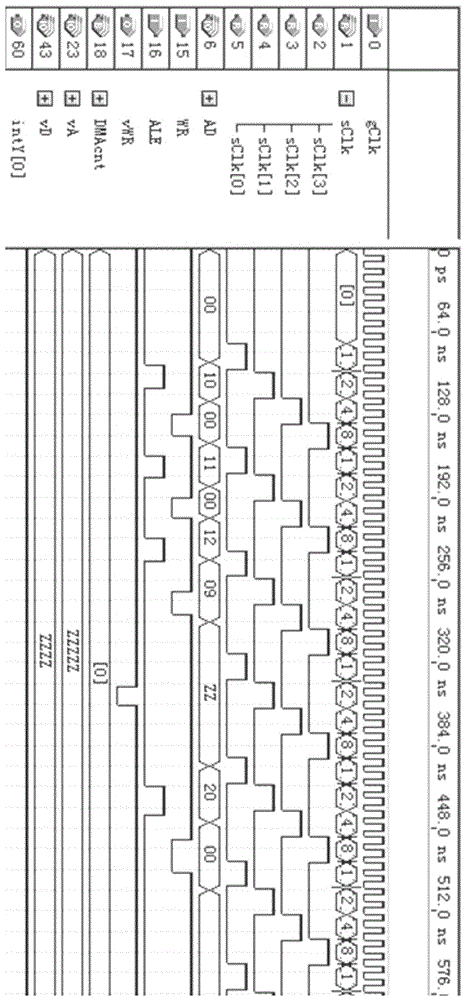

[0036] refer to figure 1 , figure 2 , image 3 , Figure 4 , Figure 5 , Image 6 , Figure 7 , Figure 8 and Figure 9 , the RAM is 512x16bit, that is, AN is equal to 19, RN is equal to 2, the number of channels is CN, etc. 8, the data collected by each channel is 32 bits, that is, BN is equal to 4, and the size of each channel in the RAM is 64K bytes. The following steps:

[0037] 1) divide the RAM, each storage unit in the RAM is 2 bytes, so each storage unit of the RAM is divided into 2 single-byte units;

[0038] 2) Divide an independent buffer area for each channel in the RAM, and the number of bytes of each buffer area is divided into 64Kbits. Among them, the buffer area occupies half of the RAM space, so the highest address of the RAM is set to 0 in the FPGA, i.e. A 18 equal to 0;

[0039] 3) The microcontroller writes the lower 8 bits of the initial target address into ADDR_BUF[7..0] of the CPLD / FPGA address register, the operation port is 0x8010, the oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More