Layout verification method used for polysilicon cell edge structure in FinFET standard cells

A standard cell, polysilicon technology for special data processing applications, instrumentation, total factory control, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

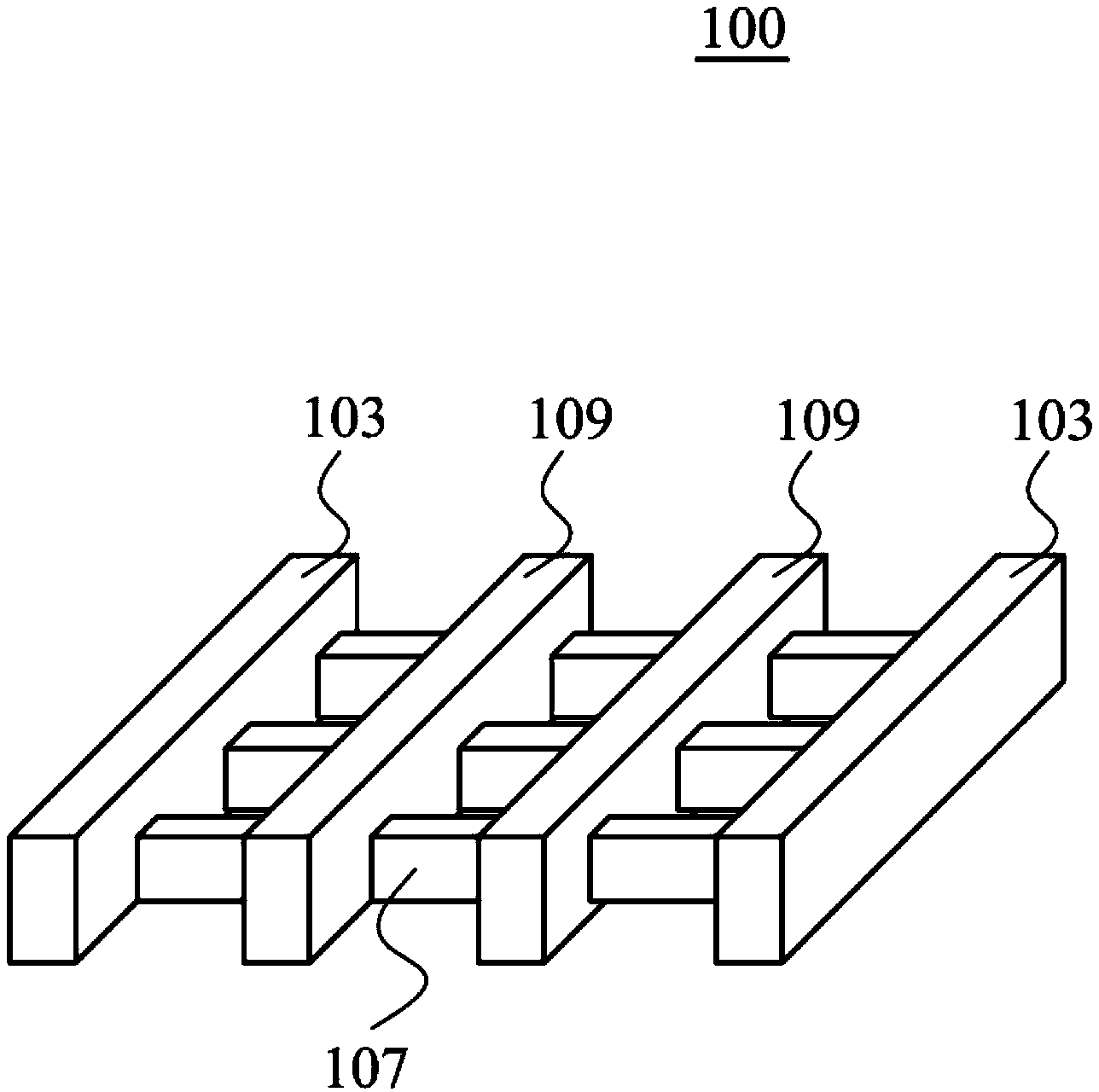

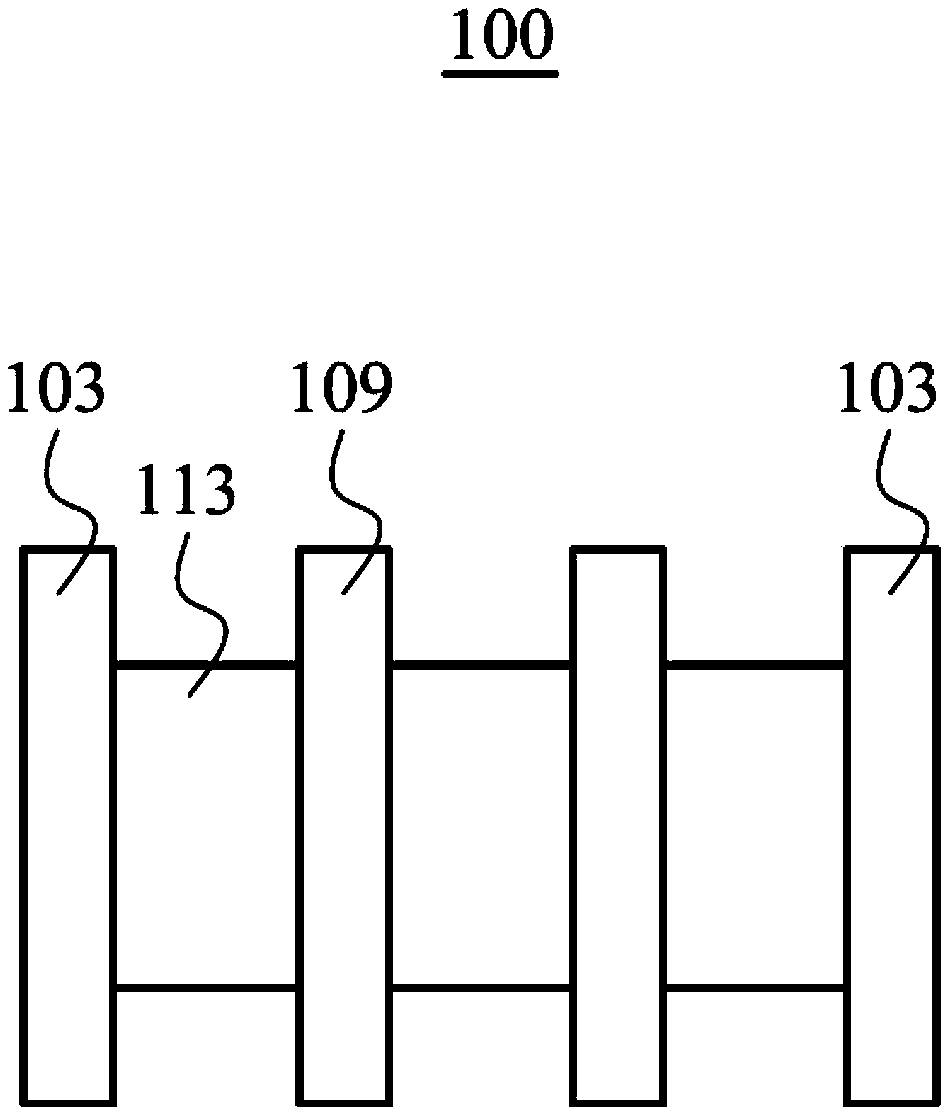

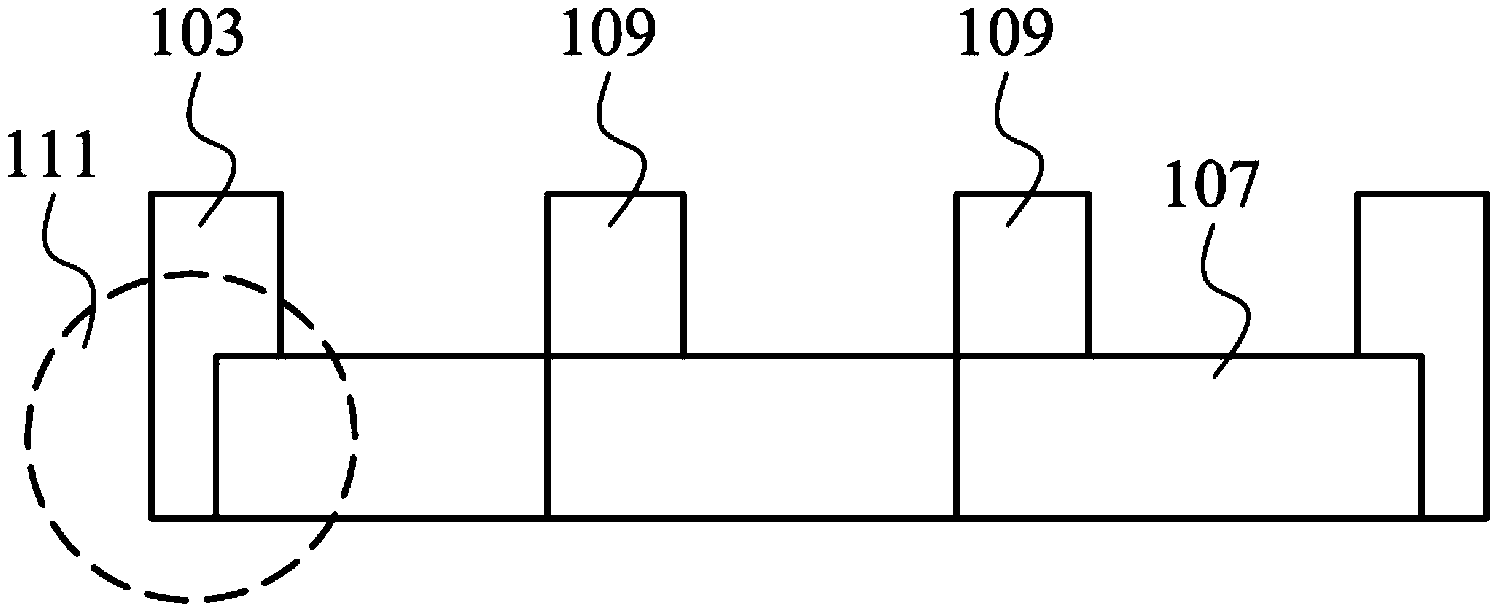

Image

Examples

Embodiment Construction

[0060] The making and using of exemplary embodiments of the invention are discussed in detail below. It should be appreciated, however, that the described embodiments provide many applicable concepts that can be implemented in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use various embodiments, and do not limit the scope of the description or the appended claims.

[0061] In standard cell design, a user such as an integrated circuit designer uses a suite of software tools that are applied in conjunction to form a design flow. Workstations or personal computers, which can include portable and removable devices such as laptops and tablets and even smartphone devices, can be used to work with the design tools. Shared data files for the design can be stored in non-volatile memory such as a disk or flash memory device, or on a server connected to a network or even accessed on an Internet port. These ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More