Failure analysis method for gate oxide defect original appearance

A technology for gate oxide layer and failure analysis, which is applied in the direction of electrical components, circuits, semiconductor/solid-state device testing/measurement, etc., and can solve problems such as unrecorded technical characteristics of gate oxide layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

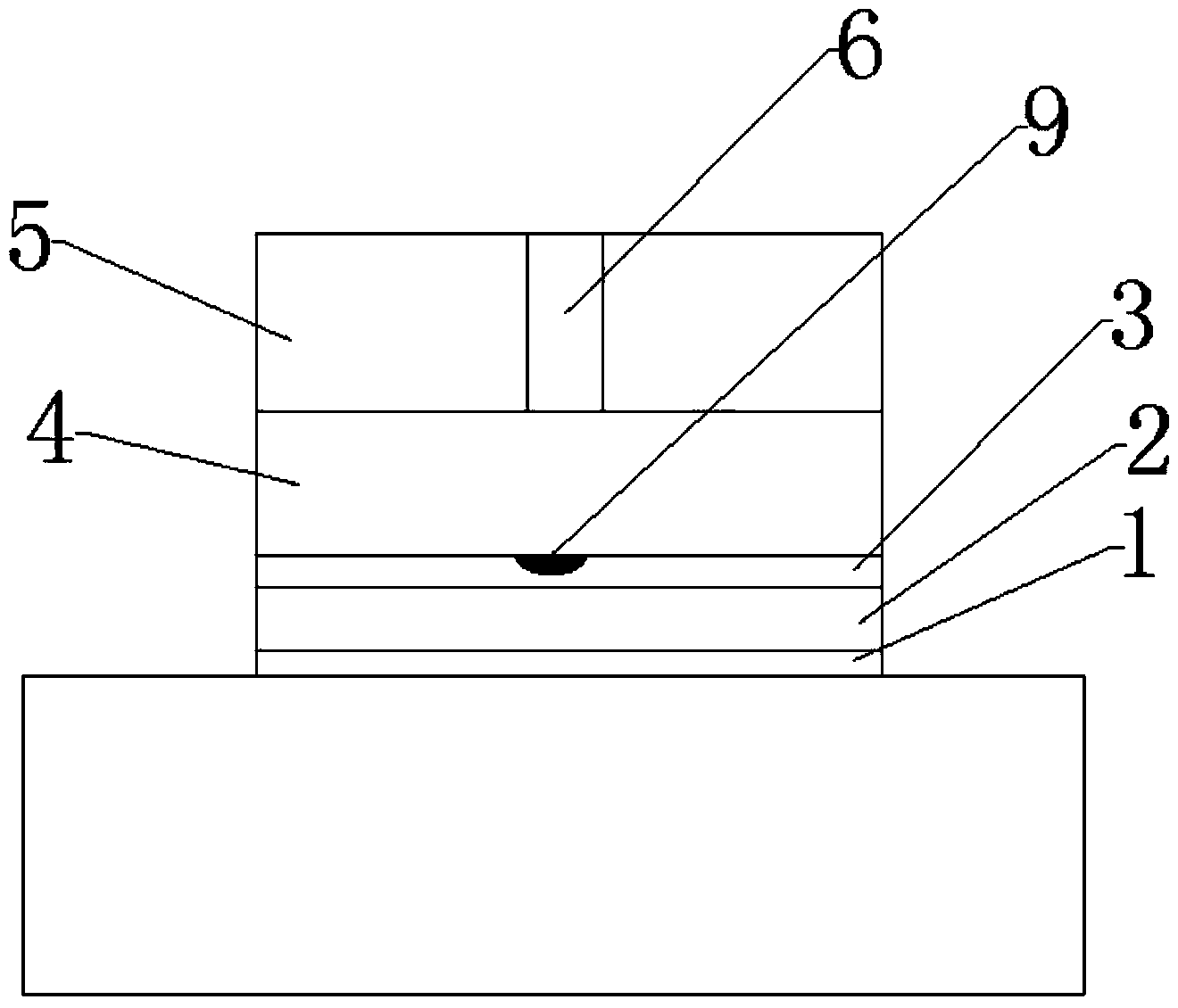

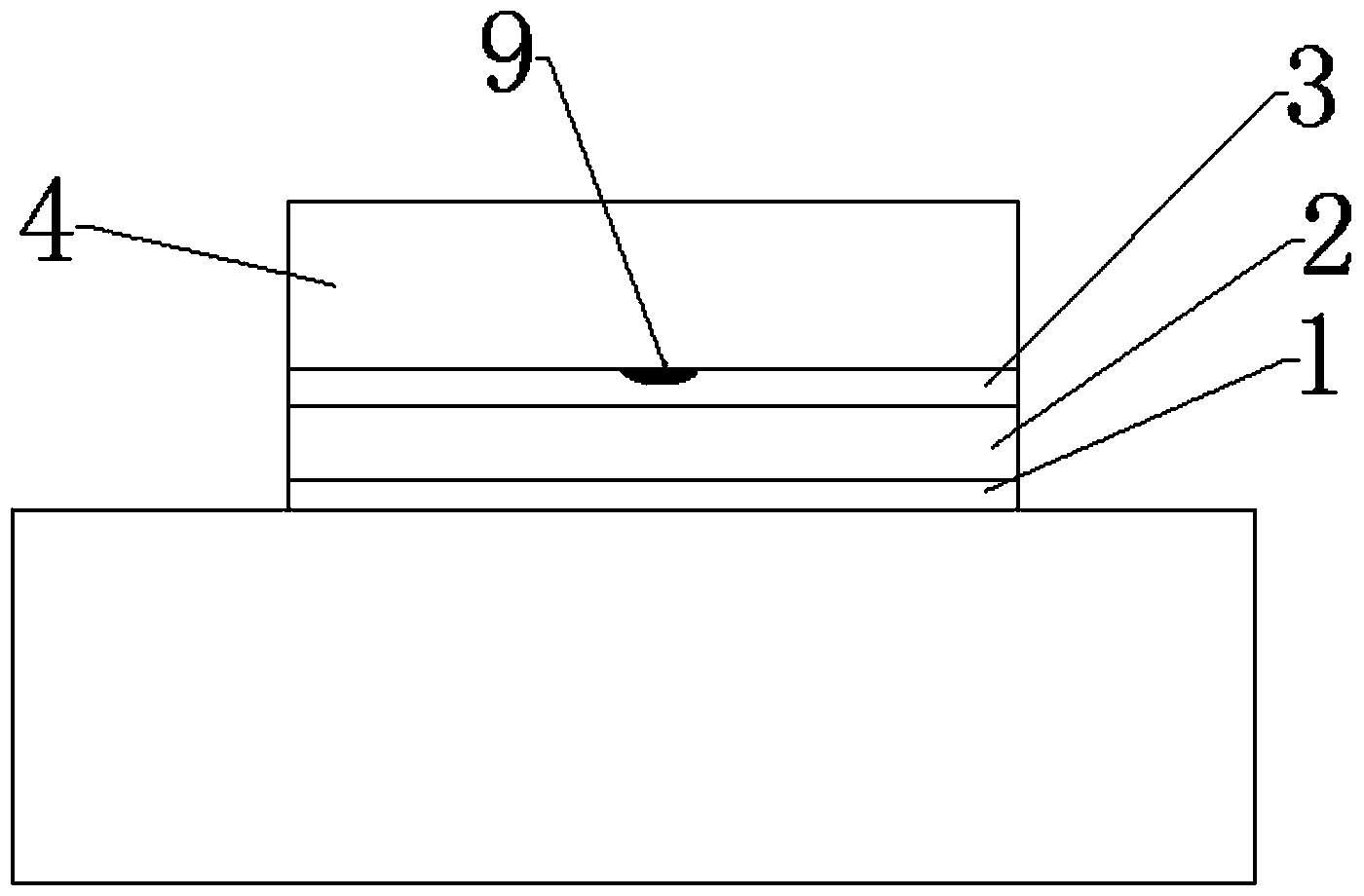

[0033] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention. The invention relates to a method for analyzing the failure of the original appearance of gate oxide layer defects. Firstly, several semiconductor structures to be tested are provided with a gate structure and a metal interconnection layer located above the gate structure, and the gate structure includes a gate oxide layer, Gate 4 and interconnection 6, preferably, the gate oxide layer can be an oxide layer or an ONO dielectric layer. In order to explain the present invention more clearly, the present embodiment takes an ONO (Oxide Nitride Oxide) dielectric layer as an example, namely The above gate oxide layer includes a first oxide layer 1 , a nitride layer 2 and a second oxide layer 3 in sequence from bottom to top.

[0034] A preset voltage is applied to each semiconductor structure to be test...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More