Super junction lateral double diffusion metal oxide semiconductor field effect transistor and manufacturing method thereof

An oxide semiconductor and lateral double-diffusion technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing the lateral breakdown voltage of SJ-LDMOS, and achieve high lateral and vertical breakdown voltages, Effect of High Lateral Breakdown Voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

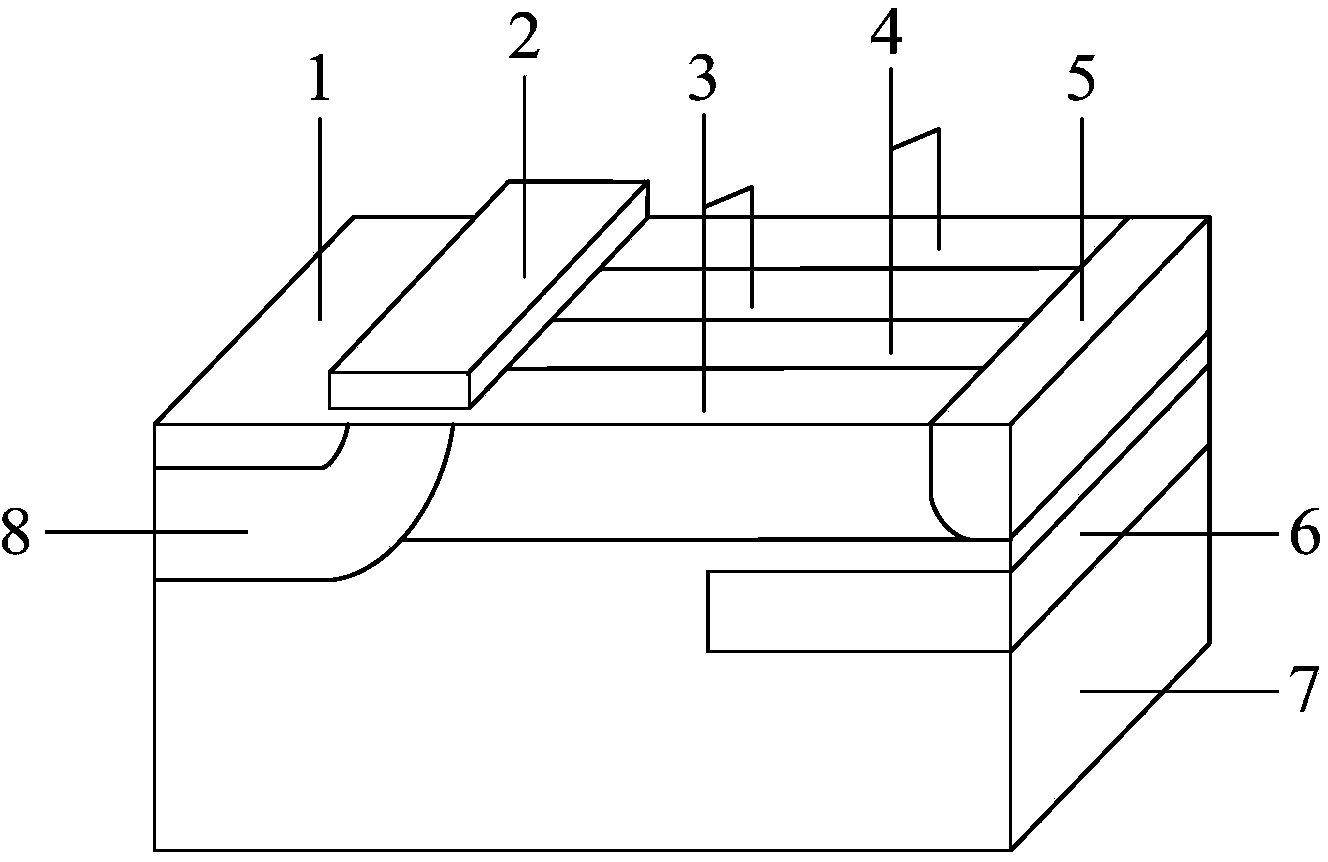

[0025] like figure 1 As shown, the present invention provides a super junction lateral double diffused metal oxide semiconductor field effect transistor, referred to as SJ-LDMOS, which includes a P-type semiconductor substrate 7 and an active region and a gate region 2 formed on the surface of the semiconductor substrate 7 . The active region includes an N-type source region 1, an N-type drain region 5, a P-type base region 8 and a lateral super junction structure. Wherein, the base region 8 serves as a channel of the MOS transistor, the source region 1 is formed in the base region 8 , and the source region 1 and the drain region 5 are located on both sides of the gate region 2 . The lateral superjunction structure includes N-type pillar regions 3 and P-type pillar regions 4 arranged alternately in the lateral direction. The heavily doped N-type pillar regions 3 and P-type pillar regions 4 reduce the on-resistance of SJ-LDMOS and minimize the conduction loss change.

[0026...

Embodiment 2

[0041] Based on the same inventive concept, the present invention also provides a method for fabricating the SJ-LDMOS in Embodiment 1, including the step of forming an active region and a gate region on the surface of a semiconductor substrate of the first conductivity type, the forming The steps for the source zone include:

[0042] forming a base region of a first conductivity type in the semiconductor substrate;

[0043]forming a source region of a second conductivity type in the base region;

[0044] forming a drain region of a second conductivity type in the semiconductor substrate, the source region and the drain region being located on both sides of the gate region;

[0045] Formed between the base region and the drain region, the lateral super junction structure includes N-type pillar regions and P-type pillar regions alternately arranged laterally.

[0046] The step of forming the active region also includes:

[0047] A buried region of the second conductivity type...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More