Composite type ultra-thin non-core substrate and manufacturing method thereof

A coreless substrate, composite technology, used in multilayer circuit manufacturing, semiconductor/solid-state device manufacturing, printed circuit components, etc., can solve the inner layer pattern difficulty of ultra-thin/coreless substrates, Low yield and other problems, to achieve the effect of increasing strength, reducing warpage deformation, and improving strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with specific drawings.

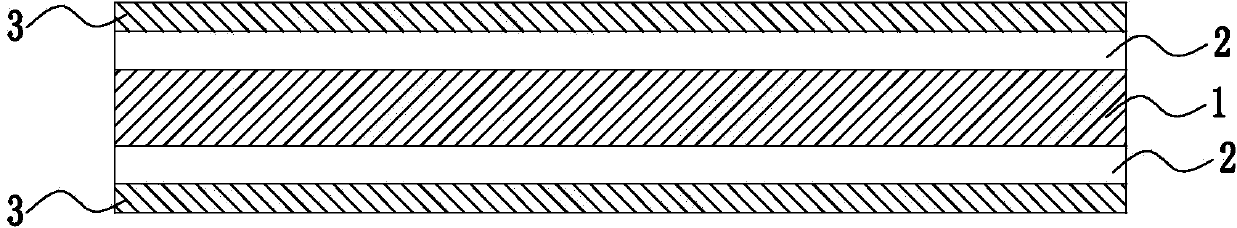

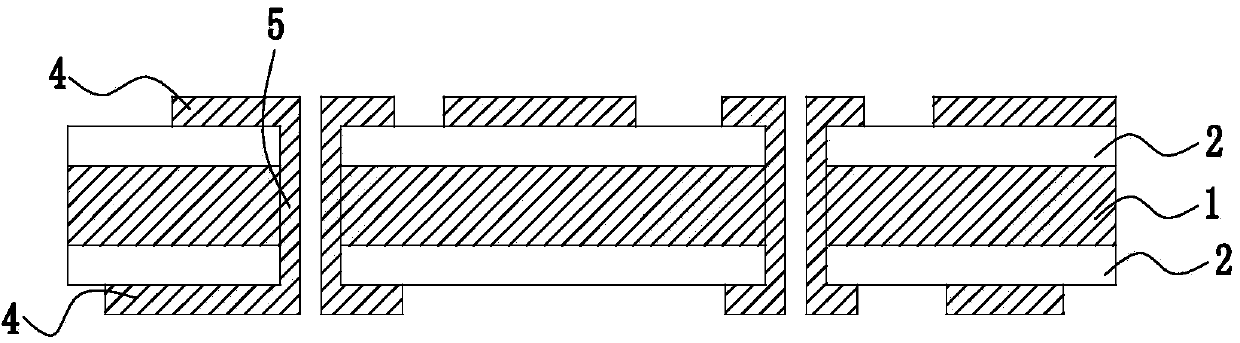

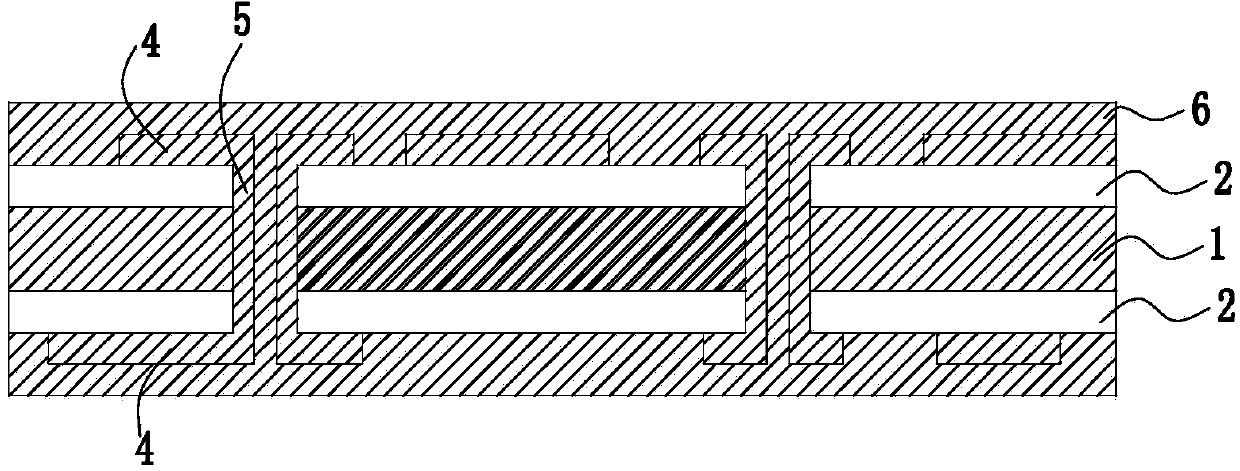

[0022] Such as Figure 5 As shown: the composite ultra-thin coreless substrate includes a PI core board. The PI core board is composed of a PI substrate 1 and copper foil 3 located on the front and back of the PI substrate 1. The copper foil 3 is bonded to the PI substrate through an adhesive layer 2 respectively. On the front and back of 1, the copper foil 3 is etched to form a core layer pattern 4; a PTH hole (metallized hole, PLATING Through Hole) 5 is set on the PI core board, and the core layer pattern 4 on the front and back of the PI core board passes through the PTH hole 5. Connection; one or more layers of PP dielectric layer 6 are respectively laminated on the front and back of the PI core board, and the PP dielectric layer 6 has an outer layer circuit pattern, and the outer layer circuit pattern is connected to the copper foil 3 .

[0023] The method for preparing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More