Lead frame structure with staggered pins and semiconductor device manufacturing method

A lead frame and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as difficulty in parallel online testing, waste of lead frame materials, and impact on work efficiency. The effect of parallel electrical performance test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

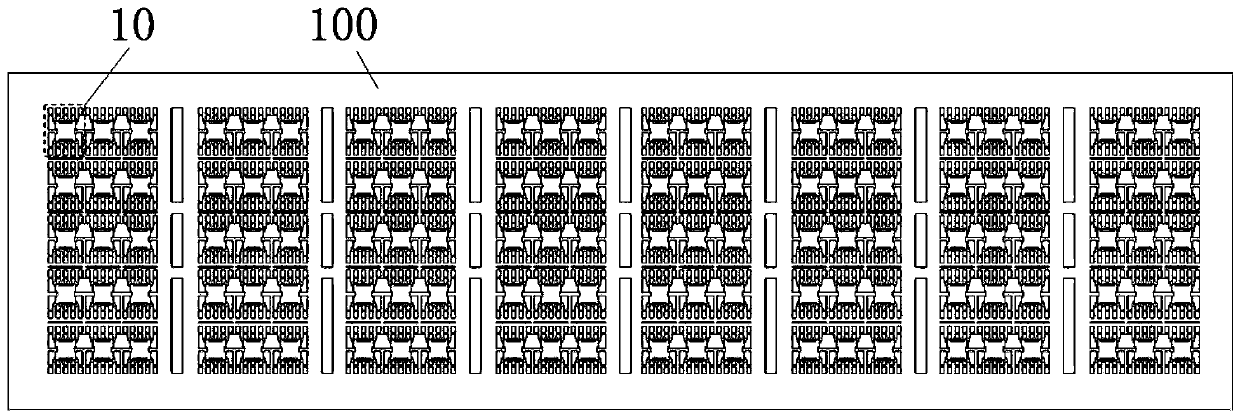

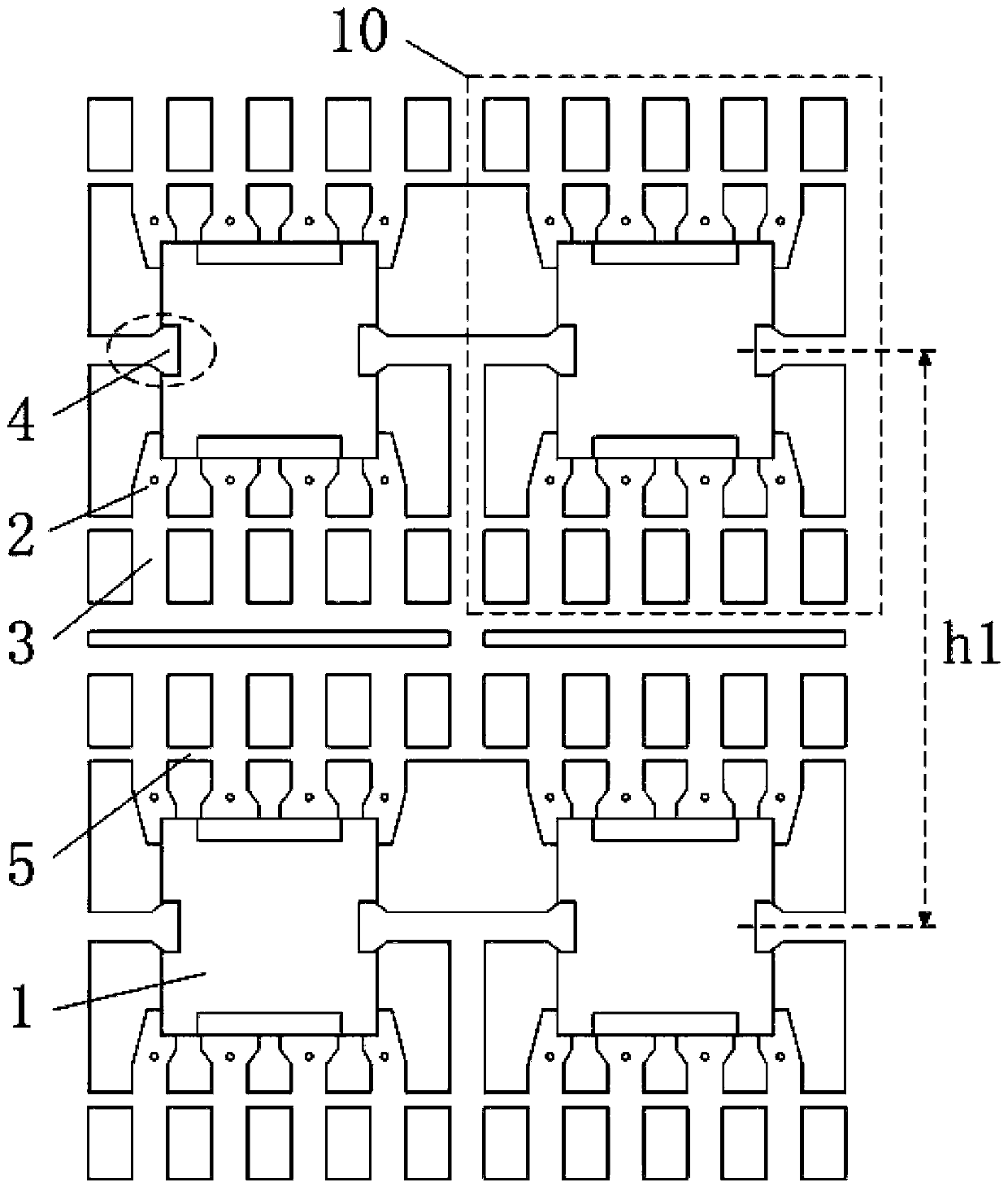

[0065] Figure 4 According to a specific embodiment of the present invention, a partial structural schematic diagram of the base material of the lead frame adopting the staggered pins of the present invention is shown. Such as Figure 4 As shown, the lead frame structure with staggered pins of the present invention is formed on a substrate 100 and includes: a plurality of chip units 20 arranged in a matrix. Twelve chip units 20 are arranged in each column, but not limited thereto. Compared with the 5x3x8 array lead frame in the prior art, in order to minimize the width of the monolithic frame, the present invention introduces the staggered pin form into the frame design.

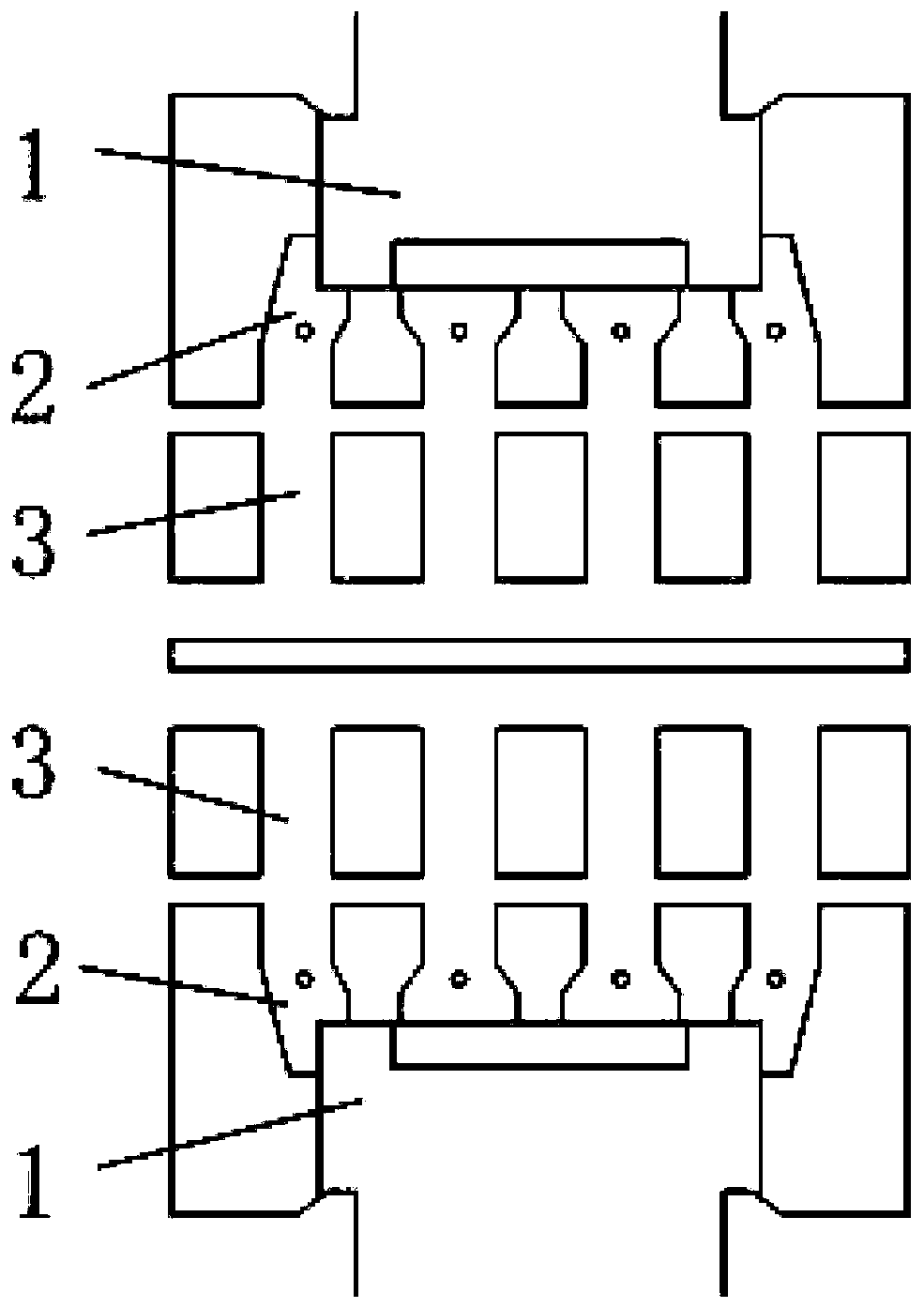

[0066] Figure 5 A schematic diagram showing a lead frame structure with staggered pins according to a specific embodiment of the present invention. Such as Figure 5As shown, each chip unit 20 includes at least one chip stage 11 , a plurality of outer pins 13 are drawn out from the periphery of the chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More